新一代高級綜合 (HLS) 工具目前用于兩個主要目的。首先是出于性能原因在硬件中實現軟件。第二個是出于生產力、重用、架構探索和更好的結果質量 (QoR) 的原因,將半導體設計推向更高的抽象級別。

同時,一種新的寄存器傳輸級 (RTL) 綜合方法稱為芯片綜合,它比以往任何時候都更容易實現對最終性能的快速準確評估,而無需創建完整的物理實現。結合這兩種技術,設計人員可以快速改變設計參數,獲得正確的性能數字,并在面積、性能和功耗方面達到最佳組合的設計。

更大的馬力,更好的抽象

各類嵌入式軟件,尤其是高清視頻處理等具有高吞吐量要求的軟件,經常會遇到性能問題。雖然可以使用一些軟件方法來提高性能,但當性能下降幾個數量級時,唯一可行的方法是更改??運行軟件的底層計算結構,這可能就像切換到多核處理器一樣簡單。然而,通常由于功率或成本的原因,改變計算結構并不是最優的。

HLS 是一種越來越有吸引力的方法,它采用軟件的一部分并在硬件中自動實現它,無論是在片上系統 (SoC) 上的原始門中,還是在 FPGA 中更好。AutoESL 的 AutoPilot 是一個將 C、C++ 或 SystemC 作為輸入并快速生成 RTL Verilog 或 VHDL 作為輸出的工具的示例。

與此同時,SoC 設計人員正在尋找將設計推向更高抽象層次的方法,用 C 或 SystemC 描述他們的算法,自動將其轉換為 RTL 代碼,并達到面積(成本)的正確權衡點,功率和性能。通過在更高級別上工作,設計人員可以顯著提高他們的生產力,并確保 QoR 接近或優于手動編碼結果。同樣,HLS 工具是執行從輸入到 RTL 代碼的優化轉換的鏈接。然后,傳統的 RTL 實現流程可以接管。

進入評估

說 HLS 使硬件編譯像軟件的 C 語言編譯一樣簡單可能有些夸張,但它確實使軟件到硬件的轉換變得簡單,尤其是與手動創建復雜的 RTL 實現相比。硬件編譯比軟件編譯更復雜的一個原因是 HLS 工具需要考慮一組更豐富的權衡。

例如,數據路徑可以簡單地實現、流水線化或復制。這些選項中的每一個都具有不同的性能、面積和功率特性,其變化因子高達 1,000。可以為 HLS 工具提供指令,以將實現導向設計人員想要的最佳位置。但是有一個問題:鑒于 HLS 的輸出是 RTL 代碼,設計人員如何快速確定特定候選實現的面積、功耗和性能?

缺少的環節是難以評估這些特征并獲得有關任何問題的快速反饋。雖然 HLS 工具提供了合理但相當粗略的估計,但通常需要更高的準確性。但是,用于將 RTL 代碼縮減為實現的傳統工具的性能與 HLS 工具的性能之間存在不匹配。

盡管 HLS 運行速度極快(大約一個小時左右),但減少 RTL 實現以實現準確的性能可能需要半天的綜合時間,然后是一天半的物理設計。這幾乎不是 HLS 用戶想要的快速反饋循環,因為它浪費了每天迭代五到六次的潛力,并將其最小化為每周幾次。這些較新的 HLS 工具的功能與語言無關,可以同時優化時序、面積和性能,從而生成高度可實現的 RTL 代碼,但被下游 RTL 綜合邊緣化。

塊和芯片

另一個細微差別是,塊的詳細性能不僅取決于塊本身,還取決于它周圍的其他塊。有時,從高層綜合的整個設計包括傳統模塊、第三方 IP 模塊和在 RTL 級別手工設計的模塊。當這些塊一起實現時,任何特定塊的性能都與共享某些相同物理資源的其他塊的性能相互關聯。

對于傳統的 RTL 綜合,設計人員面臨著一個沒有吸引力的選擇:快速但粗略的反饋或準確但極慢的反饋。所需要的是一種提供快速和準確反饋的方法。Oasys Design Systems 的 RealTime Designer 等芯片綜合工具提供了這種功能組合。

芯片綜合通過直接將 RTL 代碼簡化為布局元素來運行,因此與傳統綜合相比具有兩大優勢:布局和布線。這個過程很快,而且時間和尺寸數據與最終實現設計時最終獲得的數據有很好的相關性。HLS 和芯片綜合的結合使獲取大量 C 代碼并快速獲得性能和面積的出色估計成為可能。這使設計人員可以更有效地專注于最合適的實施位置。此外,由于芯片合成可以快速處理巨大的塊,它可以合成正在設計的塊以及影響性能的周圍塊。

區別很明顯

芯片合成的工作方式與傳統合成不同。一旦 RTL 代碼被解析,它就會被分割(基于連通性)成更小的段,最終將被簡化為門。每個分區都足夠小,不會包含任何長線,這會導致時序的高度可變性,并且足夠大,可以包含具有潛在不同區域/時間權衡的實現。每個分區都獨立于其他分區。當然,需要所有其他分區的時序編號才能對整個芯片進行計時,但并不需要同時要求每個分區的詳細內部結構。因為不再需要在門級同時查看整個芯片,所以減少了內存需求。

RTL 分區方法是芯片綜合能夠如此快速和有效的主要原因。通過在更高的層次上運行,這種方法一次智能地綜合和計時設計一個分區。然后,在滿足時序之前,它會重新綜合、替換(并更新全局路由)并重新劃分設計的各個部分,直到滿足約束條件。

使用最新的 HLS 和芯片合成技術在更高水平上工作會產生數量級的更好性能。對于 HLS 創建的典型設計規模,芯片綜合的運行時間與 HLS 大致相同。將這兩種創新技術結合使用意味著可以在一兩個小時內對設計進行迭代,從而每天可以考慮多次試驗實施。通過這種方法騰出的額外時間可以用于更緊湊的時間表或探索更豐富的替代空間。

審核編輯:郭婷

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603044 -

芯片

+關注

關注

455文章

50732瀏覽量

423254 -

soc

+關注

關注

38文章

4163瀏覽量

218171

發布評論請先 登錄

相關推薦

基于FPA的軟件工作量綜合評估研究與實踐

綜合布線中的配線架是什么

智能開關柜綜合測控系統是什么?

電磁頻譜數據綜合管理系統

綜合配線柜作用包括哪些方面

西門子推出Catapult AI NN軟件,加速神經網絡在ASIC和SoC上綜合

綜合配線架具有哪些功能

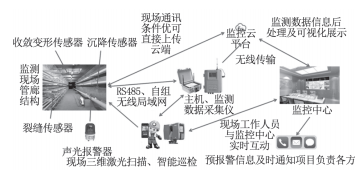

綜合管廊環境與設備監控系統

綜合管廊環境與設備監控系統保障城市綜合管廊安全運行

高級電工電機綜合保護器安裝位置差異解析

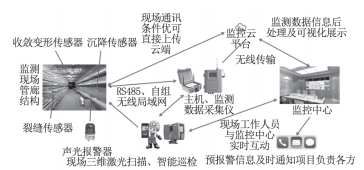

淺談邊緣計算在綜合管廊監控系統應用

芯片綜合和高級綜合:硬件中的軟件

芯片綜合和高級綜合:硬件中的軟件

評論