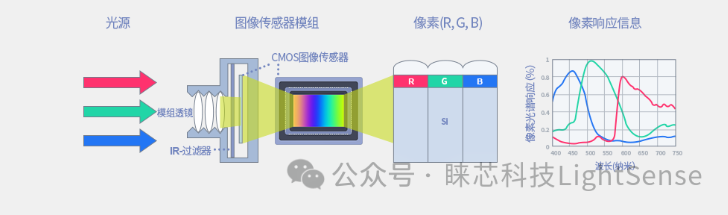

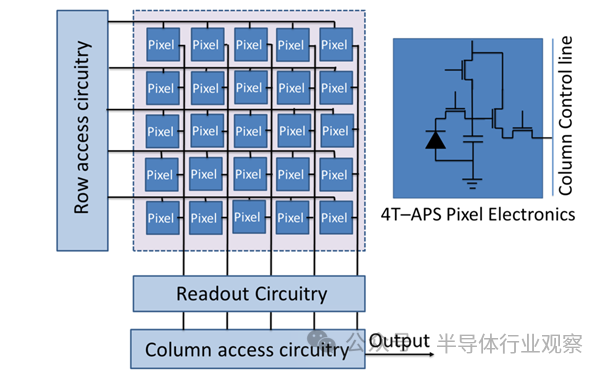

過去20多年的時間里,圖像傳感器的開發上已經迎來了不少創新,尤其是在移動市場的沖擊下。如今一億像素、自動對焦、HDR都已經不是新聞了,也正是因為有了智能手機這一商業平臺作為支撐,圖像傳感器開始像手機SoC一樣,不僅開始在芯片內加入各種AI/ML技術,也在沿用后者的結構和制造方案,比如芯片堆疊和互聯技術。

堆疊式圖像傳感器的發展

2012年,索尼推出了首款商用BSI堆疊式傳感器Exmor RS,讓傳統圖像傳感器的各項參數都獲得了升級,比如更小的像素尺寸、更高的像素密度,并通過更強大的信號處理與圖像重構技術,得到更好的圖像性能。

三層堆疊式圖像傳感器 / 索尼

圖像失真是卷簾快門傳感器中經常遇到的問題,這往往是由于像素讀取的時間滯后引起的。正因如此,三層堆疊的圖像傳感器開始出現,將像素層、邏輯層和DRAM疊加在一起。索尼在2015年發布了首款三層堆疊式的CMOS傳感器,其像素層、DRAM層和邏輯層分別用了90nm、30nm和40nm的工藝。

三星也在2017年跟進了這一設計,并隨后推出了ISOCELL 2L3這一圖像傳感器,堆疊了一個LPDDR4 DRAM芯片,實現了在1/120秒內以960FPS的速度捕捉慢動作畫面。

通過芯片堆疊的方法,圖像傳感器在一些高端應用上實現了不小的進步,原因之一就是更小的傳感器尺寸。再以索尼Exmor RS為例,一個1/4英寸800萬像素的CMOS圖像傳感器。在索尼發表的論文中,其研究人員指出指出堆疊方案讓芯片的大小減少了30%。

此外,復雜的邏輯層信號處理電路用到先進工藝,而像素層的像素陣列用的仍是各家打磨多年的成熟工藝,除了維持原有的像素優勢外,在信號處理電路中可以增加更多像自動對焦、AI這類的先進功能,實現真正的智能傳感器。

像素層再堆疊

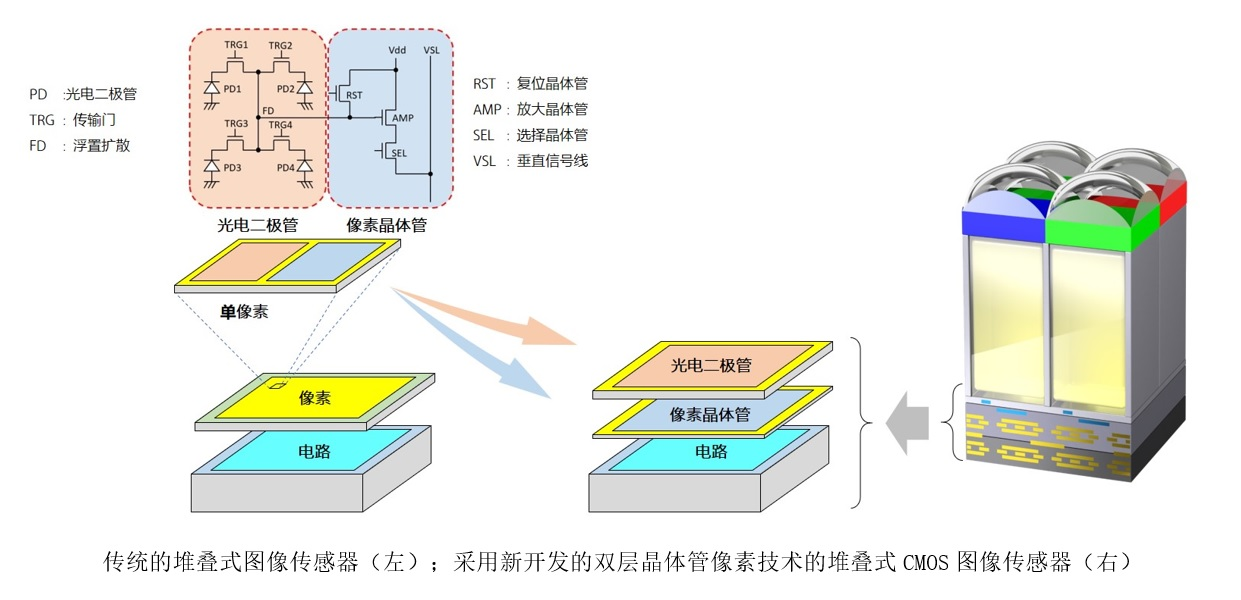

2021年底,索尼在IEEE國際電子設備會議上再次發布猛料,宣布成功開發出了全球首個雙層晶體管像素堆疊的CMOS圖像傳感器。傳統的堆疊式CMOS圖像傳感器光電二極管和像素晶體管在同一背照像素層,而索尼這一新技術將兩者分離為兩層垂直堆疊。

雙層晶體管像素堆疊式CMOS圖像傳感器技術 /索尼

根據索尼的說法,這一結構讓飽和信號量提升至原來的2倍左右,意味著單像素可以存儲更多的電子,因此傳感器的動態范圍顯著提升,并降低了噪點,哪怕是在更小的像素尺寸下,也能保持或提升像素原有的特性,從而提高成像性能。

芯片互聯技術的支撐

僅僅只是將兩個芯片堆疊在一起是不夠的,還得靠芯片互聯技術在芯片之間創造合適的電路互聯。而在圖像傳感器中,最常見的垂直互聯技術就是TSV和混合鍵合。

TSV,即硅穿孔技術采用的不是走線鍵合的方式,而是在芯片上鉆孔,通過每一層芯片,再加入導電介質形成通道,為芯片之間傳遞電信號的互聯技術。對于不需要提高TSV密度,傳輸大量數據,也不需要重新設計的圖像傳感器來說,后鉆孔的方法最為普遍。因為后鉆孔可以在完成的晶圓上進行,所以可以交由封裝廠。

銅混合鍵合 / 索尼

混合鍵合技術近來也開始慢慢普及,無論是豪威還是索尼都開始在新一代產品中使用這一技術,尤其是銅混合鍵合。以索尼的SenSWIR系列非可見光圖像傳感器為例,這類SWIR傳感器的像素尺寸大于一般的CMOS圖像傳感器,因此普遍分辨率不高,而銅混合鍵合縮小了像素間距,降低至只有5μm的像素大小,提供了SXGA(1280x1024)級別的像素分辨率。隨著圖像傳感器繼續向像素尺寸小型化、像素精細化的趨勢發展,這類混合鍵合技術也會越來越普及。

結語

芯片堆疊和互聯技術已經在圖像傳感器上得到了廣泛應用,支持到更小的像素尺寸、更大的像素陣列和支持ML/AI的智能圖像傳感器。但與此同時,圖像傳感器上用到的半導體工藝遠沒有達到極致,未來的堆疊芯片會擁有更高性能的邏輯電路,更高帶寬的芯片互聯,并根據成本在不同的工藝節點上進行優化。

-

傳感器

+關注

關注

2550文章

51035瀏覽量

753083 -

圖像傳感器

+關注

關注

68文章

1897瀏覽量

129527 -

移動芯片

+關注

關注

0文章

174瀏覽量

24211

發布評論請先 登錄

相關推薦

索尼圖像傳感器芯片有哪些

圖像傳感器芯片的發展趨勢是什么?

圖像傳感器的參數有哪些

圖像傳感器的探測能力與哪些因素有關

圖像傳感器的原理是什么?

圖像傳感器是依靠什么感光的

Melexis發布雙芯片堆疊式磁傳感器

雙芯片磁性位置傳感器中堆疊芯片和并排芯片實施方案之間的比較

簡單認識CMOS圖像傳感器

三星發布三款新型移動圖像傳感器

CMOS圖像傳感器堆棧式與單芯片的區別

跟著移動芯片走,圖像傳感器的堆疊與互聯

跟著移動芯片走,圖像傳感器的堆疊與互聯

評論