如果有一個(gè)最大的因素推動(dòng)了硬件仿真作為主要驗(yàn)證工具的發(fā)展,那就是片上系統(tǒng) (SoC) 設(shè)計(jì)。這些設(shè)計(jì)在尺寸和功能上不斷增長(zhǎng),需要更多的 IP 和接口。仿真技術(shù)還通過測(cè)試 SoC 設(shè)計(jì)的硬件屬性并同時(shí)驗(yàn)證其中的嵌入式軟件來滿足整個(gè) SoC 開發(fā)周期;仿真或 FPGA 原型設(shè)計(jì)工具都不能完全確保硬件/軟件協(xié)同驗(yàn)證。

然而,事情并不總是這樣。硬件仿真器在 1990 年代成為一種流行的驗(yàn)證工具,但當(dāng)時(shí)它們是難以使用的笨重設(shè)備,需要幾個(gè)月的時(shí)間來設(shè)置。而且,仿真是單用戶資源,每個(gè)座位要花費(fèi)數(shù)百萬美元,因此只有預(yù)算大的微處理器和圖形芯片公司才能買得起仿真器。

然后是可靠性差以及仿真器因運(yùn)行緩慢而陷入困境的問題。對(duì)仿真器進(jìn)行了徹底的改革,最終,SoC 設(shè)計(jì)運(yùn)動(dòng)的興起為仿真工具提供了必要的動(dòng)力,使它們更快、更便宜、更易于使用。

首先,編譯流程的改進(jìn)將仿真設(shè)置時(shí)間從數(shù)月縮短到數(shù)周,甚至數(shù)小時(shí)。接下來,新一代仿真引擎顯著加快了設(shè)計(jì)編譯周期、運(yùn)行速度和調(diào)試周期時(shí)間,從而提高了整體可見性。在仿真器架構(gòu)中,從昂貴的定制處理器轉(zhuǎn)向更靈活的 FPGA,這使得仿真工具更加實(shí)惠。

擁有模擬器的成本已經(jīng)降低,現(xiàn)在更多用戶可以購(gòu)買模擬器。此外,仿真器機(jī)箱現(xiàn)在可以安裝在數(shù)據(jù)中心的“過道機(jī)架”內(nèi)。此外,現(xiàn)代仿真器在編譯器周期中消耗的內(nèi)存更少,這進(jìn)一步降低了成本并縮短了編譯時(shí)間。

從 ICE 到協(xié)同仿真

硬件仿真發(fā)展的另一個(gè)重要部分是從傳統(tǒng)的在線仿真 (ICE) 環(huán)境逐漸轉(zhuǎn)變?yōu)榛谑聞?wù)的驗(yàn)證或加速等協(xié)同仿真技術(shù)。ICE 模式通常難以安裝和維護(hù),因?yàn)楸粶y(cè)設(shè)計(jì) (DUT) 環(huán)境映射在仿真器內(nèi)部,而仿真器又通過速度適配器與芯片所在的物理系統(tǒng)連接。

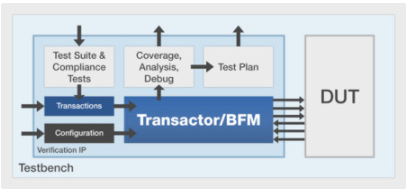

圖 1. 基于事務(wù)的仿真器為 SoC 設(shè)計(jì)驗(yàn)證提供更靈活的測(cè)試環(huán)境。

大型多時(shí)鐘 SoC 設(shè)計(jì)中功能數(shù)量的增加導(dǎo)致互連數(shù)量增加,這會(huì)降低仿真器速度并阻礙多個(gè)用戶的遠(yuǎn)程訪問。另一方面,以事務(wù)為中心的方法使用基于軟件的協(xié)議接口,稱為事務(wù)器。這些交易者,而不是整個(gè) DUT 設(shè)置,被映射到仿真器內(nèi)部,這不可避免地提高了驗(yàn)證速度。

這允許驗(yàn)證工程師和軟件開發(fā)人員從多個(gè)位置同時(shí)訪問仿真系統(tǒng)。此外,基于事務(wù)的驗(yàn)證或加速可以用更少的代碼行創(chuàng)建更高抽象級(jí)別的測(cè)試平臺(tái),從而對(duì)抗傳統(tǒng) ICE 環(huán)境的不可預(yù)測(cè)性。這些測(cè)試臺(tái)的執(zhí)行速度比傳統(tǒng)的 RTL 臺(tái)更快。

然而,值得注意的是,在某些應(yīng)用程序中仍然需要擁有硬件接口的 ICE 環(huán)境。因此,有多種仿真工具,例如 Mentor 的 Veloce 仿真平臺(tái),它提供了 ICE 和協(xié)同仿真方法的組合。

審核編輯:郭

-

soc

+關(guān)注

關(guān)注

38文章

4173瀏覽量

218423 -

仿真器

+關(guān)注

關(guān)注

14文章

1018瀏覽量

83790 -

模擬器

+關(guān)注

關(guān)注

2文章

877瀏覽量

43257

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

嵌入式工程師常用的開發(fā)工具有哪些?

嵌入式系統(tǒng)開發(fā)與硬件的關(guān)系 嵌入式系統(tǒng)開發(fā)常見問題解決

一文了解嵌入式軟件開發(fā)的對(duì)象

嵌入式開發(fā)常用軟件有哪些?

嵌入式軟件開發(fā)與AI整合

嵌入式開發(fā)前景怎么樣?

嵌入式系統(tǒng)怎么學(xué)?

嵌入式軟件工程師和硬件工程師的區(qū)別?

什么是嵌入式SoC

AMD Vitis? Embedded嵌入式軟件開發(fā)套件的功能和特性概述

fpga與嵌入式的區(qū)別 嵌入式和fpga開發(fā)有什么關(guān)系

嵌入式軟件設(shè)計(jì)的原則分享

嵌入式軟件開發(fā)應(yīng)該掌握哪些知識(shí)?

嵌入式軟件開發(fā)和軟件開發(fā)的區(qū)別

基于功能安全的汽車嵌入式軟件單元驗(yàn)證技術(shù)研究

仿真技術(shù)嵌入式軟件滿足整個(gè)SoC開發(fā)周期

仿真技術(shù)嵌入式軟件滿足整個(gè)SoC開發(fā)周期

評(píng)論