存儲器數(shù)據(jù)的穩(wěn)定可靠是MCU安全運行的基礎(chǔ),但環(huán)境因素和存儲器本身的物理特性都可能造成存儲器數(shù)據(jù)異常,本文將詳細(xì)介紹RAM&ROM常用安全機制。

存儲器(ROM,RAM)數(shù)據(jù)的安全可靠是MCU穩(wěn)定運行的基礎(chǔ),在汽車功能安全設(shè)計中,存儲器相關(guān)的安全機制也是系統(tǒng)基本保障的重點之一。通常,不同的汽車芯片都有自己的存儲器校驗機制以及相應(yīng)的處理手段來保證功能的正常運行。下面會對常見的處理機制進(jìn)行一些介紹。

RAM的校驗糾錯機制

RAM的校驗機制相對ROM的校驗機制較少,校驗機制基本都屬于MCU本身的特性,通過內(nèi)部硬件實現(xiàn),對于用戶來說是透明的。而一般用戶使用時也不會主動的對RAM進(jìn)行校驗。1. Parity BitParity Bit(奇偶校驗位)是一種數(shù)據(jù)校驗機制,常用與判斷數(shù)據(jù)在存儲過程中是否發(fā)生了比特位錯誤。

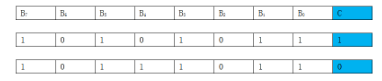

圖1 奇偶校驗?zāi)J娇梢钥吹綀D1,帶有Parity Bit的內(nèi)存在每一個字節(jié)(B7~B0)外又額外增加了一個校驗位(C)用于對錯誤進(jìn)行校驗。Parity Bit有著計算簡單的優(yōu)點,只需要對前面字節(jié)的位進(jìn)行異或操作:

C = B7^ B6^ B5^ B4^ B3^ B2^ B1^ B0Parity Bit在ECC技術(shù)之前,是RAM中應(yīng)用最多的錯誤檢查技術(shù),當(dāng)然,現(xiàn)在只有在已經(jīng)很少有CPU用到,因為每1 Byte的數(shù)據(jù)都需要1 bit的校驗位,對于MCU本就很緊張的RAM顯然不合適。另外Parity Bit只具備檢錯能力,并不具備糾錯能力。2. ECC通過上面對Parity Bit的分析可以知道,通過在原來的數(shù)據(jù)1 byte基礎(chǔ)上增加1 bit,可以用來檢查當(dāng)前1 byte數(shù)據(jù)的正確性。如果數(shù)據(jù)為256 byte就需要256 bit的校驗位,而且出錯的數(shù)據(jù)無法糾正。由于上述的缺點,出現(xiàn)了一種新的存儲檢錯糾錯機制 – ECC。

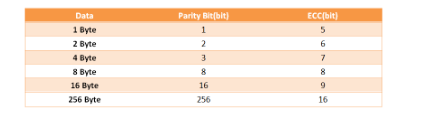

圖2 檢錯能力對比ECC(Error-Correcting Code),可以譯為檢錯糾錯碼。ECC的計算過程比Parity Bit的計算過程復(fù)雜一點,這里不進(jìn)行過多描述。僅針對ECC的兩個主要特點進(jìn)行說明:① ECC有極強的檢錯能力ECC的計算方式與Parity Bit不同,當(dāng)數(shù)據(jù)為1 Byte時,ECC需要5 bit校驗位對數(shù)據(jù)進(jìn)行校驗,之后數(shù)據(jù)每增加1倍,相應(yīng)的只需要增加1 bit的ECC 校驗位。可以看到圖2,ECC的檢錯能力相比Parity Bit有極大的提升。② ECC具有糾錯能力當(dāng)數(shù)據(jù)只有單bit 錯誤時,ECC能夠?qū)﹀e誤進(jìn)行修復(fù),但需要注意的是,當(dāng)數(shù)據(jù)中有超過 2 bit的錯誤同時產(chǎn)生時,ECC不一定能檢測出來,這一點Parity Bit也是一樣。

ROM的檢驗糾錯機制

與復(fù)雜的RAM空間相比,ROM空間的操作顯然簡單的多,因此,對于ROM的校驗使用者可以根據(jù)不同的需求,選擇不同的方式。

常用的有hash,CRC,對于大容量ROM,比如Nand Flash同樣也可以使用ECC的方式。基本上,只需要滿足ROM內(nèi)容和生成的校驗碼存在相對唯一的映射關(guān)系即可。

但是用戶自己實現(xiàn)的ROM校驗機制存在不少缺點:校驗失敗沒有靈活的處理措施,對ROM的校驗需要消耗額外MCU資源等。1. HSE隨著汽車產(chǎn)業(yè)的不斷升級,汽車智能化程度也在不斷加深,越來越多的汽車會通過OTA的方式實現(xiàn)客戶的個性化需求。但OTA在增加汽車升級和維護(hù)便利性的同時,也給數(shù)據(jù)的安全可靠性帶來了新的考驗。顯然,應(yīng)用開發(fā)者自己實現(xiàn)的ROM校驗并不足以滿足汽車應(yīng)用的安全需求,汽車應(yīng)用上,保證MCU程序的正確運行顯然需要一套更靈活,更完善的校驗機制,并且該校驗機制不僅需要保證數(shù)據(jù)的可靠性,還要保證檢驗機制本身的可靠性。下面會介紹NXP S32系列芯片是如何利用其HSE安全子系統(tǒng)來為ROM數(shù)據(jù)的可靠性提供支持,進(jìn)而保證汽車應(yīng)用的安全穩(wěn)定運行的。

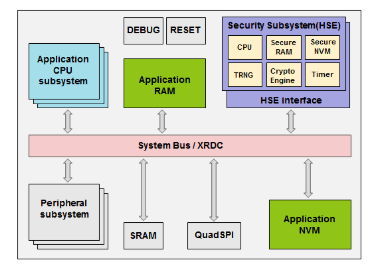

圖3 HSE框架HSE(Hardware Security Engine)全稱為硬件安全引擎,用于給對數(shù)據(jù)的可靠性和保密性有嚴(yán)格要求的應(yīng)用提供相應(yīng)的安全服務(wù)。其有以下特點:

獨立的內(nèi)核,固件,存儲空間;

可以為加密算法提供安全硬件加速;

支持固件升級。

可以看到圖3中,HSE模塊最基礎(chǔ)也最主要的部分是它的Crypto Engine(加密引擎),其可以通過硬件實現(xiàn)加解密/MAC生成校驗/簽名驗簽等功能。因為HSE全面完善的算法和密鑰管理機制,可以利用HSE模塊可以對用戶設(shè)定的存儲區(qū)域進(jìn)行校驗,并根據(jù)檢驗結(jié)果執(zhí)行不同的操作,正是HSE安全可靠,設(shè)置靈活的特性,構(gòu)成了MCU安全穩(wěn)定運行的基礎(chǔ)。當(dāng)然HSE除了能夠為MCU的OTA和安全啟動功能提供可靠保證外,HSE通過硬件加速特性和完善的加解密算法庫還能夠?qū)?a target="_blank">網(wǎng)絡(luò)協(xié)議進(jìn)行全面可靠的支持,可以實現(xiàn)TLS offload,IP offload,減少網(wǎng)絡(luò)協(xié)議的通信時延。

結(jié)語

上面提到了一些存儲器常見的校驗方式和NXP S32系列的HSE安全子系統(tǒng),當(dāng)然無論通過哪種方式,為了實現(xiàn)OTA和越來越多的網(wǎng)絡(luò)應(yīng)用功能,通過MCU實現(xiàn)更加安全可靠的數(shù)據(jù)存儲傳輸都是現(xiàn)在的趨勢。

-

mcu

+關(guān)注

關(guān)注

146文章

17123瀏覽量

350994 -

存儲器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163765 -

RAM

+關(guān)注

關(guān)注

8文章

1368瀏覽量

114643 -

數(shù)據(jù)存儲

+關(guān)注

關(guān)注

5文章

970瀏覽量

50894

發(fā)布評論請先 登錄

相關(guān)推薦

RAM、ROM常用安全機制

RAM、ROM常用安全機制

評論