雖然嵌入式市場中多核處理器的可用性并不是什么新鮮事,但今天的軟件工程師可以找到各種同質設備以及復雜的異構片上系統 (SoC) 作為他們設計的選項。這種高水平的多核集成提供了許多好處,包括更小、更低成本、更低功耗和更高性能的最終產品。

在工具和框架領域取得了進步,一些產品增加了編程范式,以幫助緩解圍繞這種復雜性的開發挑戰。然而,如果軟件架構師不能最大化多核處理器設備中每個計算元素的處理能力,那么高度集成的多核 SoC 所提供的價值就會被打折扣。

軟件工程師通過確定特定多核設備上的功能的標準方法來尋求完整的多核權利。雖然市場上有比較簡單的、通常是單核處理器的性能的標準基準,但它還沒有這些標準的基準或方法來比較復雜 SoC 的多核性能(或多核權利),這使得軟件架構師很難為他們的設計選擇最好的處理器。

基準測試挑戰

在處理器簡單且計算性能是唯一關注點的時代,對 CPU 性能進行基準測試相對容易。隨著處理器架構的發展,基準測試挑戰也隨之而來。根據 Merriam-Webster 的說法,基準的定義之一是“作為衡量或判斷他人的標準的東西”。換句話說,基準測試不是絕對的,而是相對的活動。當處理器架構的優勢和劣勢存在顯著差異時,其中存在根本挑戰:知道如何規范這些差異以制定既公平又準確的衡量標準。在實踐中,這個問題很少得到解決,最終用戶會留下難以以直接方式比較的措施。

迄今為止,傳統的基準測試已經很好地服務于嵌入式處理器市場,盡管其方式有限。這些基準測試易于理解且范圍有限,可在不考慮整體系統復雜性的情況下測量 CPU 的整數或浮點計算能力。有時,作為此類基準測試的測試工具執行的軟件內核是單一功能,可以通過使用內在指令或其他專門功能輕松優化,這會使收益難以在真正的客戶應用程序中轉化。因此,傳統的基準值為嵌入式處理工程師在選擇設備時提供了第一次通過的指標,并與潛在供應商合作。

然而,當今先進的 SoC 需要更全面的基準測試來揭示真正的性能和功能以及任何隱藏的瓶頸。由于單個芯片上集成了如此多的功能,因此對現實生活中的用例進行建模和測量變得越來越困難。因此,業界已經朝著針對特定應用領域(例如 Java 加速、Android 性能或 Web 瀏覽性能)的基準邁進。這種方法與綜合基準測試不同,適用于具有明確定義的應用程序段的處理器,并為用戶提供了對預期性能的相當準確的評估。

多核復雜性

對于部署在醫療成像、工業自動化、關鍵任務系統、通信基礎設施和高性能計算等各種應用中的新一代嵌入式多核處理器而言,問題并不那么簡單。架構復雜性與復雜的軟件實現相結合,使問題更加復雜。SoC 架構內所有處理元件和系統總線的內部連接會影響設備的計算性能,并使其更難以測量和評估。

通過多核實現,多個線程可以在不同的內核上并行執行,而不僅僅是在單個內核上執行多任務。并行路徑數量和調度可能性的增加使得建模應用程序行為和測量性能變得更加困難。

此外,多核系統引入了另一個維度:可擴展性,或者說隨著使用越來越多的內核,架構的可擴展性如何。可擴展性不僅在為當前應用程序選擇合適的架構方面很重要,而且在規劃未來增長或產品組合擴展方面也很重要。眾所周知的行業事實是,應用程序加速不會與內核數量成比例地線性增加,因為性能在某些時候會下降,并且在某些情況下實際上會隨著內核數量的增加而降低。這主要是由于內核數量增加所遇到的訪問瓶頸,以及額外的同步需求。加速還取決于軟件的分區方式以及它可以在多大程度上利用增加的并行性。

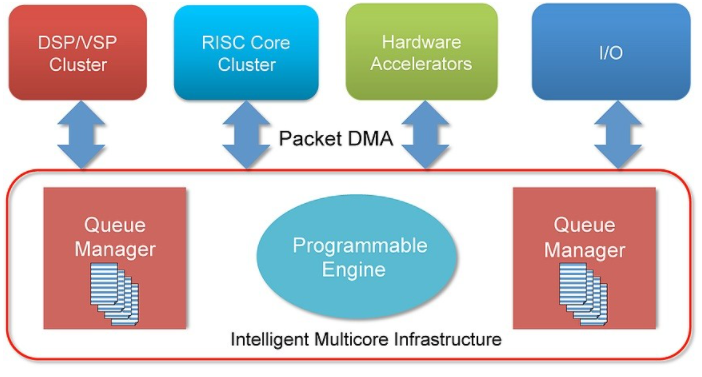

但是假設理想的軟件實現,關于多核設備架構仍有很多話要說(見圖 1)。高性能設備結合了多項創新技術,可有效地在系統中移動數據,從而使內核保持忙碌,而不會在訪問停頓上浪費時間。高帶寬芯片級互連和專用加速器創建了處理引擎孤島,這些引擎以最少的核心干預工作,并且不會造成內存瓶頸。類似地,具有內置直接內存訪問 (DMA) 的鏈式硬件隊列充當迷你裝配線,減輕中斷的核心并安排這些處理任務。

圖 1: Texas Instruments 的 KeyStone 多核 SoC 架構使用數據包 DMA 通信路徑在所有 SoC 處理元件和 I/O 上并行調度任務,從而提供可擴展性。

構建塊以獲得更好的基準

隨著芯片供應商采用截然不同的方法來提高多核效率,因此更需要設計可用于測量和比較可擴展性和性能的多核基準。這些基準測試應該易于移植,以便它們可以在裸機或常用操作系統上運行。由于增加了復雜性和復雜性,因此遵循模塊化方法非常重要,這樣可以使用基本構建塊創建復雜的工作負載。在最低級別,基準測試應該包含可以參數化以改變計算與內存訪問比率的處理內核。來自不同應用領域的代表性算法可用于創建其中一些內核。

內核也應該是可配置的,這樣它們就可以在不同級別的資源爭用下并行運行在不同的內核上。然后可以將這些內核的組合編織成復雜的工作負載拓撲,模擬各種特定于應用程序的場景。隨著行業和多核應用程序的發展,可以設計更多工作負載并將其添加到現有基準測試的全部內容中。這些基準的輸出應該是一個易于比較的分數,它反映了在特定數量的核心上完成給定工作負載所花費的時間。

毫無疑問,多核處理器支持新功能,并極大地改善了現有嵌入式產品的性能、功耗和成本。正如本期《嵌入式計算設計》中的文章所反映的,這個市場保持著興奮和前景。令人著迷的是,雖然業界利用了部分多核基準測試機制,但沒有主流的、市場接受的多核基準測試策略到位,尤其是在這樣一個注重成本的經濟時代。在做出最終選擇之前,工程師和管理人員經常面臨在多臺設備上實施自己耗時的基準測試工作的艱巨任務。

很難不問為什么在多核市場上有如此聰明和創新的工程師會出現這種情況。也許這個以多核為特色的特別版將呼吁采取行動,以建立一個可行的、市場接受的多核基準測試策略,這不僅有利于使用此類設備的嵌入式工程師,也有利于多核 SoC 制造商。

作者:Debbie Greenstreet,Atul Verma

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19259瀏覽量

229653 -

soc

+關注

關注

38文章

4161瀏覽量

218167 -

操作系統

+關注

關注

37文章

6801瀏覽量

123285

發布評論請先 登錄

相關推薦

CPU單核性能與多核性能的區別

多核CPU的優勢是什么

電壓測量儀表的主要性能有哪些?

針對特定內核使用PFlash,是否會影響多核應用程序的性能?

一文解析嵌入式多核異構方案,東勝物聯RK3588多核異構核心板系列一覽

求助,關于ESP32多核使用問題求解答

TC3x多核使用與TC2x多核使用相比是否有任何限制?

risc-v多核芯片在AI方面的應用

多核架構高性能電機控制芯片

兆芯開先KX-7000處理器現身Geekbench,多核性能接近8代i5

多核異構通信框架(RPMsg-Lite)

YY3568多核異構(Linux+RT-Thread)--啟動流程

對測量多核性能的追求

對測量多核性能的追求

評論