隨著最終產(chǎn)品功能的提高,對多核處理器提供的更高處理能力、更低成本和強大的功率性能的需求也在不斷增長。

多核的故事實際上是關(guān)于系統(tǒng)集成的。內(nèi)核數(shù)量的增加反映在外圍設(shè)備、總線結(jié)構(gòu)和多級存儲器集成度的提高上。一般來說,多核處理器根據(jù)其架構(gòu)分為兩類:同構(gòu)多核處理器和異構(gòu)多核處理器。

同質(zhì)多核處理器具有兩個或多個相同的可編程內(nèi)核,它們共享外圍設(shè)備和內(nèi)存。異構(gòu)處理器具有多個獨特的處理元素,每個元素都針對特定功能量身定制,并且每個內(nèi)核可能只能選擇性地訪問外圍設(shè)備和內(nèi)存。這兩種類型的多核處理器都產(chǎn)生了巨大的潛在性能提升。架構(gòu)師可以根據(jù)最終應用的需求定制設(shè)計,并在性能、靈活性和功耗之間取得平衡。

使用同構(gòu)或異構(gòu)多核系統(tǒng)的開發(fā)人員通常會面臨兩類問題:同步和時序以及理解性能。

多核設(shè)備中的每個處理元件都執(zhí)行設(shè)備功能的一部分。再加上改進的編碼、打包和集成實踐,同步運行、步進和暫停等傳統(tǒng)調(diào)試技術(shù)在多核系統(tǒng)中非常有效。然而,當線程交互時,經(jīng)常會出現(xiàn)與時間或同步相關(guān)的問題。

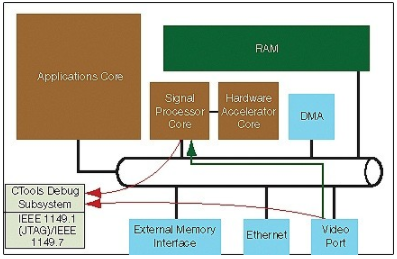

多核設(shè)備在處理元素之間總是存在依賴關(guān)系。很多時候,一個處理元素必須等待另一個處理元素的結(jié)果,如果它們不同步,兩個線程之間的切換將不正確或效率低下。但是,可能會導致更微妙的問題。例如,在面向幀的處理方案中,一個新的幀可能會因為處理沒有及時完成而丟失。雖然這可能不會導致應用程序崩潰,但它可能會降低應用程序處理結(jié)果的質(zhì)量。這些問題很難隔離,因為它們是內(nèi)核、總線結(jié)構(gòu)和共享外設(shè)相互作用的結(jié)果。深入了解處理元件和外設(shè)之間關(guān)系的芯片級工具是優(yōu)化和調(diào)試多核系統(tǒng)的關(guān)鍵(參見圖 1)。

圖 1:異構(gòu)多核系統(tǒng)監(jiān)控信號處理子系統(tǒng)的視頻流量。

在嵌入式系統(tǒng)中,停滯的處理元件不僅會降低性能,還會影響功耗。為了最大限度地提高性能并降低功耗,開發(fā)人員必須盡量減少每個處理元件在數(shù)據(jù)準備就緒時的等待時間。當空閑時,可以關(guān)閉處理元件。

元素級別的性能對于理解如何在多核設(shè)備的內(nèi)核之間劃分線程至關(guān)重要。在關(guān)鍵接口處測量的性能進一步幫助開發(fā)人員識別系統(tǒng)瓶頸。這將有助于確定是否可以采取更多措施來優(yōu)化內(nèi)核、總線結(jié)構(gòu)和外圍設(shè)備的使用。有了這些知識,降低功耗的機會就變得顯而易見了。

優(yōu)化多核設(shè)備將是未來開發(fā)人員面臨的最大挑戰(zhàn)之一。展示多核設(shè)備巨大處理潛力的能力需要深入了解處理元件和外圍設(shè)備之間的同步和時序,以及了解處理元件和關(guān)鍵接口的性能。新的多核處理器還需要強大的芯片級工具,讓開發(fā)人員能夠利用其潛在性能。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19404瀏覽量

230798 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164189 -

總線

+關(guān)注

關(guān)注

10文章

2900瀏覽量

88292

發(fā)布評論請先 登錄

相關(guān)推薦

生物醫(yī)藥行業(yè)設(shè)備資產(chǎn)管理解決方案

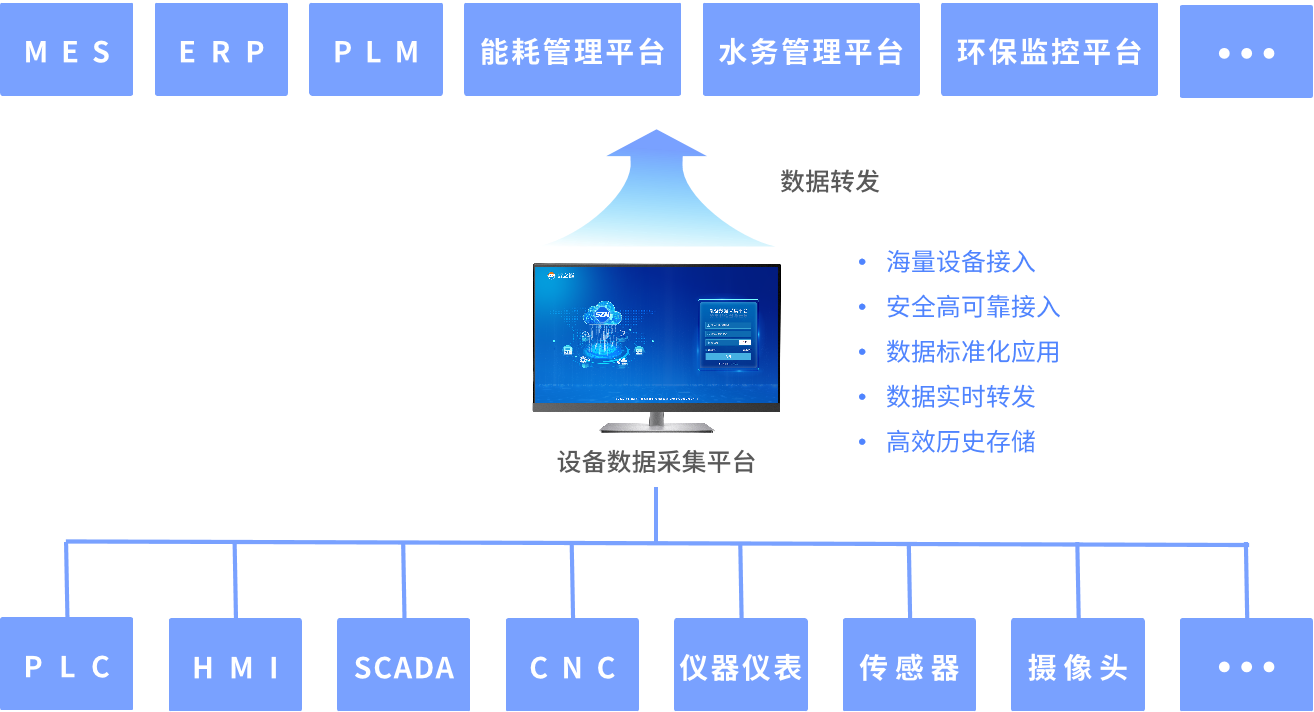

基于物聯(lián)網(wǎng)的CNC設(shè)備數(shù)據(jù)采集解決方案

解決方案丨EasyGo新能源系統(tǒng)實時仿真應用

Jacinto7 HS設(shè)備閃存解決方案

發(fā)酵設(shè)備遠程監(jiān)控運維系統(tǒng)解決方案

什么是開關(guān)設(shè)備溫升預測預警解決方案

使用最小封裝解決方案優(yōu)化離散邏輯電路設(shè)計的電路板空間

工廠配電設(shè)備運行監(jiān)控系統(tǒng)解決方案

提升25% | 自連光伏優(yōu)化解決方案

一文讀懂音頻解決方案專家

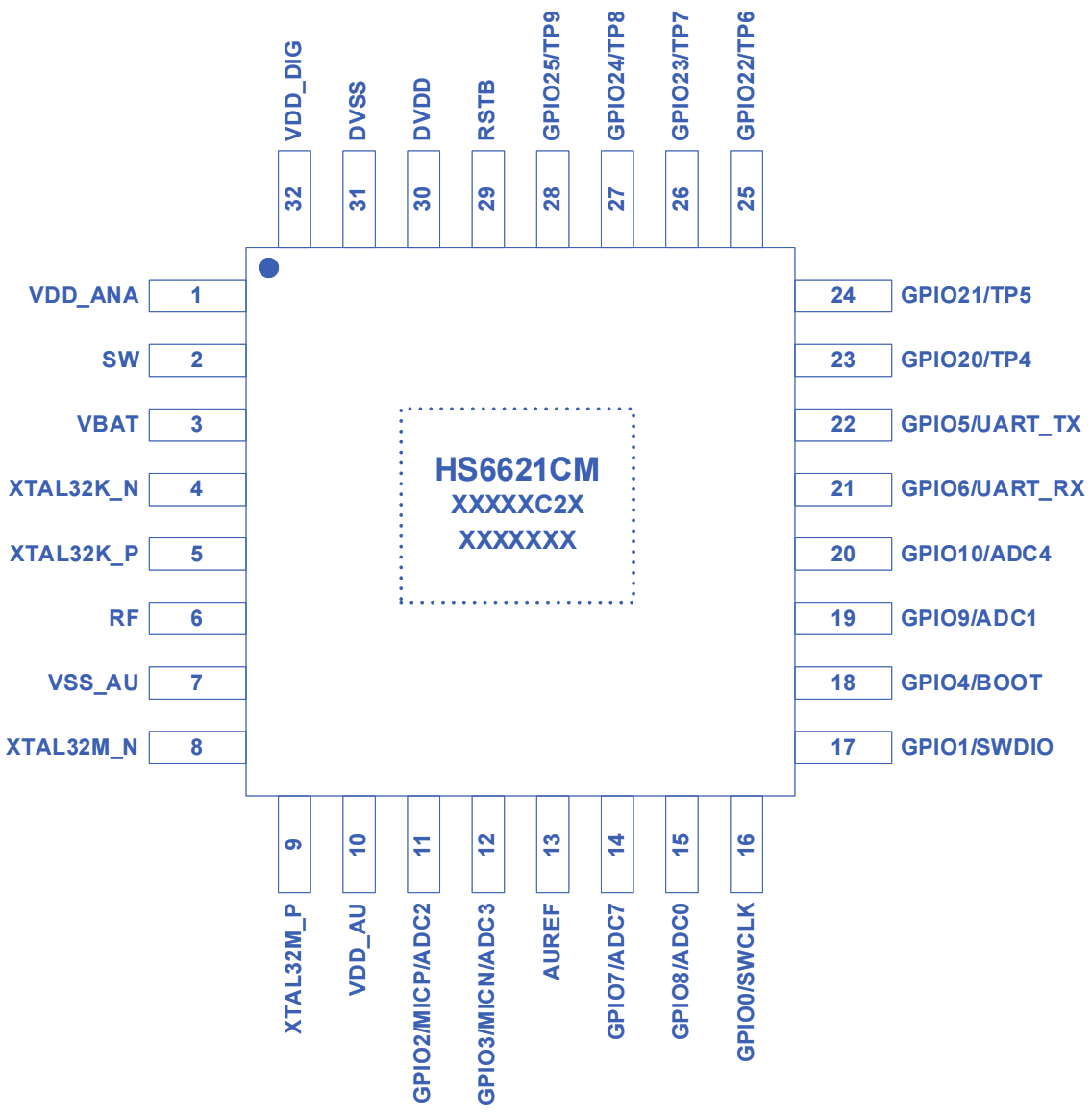

功耗優(yōu)化的片上系統(tǒng)(SoC)解決方案,引領(lǐng)低功耗藍牙與2.4GHz應用新潮流

risc-v多核芯片在AI方面的應用

礦場設(shè)備遠程監(jiān)控解決方案

優(yōu)化多核設(shè)備的解決方案

優(yōu)化多核設(shè)備的解決方案

評論