0.FPGA也能片上調試嗎?

FPGA與STM32等嵌入式開發最大的一個優點就是,可以在時序仿真階段驗證超過90%的功能,發現90%的問題。當所有的仿真沒問題了,才能進行最后一步:板級調試。如果仿真都不對,那就沒必要下載到芯片里了。

STM32等單片機,使用J-Link或ST-Link等調試器,可以進行在線調試,由于C代碼是順序執行的,我們可以插入斷點,讓程序停在我們需要的位置,或者是實時查看一些變量的數值,大大提高了我們Debug的速度,提高產品的開發效率。

對于FPGA來說,仿真畢竟是仿真,可以理解為理想條件,而最終我們的代碼是需要運行在實際的FPGA芯片硬件上的。

所以也會遇到仿真正常,實際下載到板子里不正常的情況。這種現象有兩種原因:1.程序有BUG,2.硬件有問題。比如實際程序中復位信號是低電平復位,而實際電路中設計的復位按鍵按下才是高電平,這樣按鍵未按下就會導致程序一直處于復位狀態。

當然,這只是一種最簡單的問題點,實際開發過程中,仿真與實際運行不匹配的情況還有很多。那么如何才能以最快的速度找到問題點呢?

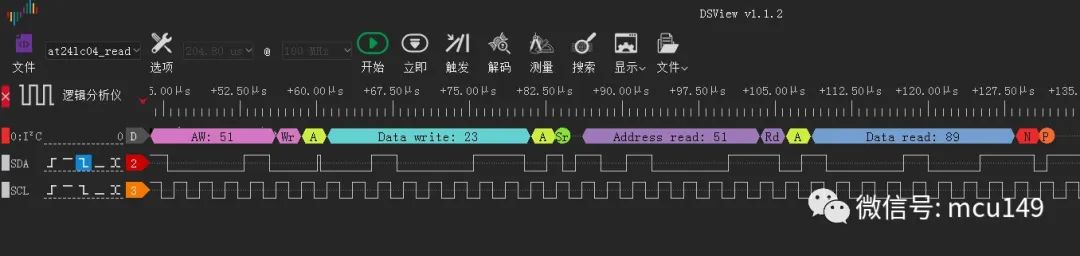

早期的FPGA調試方法通常使用邏輯分析儀,連接到FPGA芯片的外部管腳上,如果想查看內部信號,還需要把這些信號定義成Output引出到外部管腳進行了測量,如果是多位數據,這樣就會占用大量的管腳,但是此類工具有個優點就是支持多種協議解析,可以非常方便的查看協議的報文數據。

如果有一種工具能像單片機開發那樣,通過調試器JTAG接口實時獲取運行過程中寄存器的數值就好了。有需求就有市場,FPGA廠商也考慮到了開發者的這種需求,都在自家產品上加上了這個功能,那就是片上邏輯分析儀,就像在芯片內裝了一個邏輯分析儀ELA(Embedded Logic Analyzer),可以實時監測數據的變化,還可以設置觸發條件等!

FPGA領域幾大廠家提供嵌入式邏輯分析儀:

- Intel(原Altera)的SignalTap工具

- AMD(原Xilinx)的ChipScope工具

- Microchip(原Microsemi)的Identify工具

- Lattice的Reveal工具

這些工具都是嵌入式邏輯分析儀,大大提高了Debug速度。這類工具的原理通常是以預先設定的時鐘速率實時采樣FPGA的內部信號,并暫存于FPGA的內部RAM中,當滿足預設的觸發條件后,通過JTAG將存儲在片內RAM中的數據傳輸至PC上,PC接收到數據后,通過上位機把數據展現出來。

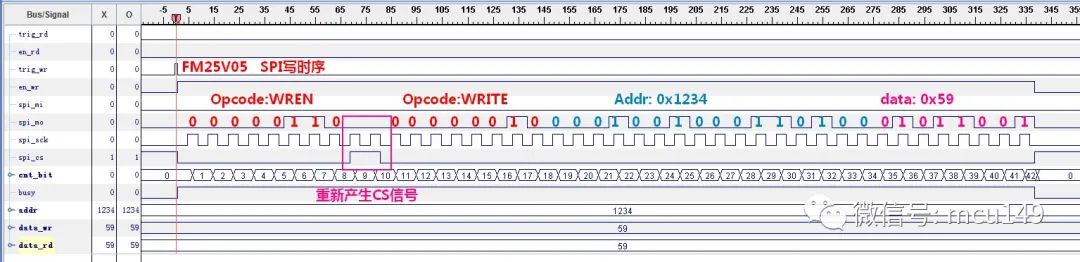

以下是使用ChipScope工具抓取的鐵電存儲器FM25V05的SPI寫時序:

FM25V05寫時序

從FPGA學習流程來看,當了解了流水燈、按鍵、UART等基本例程后,再學習I2C,SPI之前,就需要掌握片上邏輯分析儀的使用,非常有利于代碼的調試。

我個人使用過Xilinx和Microsemi的工具,還是挺好用的。

Microsemi的identify使用方法可以到CSDN文章查看:

https://blog.csdn.net/whik1194/article/details/107074187

本文主要介紹Xilinx ISE開發環境下ChipScope工具的使用。

1.Xilinx ChipScope簡介

Xilinx的FPGA片內邏輯分析儀被稱為ChipScope,通過插入IP核的方式實現,主要包括3大IP核。

- ICON

ICON(integrated controller),主要負責與JTAG口的通訊,最大支持連接15個Core,這里的Core可以是ILA或VIO。

- ILA

ILA(integrated logic analyzer),嵌入式邏輯分析儀,可以抓取內部的任何信號,通過設置觸發條件的方式,抓取一段時間的波形,時間長度取決于FPGA RAM資源大小。

- VIO

VIO(virtual input/output),即輸入輸出,可以實時監控FPGA內部信號,并提供驅動信號給FPGA模塊,類似于單片機調試中的變量值查看。

- ATC2

ATC2(Agilent trace core),是屬于特殊定制的調試IP核,需要配合新一代的Agilent邏輯分析儀一起使用,這個很少使用。

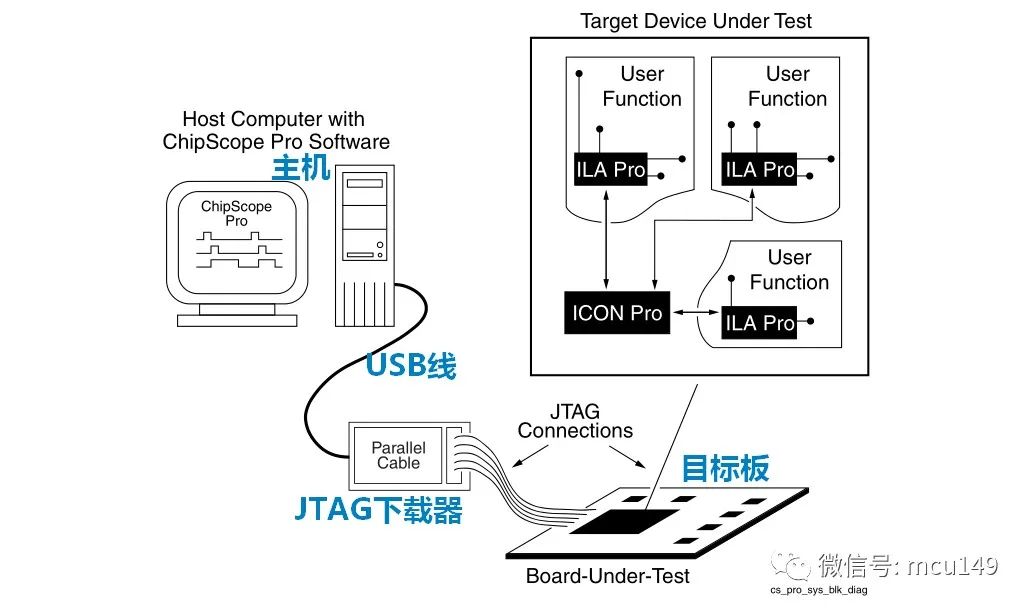

下面這張圖是來自Xilinx官方文檔:chipscope_pro_sw_cores_ug029.pdf的一張圖片,關于ChipScope官方的使用指南可以查看這篇文檔,介紹了ChipScope工具的整體框圖。

ChipScope系統框圖

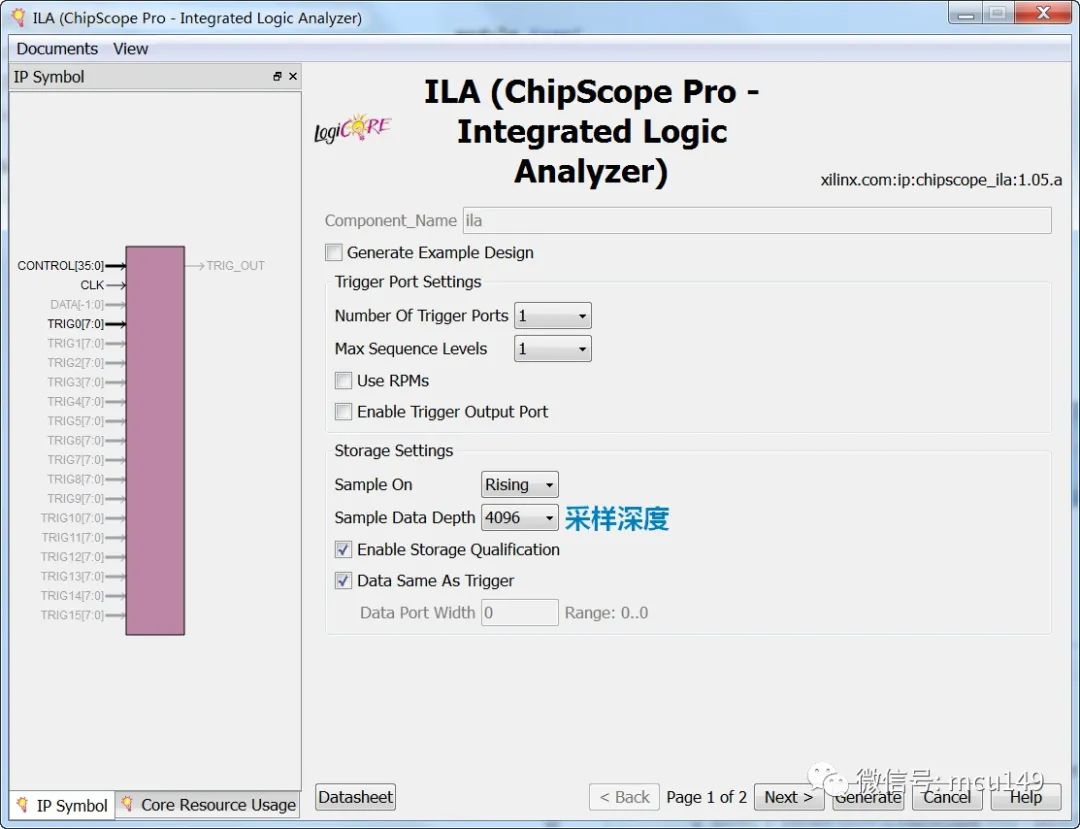

既然是邏輯分析儀,就要涉及到邏輯分析儀最重要的兩個參數:采樣頻率和采樣深度,ILA的采樣頻率取決于輸入時鐘信號的頻率,采樣深度取決于FPGA的RAM大小。

2.示例工程創建

下面以Xilinx Spartan-6 XC6SLX9為例,演示ChipScope的使用,ILA抓取cnt實時數據。VIO實現在上位機控制LED亮滅,或選擇閃爍頻率。led1通過VIO來選擇4檔閃爍頻率,led2通過VIO給的觸發信號上升沿進行翻轉,led3與VIO輸出高低保持一致。

首先創建一個基于XC6SLX9的ISE基本工程,并新建源文件。

以下代碼還未添加ChipScope:

moduletop( //Inputs inputclk,//50MHz inputrst_n, //Outputs outputregled1,//通過VIO來選擇4種閃爍頻率 outputregled2,//通過VIO來控制 outputled3//通過VIO來控制 ); wire[1:0]level;//來自VIO wiretrig;//來自VIO,按鍵產生高脈沖信號 wiretrig_rise=(trig_reg==2'b01); reg[1:0]trig_reg; reg[26:0]cnt;//在ILA中查看數據變化 always@(posedgeclk)begin if(!rst_n) trig_reg<='h0; else trig_reg<=?{trig_reg[0],?trig}; end always?@?(posedge?clk)?begin ????if(!rst_n)? ????????cnt?<=?'d0; else cnt<=?cnt?+?1; end always@(posedgeclk)begin if(!rst_n) led1<='d0; elsebegin //level來自VIO case(level) 0:led1<=?cnt[26]; ????????????1:??led1?<=?cnt[25]; ????????????2:??led1?<=?cnt[24]; ????????????3:??led1?<=?cnt[23]; ????????endcase ????end end always?@?(posedge?clk)?begin ????if(!rst_n) ????????led2?<=?0; ????else?if(trig_rise)??????//trig上升沿翻轉 ????????led2?<=?!led2; end endmodule

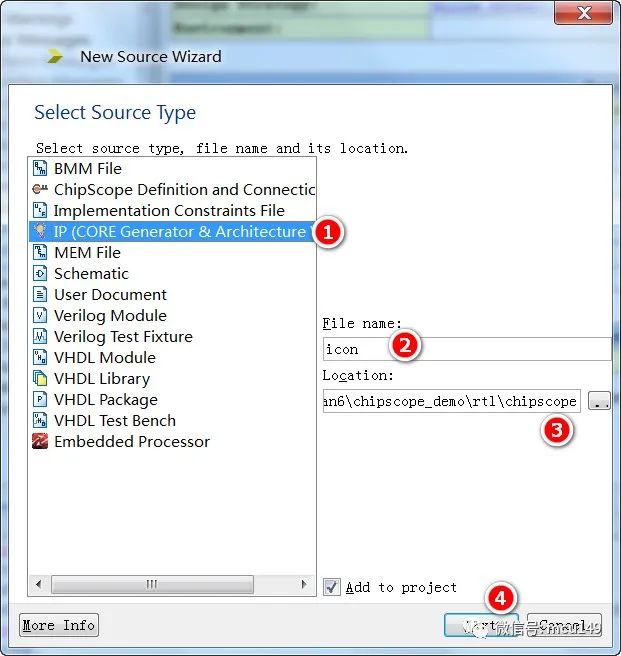

3.添加ChipScope ICON IP核

添加一個IP核源文件,保存在chipscope文件夾下。

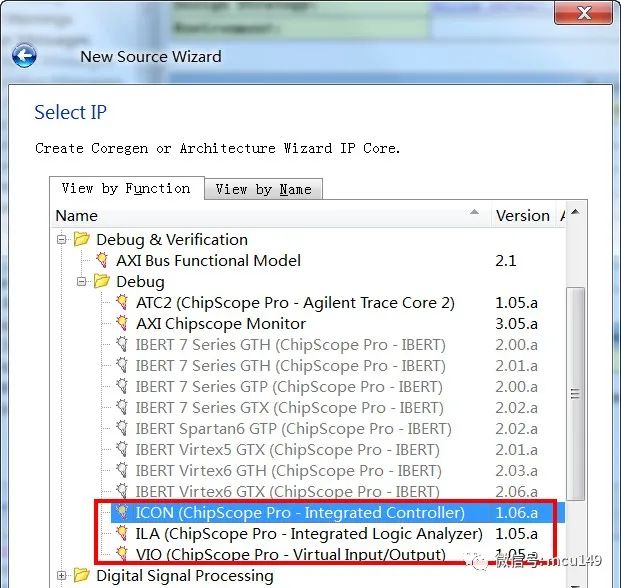

添加ICON

選擇ICON IP核,以下添加VIO和ILA核是一樣的操作。

選擇ICON

添加之后進入配置界面,因為我們連接了ILA和VIO兩個IP核,這里控制端口需要兩個:

配置端口

查看例化模板:

iconYourInstanceName( .CONTROL0(CONTROL0),//INOUTBUS[35:0] .CONTROL1(CONTROL1)//INOUTBUS[35:0] );

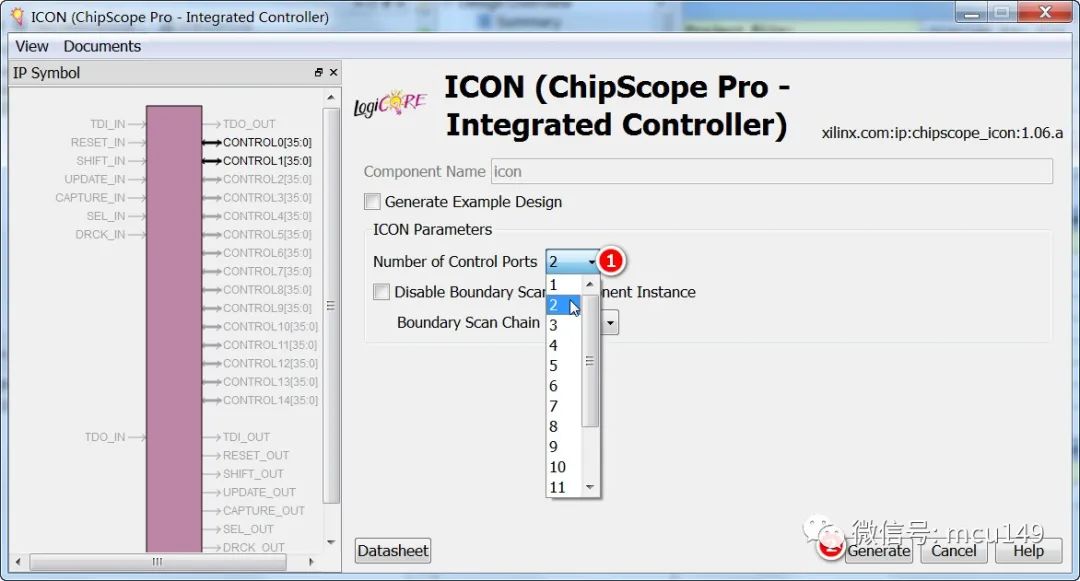

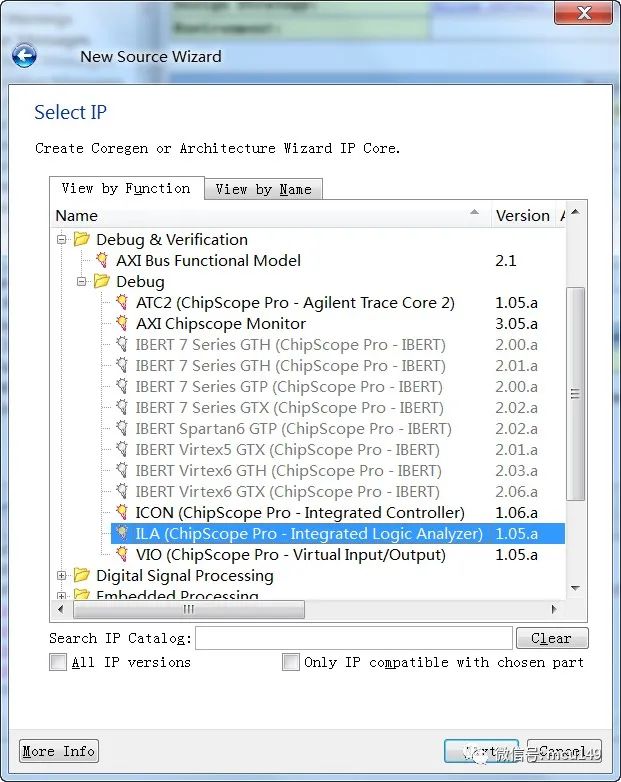

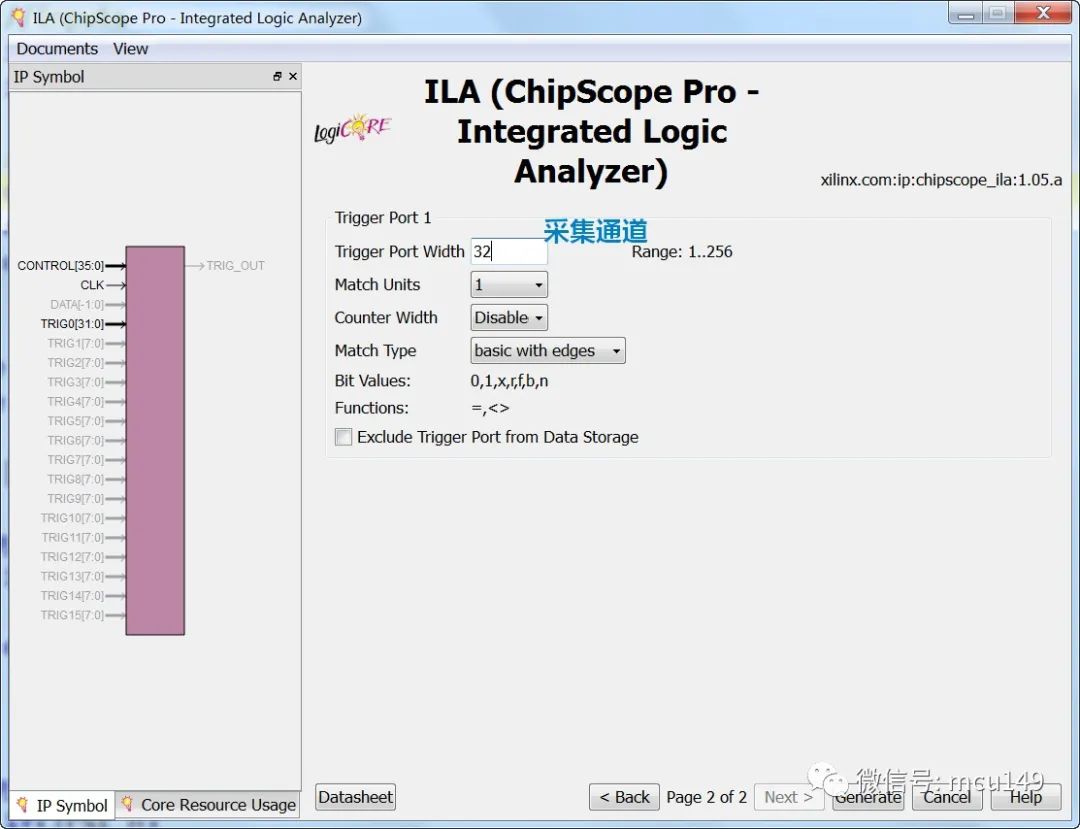

4.添加ChipScope ILA IP核

添加ILA

選擇采樣深度,數值越大,占用FPGA RAM資源越多,采樣時間越長。

設置采樣深度

選擇采集通道,這里選擇32個通道。

選擇觸發通道

等待生成完成,查看例化模板:

ilaYourInstanceName( .CONTROL(CONTROL),//INOUTBUS[35:0] .CLK(CLK),//IN .TRIG0(TRIG0)//INBUS[31:0] );

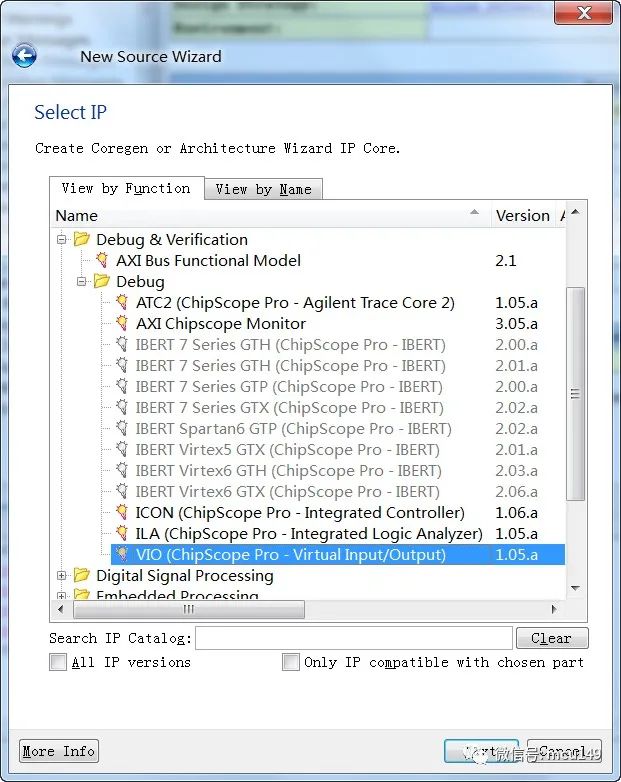

5.添加ChipScope VIO IP核

同樣的方式添加VIO核:

添加VIO

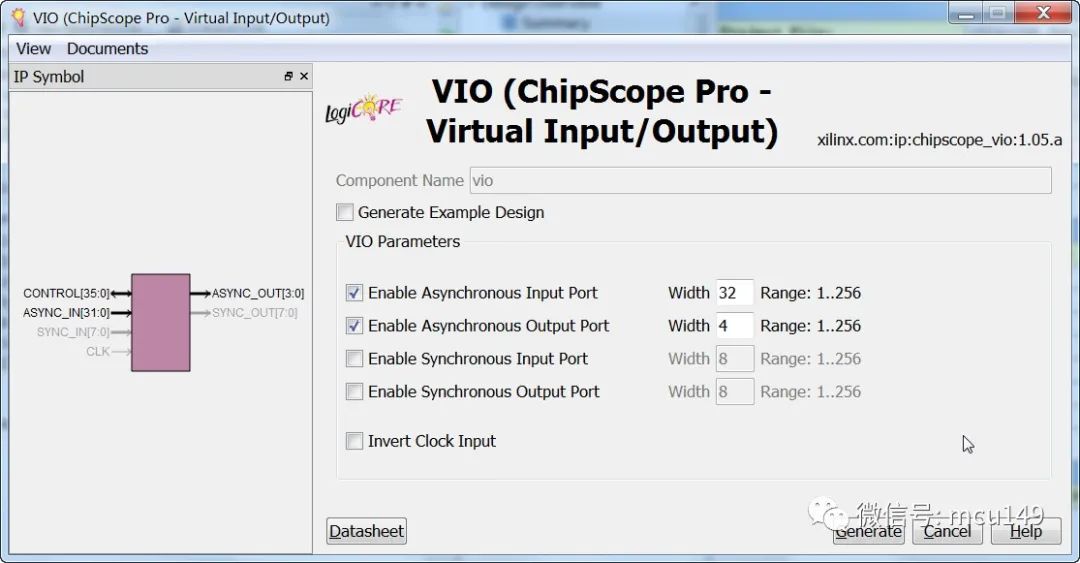

選擇32路輸入,用于監測cnt的值,4路輸出,用于控制LED。

配置輸入輸出通道

設置為異步輸入32位,輸出4位。

6.將ChipScope的3個IP核添加到頂層模塊

moduletop( //Inputs inputclk,//50MHz inputrst_n, //Outputs outputregled1,//通過VIO來選擇4種閃爍頻率 outputregled2,//通過VIO來控制 outputled3//通過VIO來控制 ); wire[1:0]level;//來自VIO wiretrig;//來自VIO,按鍵產生高脈沖信號 wiretrig_rise=(trig_reg==2'b01); reg[1:0]trig_reg; reg[26:0]cnt;//在ILA中查看數據變化 always@(posedgeclk)begin if(!rst_n) trig_reg<='h0; else trig_reg<=?{trig_reg[0],?trig}; end always?@?(posedge?clk)?begin ????if(!rst_n)? ????????cnt?<=?'d0; else cnt<=?cnt?+?1; end always@(posedgeclk)begin if(!rst_n) led1<='d0; elsebegin //level來自VIO case(level) 0:led1<=?cnt[26]; ????????????1:??led1?<=?cnt[25]; ????????????2:??led1?<=?cnt[24]; ????????????3:??led1?<=?cnt[23]; ????????endcase ????end end always?@?(posedge?clk)?begin ????if(!rst_n) ????????led2?<=?0; ????else?if(trig_rise)??????//trig上升沿翻轉 ????????led2?<=?!led2; end /*?Xilinx?ChipScope?Config?*/ wire?[35:0]?CONTROL0; wire?[35:0]?CONTROL1; wire?[31:0]?TRIG0; wire?[31:0]?ASYNC_IN; wire?[3:0]?ASYNC_OUT; assign?ASYNC_IN[26:0]?=?cnt[26:0]; assign?level?=?ASYNC_OUT[1:0]; assign?trig??=?ASYNC_OUT[2]; assign?led3??=?ASYNC_OUT[3]; assign?TRIG0[26:0]?=?cnt[26:0]; assign?TRIG0[28:27]?=?level[1:0]; assign?TRIG0[29]?=?led1; assign?TRIG0[30]?=?led2; assign?TRIG0[31]?=?led3; icon?icon_ut0( ????.CONTROL0(CONTROL0[35:0]), ????.CONTROL1(CONTROL1[35:0]) ); ila?ila_ut0( ????.CONTROL(CONTROL0[35:0]),? ????.CLK(clk),? ????.TRIG0(TRIG0[31:0]) ); vio?vio_ut0( ????.CONTROL(CONTROL1[35:0]), ????.ASYNC_IN(ASYNC_IN[31:0]), ????.ASYNC_OUT(ASYNC_OUT[3:0]) ); endmodule

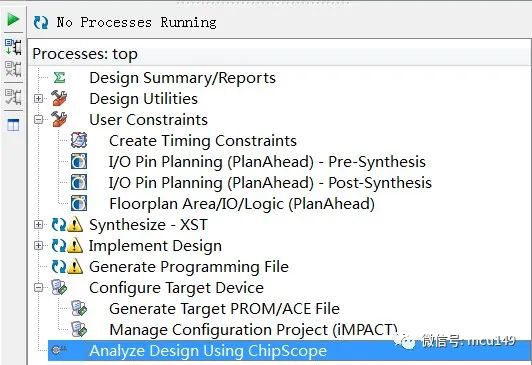

7.編譯下載

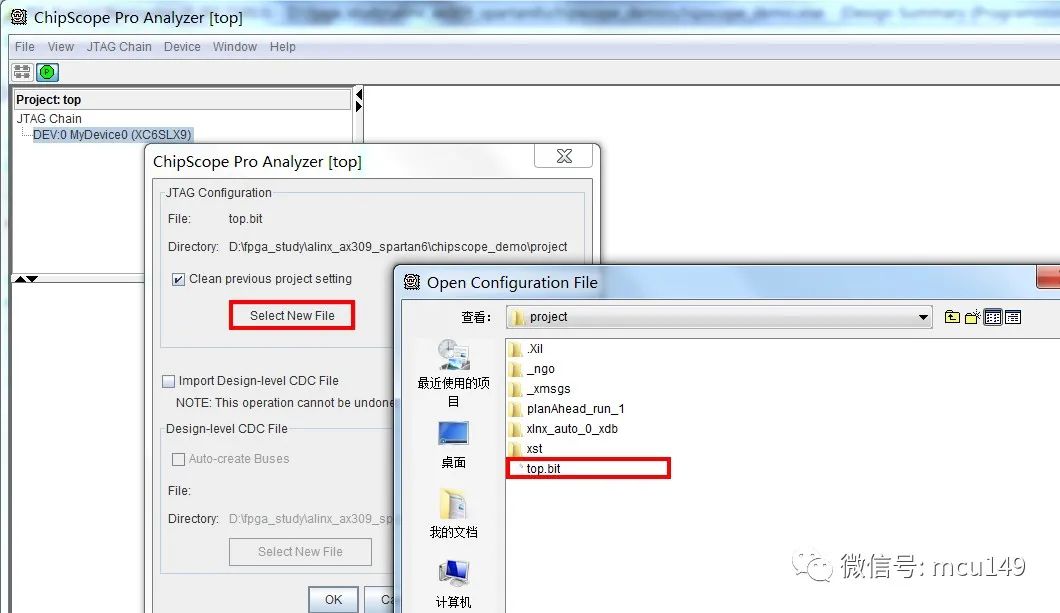

管腳分配,編譯通過,生成bit文件,打開ChipScope,下載bit文件。

ChipScope

下載Bit文件

選擇bit文件

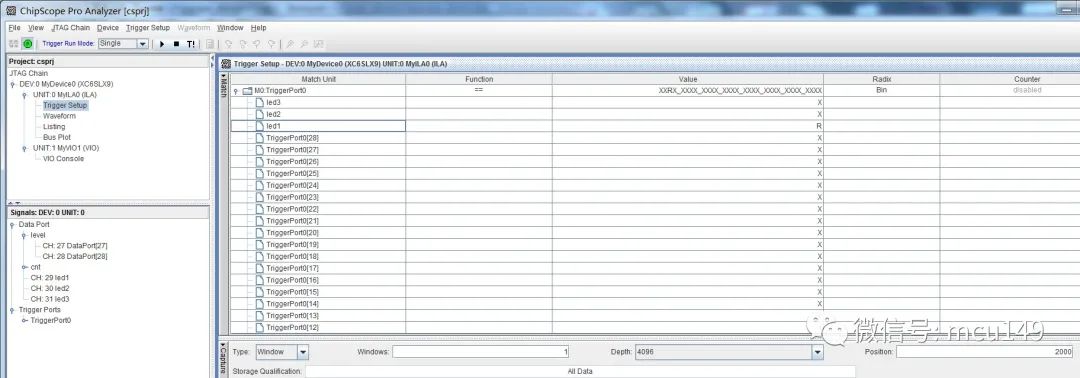

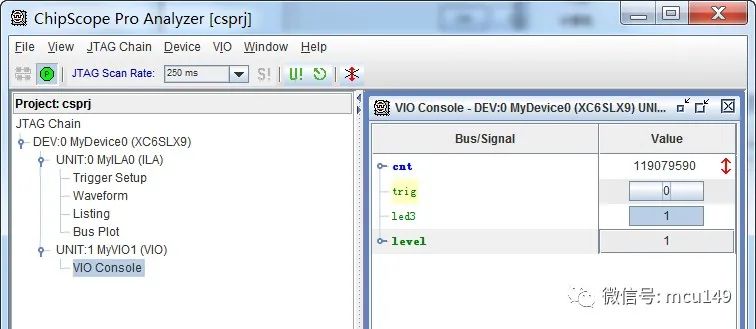

對信號進行重新命名,設置觸發信號,或者控制VIO輸出狀態。

設置觸發方式

trig設置成PushButton類型,并設置為高脈沖。

led3設置成ToggleButton類型,即按一下狀態翻轉一次。

VIO配置

8.總結

單片機在線調試可以設置斷點,讓程序停下,FPGA只要時鐘信號存在,就會一直運行下去,所以無法人為的設置斷點,中止代碼的運行。

任何事物都不可能達到十全十美,使用管腳外接的邏輯分析儀不會占用任何的邏輯資源,可以通過邏輯分析儀解析協議的報文,缺點是不能查看內部信號;使用片內邏輯分析儀的優點是可以實時查看內部信號,設置觸發條件,缺點是會占用FPGA的邏輯資源,比如RAM等。

Xilinx新一代的集成開發工具Vivado最低支持Spartan-7系列的FPGA芯片,由于手頭只有Spartan-6系列的開發板,所以無法演示在Vivado環境下的ChipScope使用,基本上都大同小異,使用方法類似,畢竟是同一家的調試工具。

9.參考資料

Xilinx官方文檔:chipscope_pro_sw_cores_ug029.pdf

審核編輯 :李倩

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603002 -

芯片

+關注

關注

455文章

50714瀏覽量

423149 -

STM32

+關注

關注

2270文章

10895瀏覽量

355743

原文標題:FPGA如何進行片上調試?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何在服務器上調試本地FPGA板卡

N76E885片上調度OCD功能,用什么調試器?

Renesas推出E8片上調試仿真器

如何使用X-DSP可測性設計與片上調試技術的研究與實現

支持片上測試和調試功能的在線調試模塊的應用設計

FPGA如何進行片上調試?

78K0/KF2Demo Board Campaign Board 用于 NEC QB-78K0MINI 片上調試仿真器的演示板

78K0/KF2Demo Board Campaign Board 用于 NEC QB-78K0MINI 片上調試仿真器的演示板

FPGA也能片上調試嗎?

FPGA也能片上調試嗎?

評論