更小硅幾何尺寸的不斷進步使嵌入式設備(尤其是微處理器)的工作電壓更低。處理器內核的工作電壓現在低至 1.2 V,并迅速升至 0.8 V,這對設計人員如何有效地為這些設備供電提出了挑戰。與使用線性穩壓器為低壓設備供電的傳統方法相反,在這些應用中使用開關穩壓器可以幫助解決這個問題。根據系統要求,設計人員可以使用各種架構來最大限度地提高開關穩壓器的效率。

典型的低功耗嵌入式處理器消耗 300-600 mA。在內核電壓為 3.3 V 的老一代處理器中使用開關穩壓器幾乎沒有什么好處。然而,降低核心電壓為提高效率提供了重要機會,尤其是在由鋰離子電池 (4.2 V) 或 5 V 軌供電時。例如,4.2 V 系統中的線性穩壓器在調節到 1.2 V 時會浪費 1.8 W [(4.2-1.2 V) x 600 mA]。相比之下,開關穩壓器在相同電壓下的效率最高可達 95%條件,這會給系統增加大量的運行時間。

開關穩壓器產生的潛在噪聲、輕負載時的低效率以及對更復雜控制的需求傳統上阻礙了設計人員將此類穩壓器用于嵌入式處理器。此外,線性穩壓器的占地面積更大,使線性穩壓成為首選方法。盡管如此,設計人員仍可以采用多種技術來大大提高開關電源的效率,并使開關穩壓器在不同類型的設計中可行。具有集成控制器、傳輸器件和補償組件的單個 IC 使開關穩壓器的設計密集度降低,實施起來更具成本效益。

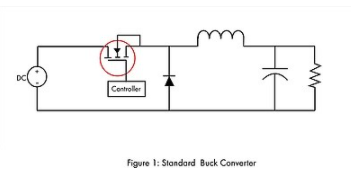

標準降壓拓撲

一個簡單的降壓開關包括場效應晶體管 (FET)、二極管、電感器、電容器和控制器,如圖 1 所示。在此拓撲中調節輸出電壓涉及改變 FET 柵極上的占空比以增加或減少通過電感器的電流,一種稱為脈沖寬度調制 (PWM) 的方法。PWM 開關穩壓器在滿載運行時的效率可高達 95% 以上。然而,當在輕負載下運行時,開關穩壓器的效率會顯著下降,這對于在不斷變化的負載條件下運行或需要低電流或睡眠模式的系統來說是不可取的。

圖1

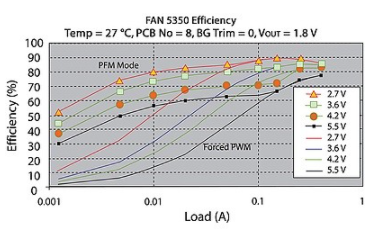

為了克服開關穩壓器在輕負載條件下效率低下的問題,設計人員可以將穩壓器置于脈沖跳躍或脈沖頻率調制 (PFM) 模式。在 PFM 模式下,開關穩壓器中的 FET 僅在輸出電壓低于下限時工作。這減少了脈沖數量,進而減少了通過 FET、電感器和二極管的開關損耗,從而提高了輕負載條件下的效率。對于圖 2 所示的器件,穩壓器以大約 100 mA 的電流從 PFM 轉換為 PWM,從而在整個輸出電流范圍內最大限度地提高效率。

圖 2

在使用 PFM 穩壓器進行設計時,設計人員必須考慮使用它的應用。由于切換器的頻率隨輸出負載而變化,因此切換頻率可能會降至音頻頻段,這可能會產生不良噪聲問題。幸運的是,當今市場上可用的某些工具可以確保頻率永遠不會進入音頻頻帶。盡管這些工具可能會導致輕負載下的效率略有下降,但它們可以為設計人員節省無數時間來消除噪聲問題。

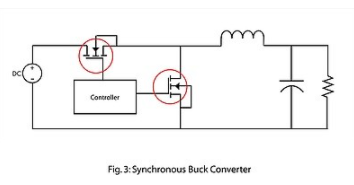

同步拓撲

設計人員可以使用同步拓撲進一步提高開關的效率,如圖 3 所示。這種拓撲可以通過用低 R ds(on) FET 替換二極管來降低開關損耗和二極管的反向恢復損耗。

圖 3

在此拓撲中,同步切換的時序至關重要。如果兩個 FET 都導通,則每個周期都會損失功率,效率會受到影響。此外,設計人員必須考慮選擇哪些器件。例如,FET 的柵極電容是一個重要的變量,因為它可以在控制器關閉 FET 后保持低側 FET 導通。在柵極保持充電的短時間內,輸入電源直接分流到地。R ds(on)和 FET 的柵極電容將對這種拓撲的效率影響最大;因此,優化兩者很重要。

在上述拓撲中,當電路板空間非常有限時,使用更高的開關頻率可能是有利的。更高的開關頻率允許設計人員使用更小的無源元件,例如電感器和輸出電容器,這可以降低設計成本和整體占位面積。然而,這是以降低效率為代價的。當頻率增加時,FET 開關的次數增加,這反過來又增加了損耗。此外,較小的電感器和電容器可能會在輸出電壓上產生較高的紋波。

多相拓撲

為了克服當今嚴格的紋波要求,同時保持嵌入式設計的效率,設計人員可以使用多相 DC-DC 開關。這種拓撲結構可以降低開關損耗,同時有效提高穩壓器的開關頻率。

例如,考慮連接到負載 I load的單相 DC-DC 同步開關。通過每個 FET 的開關損耗為 I 2 R 或 I load 2 * R ds(on)。在多相設計中,每個 FET 的開關損耗相同。但是,每相中的電流除以相數。因此,可以通過以下方式降低兩相設計中的開關損耗:

此外,多相設計改善了穩壓器的紋波電流和瞬態響應時間。這會增加成本和占位面積,因為必須為每相添加一個電感器和兩個 FET,并且控制器變得更大、更復雜。

縮小選項

電源效率是滿足便攜式產品延長電池壽命需求的關鍵。處理器制造商通過降低工作電壓來幫助這項工作,但電源必須適應以最大限度地提高效率。在決定最高效的電源時,檢查變量以確保電源滿足處理器要求非常重要。電源成本也必須是決策的一部分。

標準降壓開關在 PWM 模式下運行時可提供效率,并且比同步降壓更簡單,因此是一種更便宜的選擇。但是,二極管會產生電壓降,從而浪費一些功率。同步降壓使用 FET 代替二極管來降低此電壓降,從而提高效率但成本更高。

當處理器處于睡眠模式時,多模式穩壓器通過從 PWM 切換到 PFM 來提高整個負載范圍內的效率。這會增加一些輸出紋波電壓,但只要它保持在處理器的功率規格范圍內,就會顯著提高電池壽命。多相穩壓器在保持效率的同時消除了大部分輸出紋波電壓,但成本也更高。

設計人員在為嵌入式處理器設計電源時可以遵循這些指南。所有設計都需要權衡取舍,電源也不例外。考慮到任何設計的預算限制、電源要求和效率目標,這些策略將有助于縮小選擇范圍,以確定提供三者最佳折衷的電源。

作者:Brian Law,Greg Ferrell

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19262瀏覽量

229664 -

嵌入式

+關注

關注

5082文章

19108瀏覽量

304836 -

穩壓器

+關注

關注

24文章

4223瀏覽量

93763

發布評論請先 登錄

相關推薦

英特爾發布至強6處理器產品

充電也要算法?儲能充電芯片中的算法處理器

浪潮信息分布式存儲AS13000完成英特爾至強6能效核處理器適配

采用144核,能效提升66%!英特爾至強6處理器震撼上市,加速數據中心升級

差分可編程振蕩器,頻點50MHz,LVDS輸出,應用于音視頻處理器

英特爾發布至強6能效核處理器

英特爾首發數據中心能效核處理器,144核高密度,機架密度提升3倍

重磅!英特爾發布intel3制程至強6能效核處理器,賦能數據中心能效升級

英特爾?至強?6能效核處理器:Intel 3開山力作,每瓦性能提升2.6倍

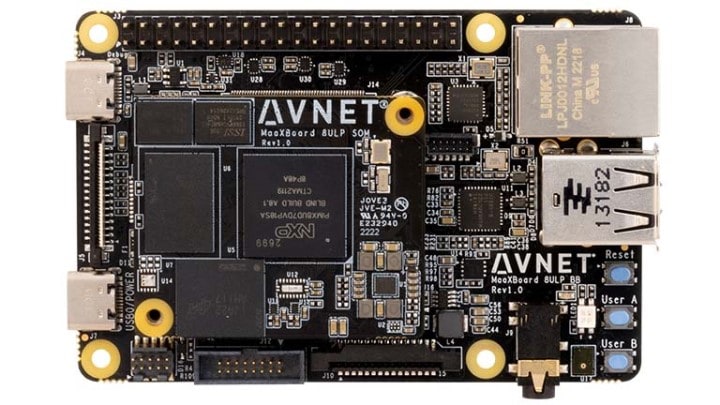

構建強大、高能效的i.MX 8ULP應用處理器合作生態體系

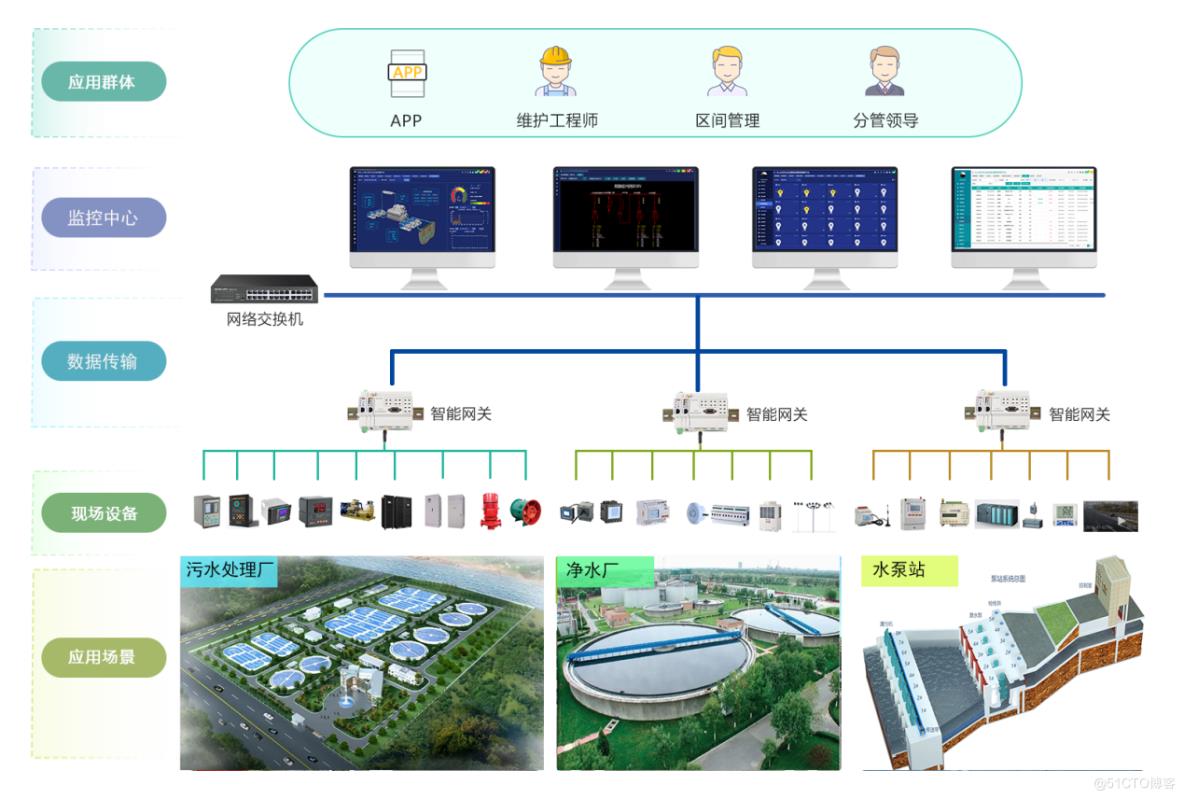

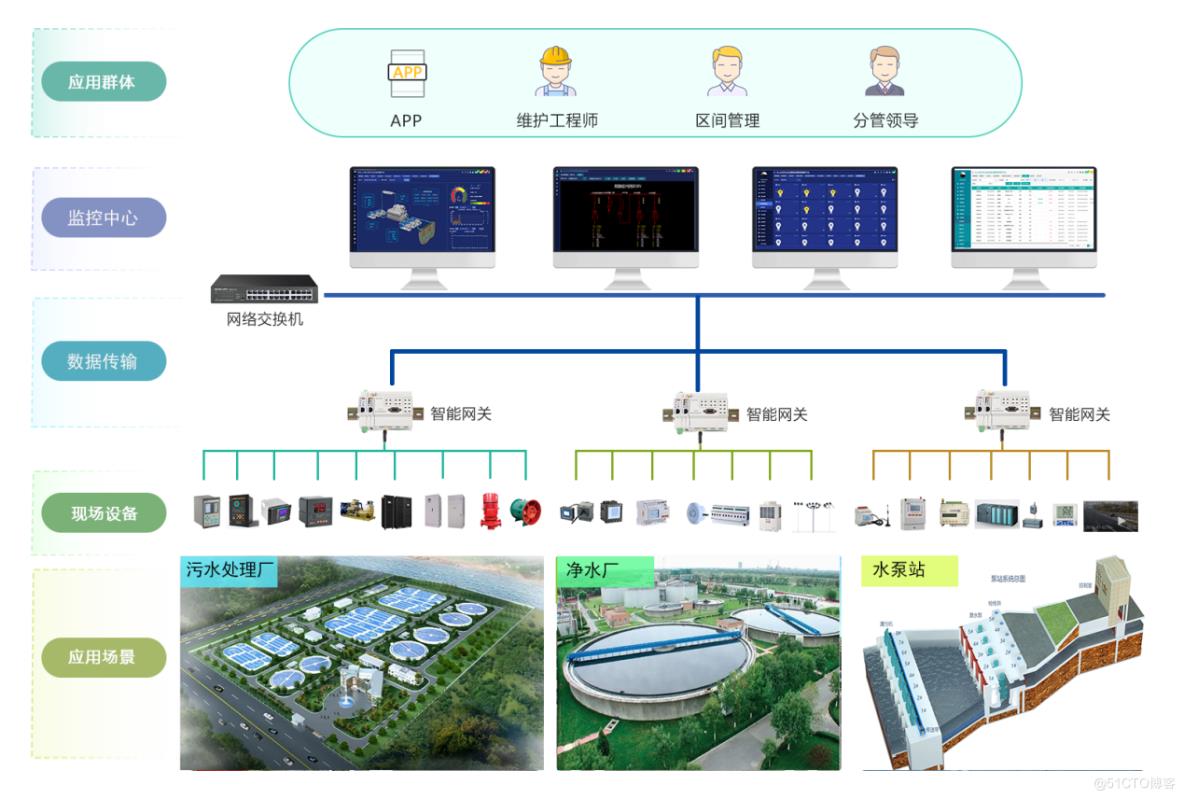

智慧水務能效管理平臺-為污水處理的能效管理提供科學、精細的解決方案

AMD EPYC 8004系列處理器優勢介紹

提高處理器能效的切換策略

提高處理器能效的切換策略

評論