執(zhí)行概要

就 FPGA 而言,可在設(shè)備的可編程邏輯中例化一個或多個軟核處理器,從而使設(shè)計(jì)人員能夠?qū)⒖删幊涛?a target="_blank">控制器和/或微處理器核添加到自己的設(shè)計(jì)中。

現(xiàn)在,基于 FPGA 的軟核處理器的性能在嵌入式市場中變得越來越重要。工業(yè)和軍用等市場中那些運(yùn)行復(fù)雜工作負(fù)載的嵌入式應(yīng)用需要能夠配備多種支持易用工具的高性能軟核處理器來加速軟件開發(fā)。

RISC-V 不但能夠滿足這些市場的性能需求,還能提供一條持續(xù)實(shí)現(xiàn)技術(shù)模塊或知識產(chǎn)權(quán)模塊(IP 模塊) 升級、不斷獲得先進(jìn)工具的途徑。發(fā)展壯大中的 RISC-V 生態(tài)系統(tǒng)也帶來了廣泛的軟件兼容性、更好的工具和編譯器支持,以及標(biāo)準(zhǔn)的調(diào)試環(huán)境。

通過將英特爾 FPGA 中使用的軟核處理器遷移到開放標(biāo)準(zhǔn),以及與知名 RISC-V 解決方案提供商 Ashling 合作,英特爾可使用戶獲得由現(xiàn)代集成開發(fā)環(huán)境 (IDE)、編譯器、調(diào)試器和操作系統(tǒng)組成的多元生態(tài)系統(tǒng)的支持。

英特爾 RISC-V 策略

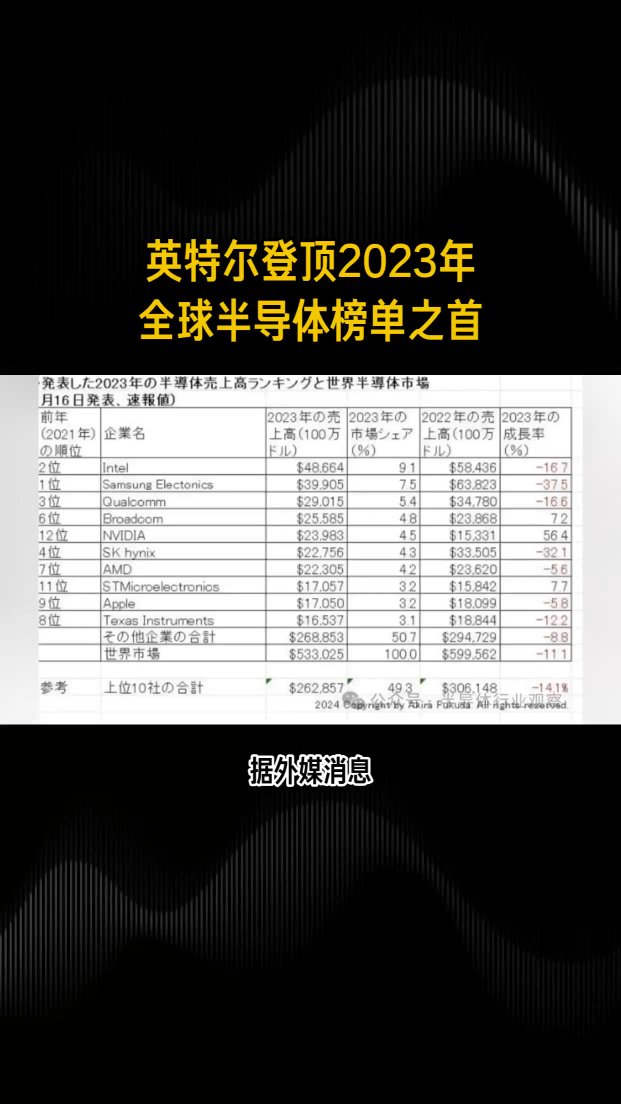

英特爾是微處理器行業(yè)的開拓者。早在 50 多年前的 1971 年就打造了首款商用微處理器英特爾 4004。1978 年,英特爾創(chuàng)造了 x86 架構(gòu),這是早期面向基于微處理器計(jì)算的指令集架構(gòu) (ISA) 之一。現(xiàn)在,x86 指令集架構(gòu)已經(jīng)發(fā)展成為世界上通用計(jì)算應(yīng)用廣泛使用的架構(gòu)。自 x86 指令集架構(gòu)問世以來,英特爾將 40 多年的時間都投入到開發(fā)成功的指令集架構(gòu)、建立卓有成效的合作關(guān)系以及發(fā)展高生產(chǎn)力水平的生態(tài)系統(tǒng)上,這些業(yè)界都有目共睹。

除了微處理器產(chǎn)品外,英特爾的可編程解決方案事業(yè)部還開發(fā)了大容量高性能 FPGA。這些設(shè)備為用戶提供了多種選擇,包括可配置的嵌入式 SRAM、高速收發(fā)器、高速輸入/輸出 (I/O)、邏輯塊和路由。內(nèi)置的 IP 模塊與出色的軟件工具相結(jié)合,有效縮短了 FPGA 開發(fā)時間、降低了功耗和成本。

2022 年 2 月,英特爾成為全球開放硬件標(biāo)準(zhǔn)組織 RISC-V International 的活躍成員。開放的 RISC-V 生態(tài)系統(tǒng)提供了現(xiàn)代計(jì)算不可或缺的開放式、模塊化構(gòu)建基礎(chǔ)。加入 RISC-V 后,英特爾展現(xiàn)出自身的領(lǐng)導(dǎo)力,開展了多項(xiàng)活動,為所有行業(yè)利益相關(guān)者擴(kuò)大了 RISC-V 生態(tài)系統(tǒng)的潛力。

基于 RISC-V 策略,英特爾與 RISC-V 生態(tài)系統(tǒng)內(nèi)各大合作伙伴通力合作,這些合作伙伴包括 Ashling、晶心科技、Esperanto Technologies、SiFive 和 Ventana Micro Systems。

英特爾計(jì)劃投入多筆資金,加強(qiáng) RISC-V 生態(tài)系統(tǒng)建設(shè)并幫助推動 RISC-V 進(jìn)一步落地。在英特爾的組織下,這些投資將幫助那些具有開創(chuàng)性的 RISC-V 公司通過在以下活動及其他方面開展合作,更快實(shí)現(xiàn)創(chuàng)新:

技術(shù)協(xié)同優(yōu)化

優(yōu)先晶圓共乘服務(wù)

支持客戶設(shè)計(jì)

建立開發(fā)板

不斷發(fā)展軟件基礎(chǔ)設(shè)施

例如,英特爾計(jì)劃提供一系列經(jīng)過驗(yàn)證的基于 RISC-V 的內(nèi)核,這些內(nèi)核的性能已針對不同的細(xì)分市場進(jìn)行了優(yōu)化。英特爾將通過與各大提供商合作,優(yōu)化面向英特爾制程工藝的 IP 模塊,以確保 RISC-V 能夠在從嵌入式內(nèi)核到高性能內(nèi)核的各種內(nèi)核類型的英特爾 芯片上運(yùn)行良好。RISC-V 產(chǎn)品將提供三種類型:

基于英特爾 技術(shù)制造的合作伙伴產(chǎn)品。

獲得差異化 IP 模塊許可的 RISC-V 內(nèi)核。

采用英特爾先進(jìn)封裝技術(shù)和高速芯片到芯片接口的 RISC-V 小芯片構(gòu)建模塊。

英特爾對 RISC-V 的投資,再加上 RISC-V 社區(qū)的支持,將加速開放式 RISC-V 模塊和其他交付產(chǎn)品的開發(fā)進(jìn)程。此外,英特爾晶圓代工服務(wù) (IFS) 部門還將贊助一個開源軟件開發(fā)平臺。該平臺支持自由開展實(shí)驗(yàn),生態(tài)系統(tǒng)、大學(xué)和聯(lián)盟的合作伙伴均可從中受益。這項(xiàng)代工服務(wù)策略將提供廣泛的面向英特爾制程工藝優(yōu)化的技術(shù)。英特爾晶圓代工服務(wù)能夠提供面向 x86、Arm和 RISC-V 全部三大行業(yè)主流指令集架構(gòu)優(yōu)化的技術(shù)。而且,英特爾已經(jīng)看到代工客戶對支持更多 RISC-V IP 模塊產(chǎn)品的強(qiáng)勁需求。

英特爾 eASIC 設(shè)備:

從 FPGA 到 ASIC 的捷徑

為了適應(yīng)各種業(yè)務(wù)和開發(fā)模式,英特爾還提供了先進(jìn)的英特爾 eASIC 設(shè)備和 ASIC 選擇方案。英特爾 eASIC 設(shè)備屬于結(jié)構(gòu)化 ASIC,這是一種介于 FPGA 和標(biāo)準(zhǔn)單元 ASIC 二者之間的中間技術(shù)。而標(biāo)準(zhǔn)單元 ASIC 則可以利用英特爾晶圓代工服務(wù)創(chuàng)建。該服務(wù)是一種完全垂直化的獨(dú)立代工業(yè)務(wù),旨在幫助滿足全球?qū)?a target="_blank">半導(dǎo)體不斷增長的需求。

英特爾 eASIC 設(shè)備性能介于 FPGA 和 ASIC 實(shí)現(xiàn)之間。使用英特爾 eASIC 設(shè)備,既可以保持與 FPGA 實(shí)現(xiàn)相同的主頻,又能夠降低功耗,還可以在保持散熱/功耗預(yù)算不變的同時提高性能。與標(biāo)準(zhǔn)單元 ASIC 相比,英特爾 eASIC 設(shè)備上市時間 (TTM) 更快,一次性成本投入 (NRE) 更低。相比之下,標(biāo)準(zhǔn)單元 ASIC 則能以更低的功耗提供更高的性能。一旦一種設(shè)計(jì)的英特爾 FPGA 實(shí)現(xiàn)得到驗(yàn)證,該設(shè)計(jì)就可以固化成為成本和功耗更低的英特爾 eASIC 設(shè)備或性能更高、功耗進(jìn)一步降低的 ASIC。開發(fā)人員還可能會從該設(shè)計(jì)的英特爾 FPGA 實(shí)現(xiàn)開始,隨后遷移到英特爾 eASIC 設(shè)備,然后再次遷移到完整的ASIC(圖 1)。

英特爾提供從 FPGA 到英特爾 eASIC 設(shè)備和 ASIC 的遷移路徑,以減少成本、降低功耗、提升性能。

英特爾的 RISC-V 策略既支持基于英特爾 FPGA 開發(fā) RISC-V,也支持后續(xù)部署到英特爾 FPGA、英特爾 eASIC 設(shè)備和ASIC(包括英特爾晶圓代工服務(wù)提供的 ASIC)。除了英特爾之外,其他公司較難提供從 FPGA 到英特爾 eASIC 設(shè)備再到ASIC 這些能夠減少成本、降低功耗、提升性能的遷移路徑。

RISC-V 對于FPGA 客戶的價值

RISC-V 是一種開源硬件指令集架構(gòu),始于 2010 年。不同于大多數(shù)其他指令集架構(gòu),RISC-V 是在開源許可下提供的。RISC-V指令集規(guī)范定義了 32 位和 64 位尋址空間變體。指令集具有可變寬度和可擴(kuò)展等特點(diǎn),為解決廣泛用例而設(shè)計(jì)。

除了具有開源指令集架構(gòu)這一屬性外,RISC-V 的成功還可以歸因于其實(shí)現(xiàn)模塊化、可擴(kuò)展性、穩(wěn)定性、效率和性能的設(shè)計(jì)宗旨。RISC-V 是一種“白板”設(shè)計(jì),沒有傳統(tǒng)或反向兼容方面的限制或約束,因此能夠?yàn)槲磥黹_放式計(jì)算設(shè)計(jì)的自由和創(chuàng)新鋪平道路。得益于多方參與者的加入,RISC-V 正借助目前可用的多種開源架構(gòu)實(shí)現(xiàn)方案推動多項(xiàng)創(chuàng)新。

商業(yè)企業(yè)要求指令集架構(gòu)即使對部署多年的產(chǎn)品也仍保持穩(wěn)定性。為了解決這一問題,2015 年 RISC-V 基金會 (RISC-VFoundation) 成立,負(fù)責(zé)制定、維護(hù)和發(fā)布 RISC-V 定義。為更好地發(fā)揮作用,這家非盈利性組織于 2020 年更名為 RISC-V International。

RISC-V 正迎來指數(shù)級增長。據(jù) RISC-V International 報告1 ,“承諾加入 RISC-V 和對 RISC-V 的投資持續(xù)飆升。2021 年,RISC-V 成員人數(shù)增長了 130%,達(dá)到 2,478 名成員,其中包括 18 名高級成員”。隨著數(shù)十億芯片部署就緒,從嵌入式汽車到超大規(guī)模人工智能 (AI)、從 5G 到高性能計(jì)算 (HPC) 等,RISC-V 在各行各業(yè)以及各種實(shí)現(xiàn)方案中得到廣泛的商業(yè)應(yīng)用。

RISC-V 的開源性質(zhì)開啟了通過開放標(biāo)準(zhǔn)合作來實(shí)現(xiàn)處理器創(chuàng)新的新時代。多方參與者正在推進(jìn)實(shí)現(xiàn)方案的創(chuàng)新,使廣泛的開源生態(tài)系統(tǒng)迅速崛起。該生態(tài)系統(tǒng)涵蓋復(fù)雜的硬件設(shè)計(jì)和驗(yàn)證工具、豐富的軟件開發(fā)工具套件、操作系統(tǒng) (OS) 和實(shí)時操作系統(tǒng) (RTOS) 端口等。硬核和軟核 RISC-V 處理器的激增也為應(yīng)用在不同實(shí)現(xiàn)方案之間的移植和應(yīng)用的長期維護(hù)提供了極大的便利條件。人們會看到,從一開始就是為充分利用 RISC-V 架構(gòu)的優(yōu)勢而開發(fā)的應(yīng)用將大量涌現(xiàn)。

就 FPGA 而言,可在設(shè)備的可編程邏輯中例化一個或多個軟核處理器,從而使設(shè)計(jì)人員能夠?qū)⒖删幊涛⒖刂破骱?或微處理器核添加到自己的設(shè)計(jì)中。同樣,對于在芯片中直接集成了一個、兩個或四個 Arm 硬核處理器的英特爾 片上系統(tǒng) (SoC) FPGA來說,必要時可在設(shè)備的可編程邏輯中例化更多軟核處理器。

自 2004 年推出以來,英特爾的 32 位 Nios II 處理器一直是使用英特爾 FPGA 和 SoC FPGA 的設(shè)計(jì)人員選擇的軟核處理器。多年來,Nios II 處理器積累形成了由開發(fā)人員、工具、軟件和軟件 IP 模塊組成的大型生態(tài)系統(tǒng)。

現(xiàn)在,英特爾已推出基于開源 RISC-V 指令集架構(gòu)、面向英特爾 FPGA 的新一代軟核處理器 Nios V 處理器。Nios V 處理器家族的第一款產(chǎn)品是 Nios V/m(“微控制器”版)。英特爾計(jì)劃增加更多 Nios V 處理器變體,包括一個“通用”版、一個“應(yīng)用類”版和一個“Linux”版,其中“Linux”版是能夠運(yùn)行 Linux 內(nèi)核的 64 位處理器。此外,英特爾還會加大對包括 Zephyr、FreeRTOS 和Linux 在內(nèi)的廣泛操作系統(tǒng)的支持。

利用 Nios 處理器中的 RISC-V 將會極大拓展當(dāng)下廣泛的 Nios 生態(tài)系統(tǒng),為基于 FPGA 的系統(tǒng)開發(fā)人員提供更大的靈活性、更出色的性能。Nios V 處理器采用與 Nios II 處理器相同的簡單設(shè)計(jì)流程,可通過英特爾 Quartus Prime Pro Edition Software 獲得。讓現(xiàn)有基于 Nios II 處理器的設(shè)計(jì)的創(chuàng)建者特別感興趣的是,他們可以把設(shè)計(jì)快速、輕松地移植到 Nios V 處理器。

由于 RISC-V 指令集架構(gòu)內(nèi)已實(shí)現(xiàn)多項(xiàng)架構(gòu)升級,與現(xiàn)有的軟核處理器相比,Nios V 軟核處理器能提供更好的性能。此外,RISC-V 還有一個關(guān)鍵優(yōu)勢,那就是軟件可移植性和穩(wěn)定性。舉例來說,開發(fā)人員可以利用軟核版 RISC-V 在 FPGA 中開始一項(xiàng)設(shè)計(jì),所編寫的任何在初始 RISC-V 軟核上運(yùn)行的軟件今后都可以在任何其他 RISC-V 核上運(yùn)行。

RISC-V 另一個非常重要的優(yōu)勢是,廣泛的開源生態(tài)系統(tǒng)迅速崛起。這一生態(tài)系統(tǒng)涵蓋硬件設(shè)計(jì)和驗(yàn)證工具、軟件開發(fā)工具(例如編譯器和調(diào)試器)、操作系統(tǒng) (OS) 和 RTOS 端口等。

英特爾大力投資 RISC-V 的一個例證是,英特爾通過與知名的RISC-V 工具供應(yīng)商和 RISC-V International 成員 Ashling 合作,向 FPGA 客戶提供面向 RiscFree 集成開發(fā)環(huán)境和統(tǒng)一調(diào)試器的完整開源工具解決方案。

RiscFree 對于 FPGA

和 ASIC 客戶的價值

如今的 SoC 和系統(tǒng)級封裝 (SiP) 設(shè)計(jì)正變得越來越復(fù)雜,這是因?yàn)樾酒O(shè)計(jì)人員需要將更多的功能集成到單一的器件和單一的封裝中,以滿足市場對于更多功能、更高性能和更低功耗的需求。由于制程工藝的改進(jìn)出現(xiàn)瓶頸,設(shè)計(jì)人員只得不斷采用多核設(shè)計(jì)。此外,他們還將多種異構(gòu)處理器架構(gòu)(如 RISC-V、Arm和 x86)整合到同一 SoC 或 SiP 中。

促使 RISC-V 獲得成功的一個主要因素是,不同的公司和實(shí)體可以將指令集架構(gòu)作為自己獨(dú)特的差異化實(shí)現(xiàn)方案(例如不同的數(shù)據(jù)寬度、管道寬度和管道架構(gòu))的基礎(chǔ)。這使 RISC-V 處理器能夠以廣泛的形式出現(xiàn),從面向邊緣微控制器應(yīng)用的基于 32 位 FPGA 的軟核處理器到面向云端高性能計(jì)算應(yīng)用的基于 64 位 SoC 的硬核處理器,無所不包。

Ashling 的 RiscFree 集成開發(fā)環(huán)境和統(tǒng)一調(diào)試器為全部 RISC-V實(shí)現(xiàn)提供支持。自推出以來,RiscFree 工具鏈穩(wěn)步在嵌入式工具市場拿下市場份額,在 RISC-V 市場上更以其易用性、廣泛的功能和插件式架構(gòu)而表現(xiàn)搶眼。

RiscFree 可以針對上述設(shè)備使用單一調(diào)試探針,從單一軟件環(huán)境提供全面開源的多核(同構(gòu)和異構(gòu))調(diào)試解決方案,為 ASIC 客戶帶來附加價值。RiscFree 完全支持 Nios V 處理器,同樣也可為 FPGA 客戶帶來附加價值。

就英特爾 FPGA 而言,RiscFree 包括一個開源的、基于 Eclipse 的集成開發(fā)環(huán)境、編譯器、調(diào)試器和跟蹤程序。這種單次安裝程序開箱可用,可為基于 RISC-V 指令集架構(gòu)的所有 32 位和 64 位Nios V 軟核處理器提供 RiscFree 軟件開發(fā)和調(diào)試支持。

除了自定義集成和支持向 Nios V 處理器擴(kuò)展外,RiscFree 還支持英特爾 Agilex 、英特爾 Stratix 10、英特爾 Arria 10和英特爾 Cyclone 10 GX 設(shè)備,以及后續(xù)的更多產(chǎn)品系列。

Ashling 與英特爾合作的價值

自 1982 年以來,Ashling 一直是重要的嵌入式開發(fā)工具和服務(wù)提供商,有著 30 余年的嵌入式系統(tǒng)工具開發(fā)經(jīng)驗(yàn)。作為 RISC-VInternational 的長期成員,Ashling 始終密切關(guān)注 RISC-V 的發(fā)展,尤其重視調(diào)試標(biāo)準(zhǔn)及跟蹤標(biāo)準(zhǔn)。作為跟蹤技術(shù)委員會 (Tracecommittee) 的副主席,Ashling 參與制定了第一批定義 RISC-V 實(shí)時跟蹤的標(biāo)準(zhǔn)。

與 Ashling 合作,英特爾便有了自己的工具提供商,可確保其所有 Nios V 處理器的工具需求均能得到滿足,包括由集成開發(fā)環(huán)境、編譯器、調(diào)試器及 Nios V 處理器和 Arm 處理器跟蹤支持組成的完整開源工具鏈。

兩家公司已計(jì)劃保持長期合作,因此,隨著英特爾 Nios V處理器家族的發(fā)展壯大,工具鏈也會隨之發(fā)展,以確保能夠充分支持新產(chǎn)品和新功能。

Ashling 與英特爾團(tuán)隊(duì)在工程設(shè)計(jì)方面的合作將確保 Ashling 軟件開發(fā)與英特爾 FPGA 開發(fā)工具鏈緊密耦合,例如:

01項(xiàng)目管理器和構(gòu)建管理器包括 Make 和 Cmake 支持,可快速導(dǎo)入、構(gòu)建和調(diào)試英特爾 Quartus 軟件創(chuàng)建的應(yīng)用框架。

02Nios V GCC 編譯器工具鏈完全整合到 RiscFree 集成開發(fā)環(huán)境中,可以為使用 Nios V HAL API 接入硬件的 newlib和 picolibc 運(yùn)行時庫提供支持。

03RiscFree 提供運(yùn)行時調(diào)試功能,可以支持英特爾 FPGA Download Cable II (USB Blaster II)、Nios V 和 Arm 處理器內(nèi)核寄存器虛擬化,以及對 Nios V 和 Arm 兩種處理器內(nèi)核的實(shí)時片上和片下跟蹤。

04RiscFree 還為 Zephyr、FreeRTOS、uC/OS-II 以及完整的目標(biāo)(多核/多 Hart)Linux 內(nèi)核等各種 OS 和 RTOS 解決方案提供感知調(diào)試能力,同時也支持設(shè)備驅(qū)動程序和應(yīng)用調(diào)試。

05RiscFree 支持面向 Nios V 處理器的自定義指令和擴(kuò)展。

在很多同時采用 Arm 和 RISC-V 處理器內(nèi)核(硬核和/或軟核)的開發(fā)環(huán)境中,必須運(yùn)用多種調(diào)試器,一種用于 Arm 處理器,一種用于 RISC-V 處理器。經(jīng)過比較,單個 RiscFree 實(shí)例支持調(diào)試任意數(shù)量的異構(gòu)或同構(gòu)內(nèi)核;例如,同時調(diào)試英特爾 FPGA Arm硬核和 Nios V 軟核。

英特爾與競爭對手

多數(shù)競爭對手只提供閉源的專有解決方案,而英特爾則能讓您全面獲得開源 RISC-V 生態(tài)系統(tǒng)的支持。解決方案目前支持 RISC-V開發(fā),后續(xù)還支持部署到英特爾 FPGA、英特爾的結(jié)構(gòu)化 ASIC 和英特爾晶圓代工服務(wù)提供的 ASIC。

在 Ashling 及其 RiscFree 集成開發(fā)環(huán)境和統(tǒng)一調(diào)試器的支持下,英特爾作為開放式生態(tài)系統(tǒng)的合作伙伴,可以利用其 RISC-V 開發(fā)人員目前可用的易用開源工具,支持完整的跨越 FPGA、英特爾 eASIC 設(shè)備和 ASIC 的自定義邏輯連續(xù)體。

總結(jié)

除了向全球供應(yīng)強(qiáng)大的微處理器,英特爾還開發(fā)了先進(jìn)的 FPGA。FPGA 經(jīng)過配置可以執(zhí)行多種功能,包括例化一個或多個軟核處理器。這些軟核處理器的性能在嵌入式市場中變得越來越重要。

RISC-V 是一種開源硬件指令集架構(gòu)。RISC-V 定義為一種“白板”設(shè)計(jì),沒有傳統(tǒng)或反向兼容方面的限制或約束,其設(shè)計(jì)宗旨就是要實(shí)現(xiàn)模塊化、可擴(kuò)展性、穩(wěn)定性、效率和性能。因此,RISC-V 正迎來指數(shù)級增長。

英特爾加入全球開放硬件標(biāo)準(zhǔn)組織 RISC-V International,積極發(fā)揮領(lǐng)導(dǎo)作用,致力于為所有行業(yè)利益相關(guān)者擴(kuò)大 RISC-V 生態(tài)系統(tǒng)的潛力。

英特爾現(xiàn)已發(fā)布了基于開源 RISC-V 指令集架構(gòu)、面向英特爾 FPGA 的新一代軟核處理器 Nios V 處理器。除了面向 FPGA的軟核 Nios V 處理器,英特爾還將提供面向英特爾 eASIC 設(shè)備和 ASIC 的硬核 RISC-V 實(shí)現(xiàn)方案。此外,英特爾還提供從FPGA 到英特爾 eASIC 設(shè)備和 ASIC 的遷移路徑。除了英特爾之外,其他公司較難提供從 FPGA 到英特爾 eASIC 設(shè)備再到ASIC 這些能夠減少成本、降低功耗、提升性能的遷移路徑。

英特爾的合作伙伴 Ashling 是 RISC-V International 的長期成員,Ashling 的 RiscFree 集成開發(fā)環(huán)境和統(tǒng)一調(diào)試器為全部RISC-V 實(shí)現(xiàn)提供支持。自推出以來,RiscFree 工具鏈便憑借其易用性、廣泛的功能和插件式架構(gòu),在包括 RISC-V 市場在內(nèi)的嵌入式工具市場得到廣泛應(yīng)用。

Ashling 的 RiscFree 能夠針對上述設(shè)備使用單一調(diào)試探針,從單一軟件環(huán)境提供全面開源的多核(同構(gòu)和異構(gòu))調(diào)試解決方案,為英特爾的 FPGA 和 ASIC 客戶帶來附加價值。

英特爾計(jì)劃加大投資力度,以加強(qiáng) RISC-V 生態(tài)系統(tǒng)建設(shè)并推動 RISC-V 進(jìn)一步落地。在英特爾的組織下,這些投資將幫助具有開創(chuàng)性的 RISC-V 公司通過在技術(shù)協(xié)同優(yōu)化、優(yōu)先晶圓共乘服務(wù)、支持客戶設(shè)計(jì)、建立開發(fā)板和發(fā)展軟件基礎(chǔ)設(shè)施這些方面開展合作,更快實(shí)現(xiàn)創(chuàng)新。

原文標(biāo)題:白皮書丨英特爾攜手知名RISC-V工具提供商Ashling,著力擴(kuò)展多平臺RISC-V支持

文章出處:【微信公眾號:英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603980 -

英特爾

+關(guān)注

關(guān)注

61文章

9978瀏覽量

171888 -

RISC-V

+關(guān)注

關(guān)注

45文章

2292瀏覽量

46210

原文標(biāo)題:白皮書丨英特爾攜手知名RISC-V工具提供商Ashling,著力擴(kuò)展多平臺RISC-V支持

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

世紀(jì)大并購!傳高通有意整體收購英特爾,英特爾最新回應(yīng)

英特爾推出全新英特爾銳炫B系列顯卡

英特爾CEO Gelsinger宣布退休

剛剛!英特爾最新回應(yīng)

從運(yùn)動員到開發(fā)者: 英特爾以開放式AI系統(tǒng)應(yīng)對多重挑戰(zhàn)

英特爾加速AI PC發(fā)展,預(yù)計(jì)到2028年占據(jù)80%市場份額

英特爾CEO:AI時代英特爾動力不減

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

英特爾旗下FPGA公司Altera正式亮相

英特爾成立全新獨(dú)立運(yùn)營的FPGA公司Altera

英特爾旗下Altera正式獨(dú)立運(yùn)作,FPGA市場將迎來怎樣的巨變?

英特爾成立Altera新公司,專注FPGA端到端解決方案

英特爾eASIC設(shè)備:從FPGA到ASIC的捷徑

英特爾eASIC設(shè)備:從FPGA到ASIC的捷徑

評論