引言

隨著對多功能移動消費電子設備需求的增加,半導體芯片互連密度的復雜性不斷增加。傳統的芯片到封裝集成(CPI)使用引線鍵合將鍵合焊盤互連到封裝引線。隨著芯片規模向原子級發展,采用硅通孔(TSV)技術的芯片間互連成為一種極具吸引力的潛在解決方案,可實現更高的性能和更低的制造成本。穿過硅芯片的垂直電互連可以縮短芯片間互連的長度,并實現更緊湊的CPI互連結構。在TSV制造中,硅中具有受控側壁輪廓的高深寬比結構對于納米和微米尺度的微電子器件非常重要。

關鍵詞:硅通孔,等離子蝕刻

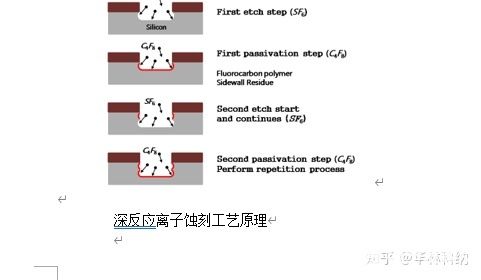

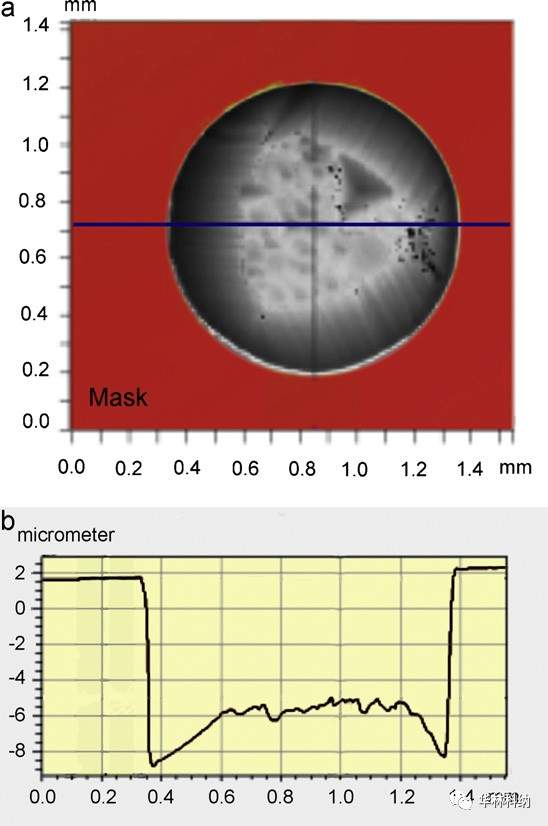

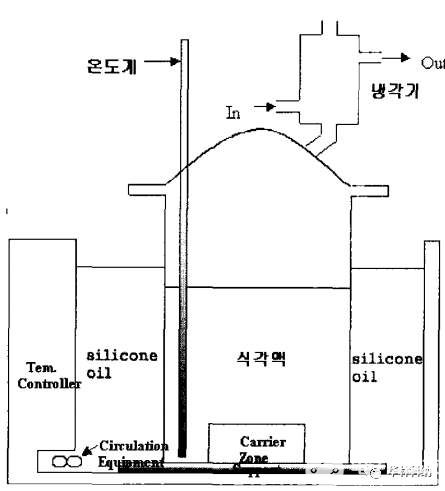

TSV互連技術包括深度硅蝕刻用于通孔形成、絕緣襯墊層沉積和用導電金屬填充通孔。通過等離子體蝕刻可以獲得垂直和深的硅通孔蝕刻,但是這仍然是一種具有挑戰性的復雜制造工藝。深硅通孔蝕刻需要高能離子轟擊,以提供足夠的動能來破壞晶片上硅原子的化學鍵,以及高活性自由基的直接化學反應,從而形成揮發性蝕刻副產物。深通孔區域中的離子充電可能導致硅蝕刻的局部化。反應性自由基可以增加硅通孔的蝕刻速率,但是它也增加了tsv的橫向蝕刻速率。增加的離子轟擊會導致通孔蝕刻掩模的腐蝕,質量差的蝕刻掩模會導致粗糙的側壁輪廓。最近的研究采用碳氫化合物和氫氟碳化合物(HFC)氣體化學,通過形成側壁鈍化來改善TSV蝕刻剖面,并防止蝕刻掩模腐蝕。

在這項研究中,我們調查了不同類型的影響

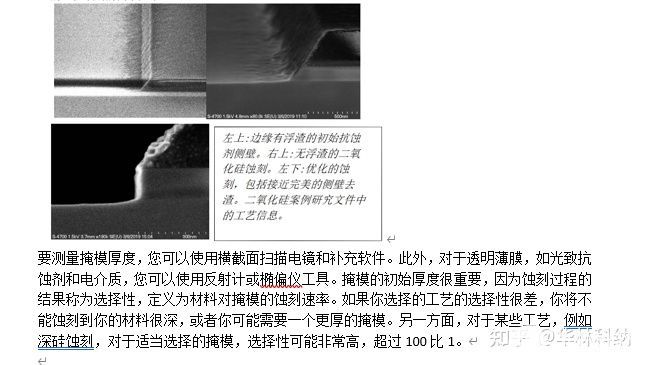

TSV蝕刻中的蝕刻掩模以及tsv中的側壁輪廓的影響。我們首先用傳統的光刻膠(PR)掩模檢查了TSV的側壁輪廓,并研究了兩種類型的硬掩模對tsv側壁輪廓的影響。研究的TSV蝕刻材料是光致抗蝕劑、二氧化硅和鋁。隨著掩模的圖案尺寸變窄,蝕刻深度和蝕刻速率趨于降低。

結果

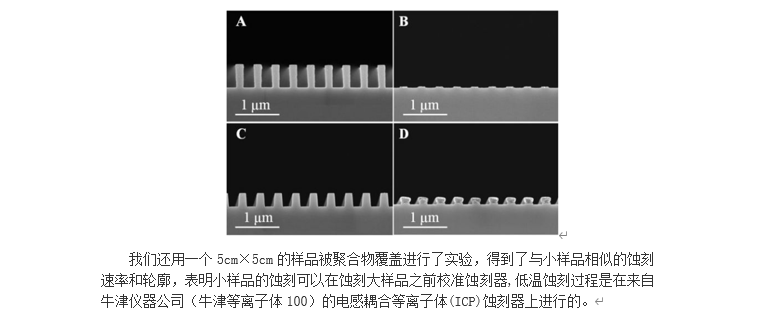

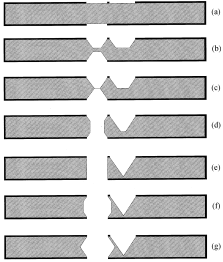

使用三種不同蝕刻掩模的蝕刻輪廓結果:光刻膠、氧化物和金屬。評估不同類型的蝕刻掩模所考慮的因素是底切、殘留和蝕刻速率。

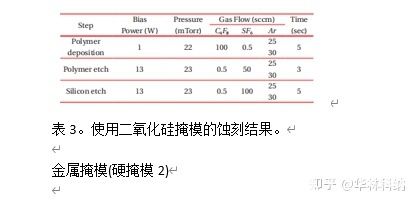

氧化物掩模(硬掩模1)

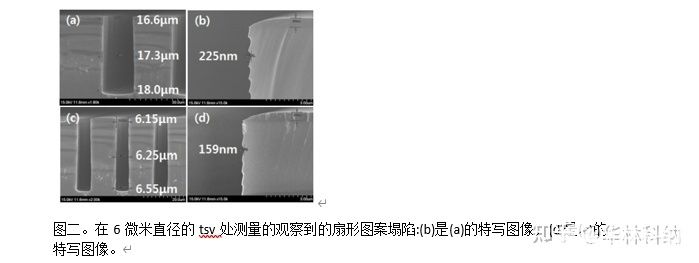

光致抗蝕劑是用于較大直徑的tsv的有用的蝕刻掩模材料,但是可能不適合用于塌陷扇形的較小尺寸的通孔。為了進一步研究用于較小尺寸TSV圖案化的光致抗蝕劑的替代物,我們研究了硬掩模材料。第一種候選材料是二氧化硅(SiO2),蝕刻后的TSV剖面的幾何特征如表3所示。直徑大于20微米的tsv超出了本實驗的范圍。以前在ARDE也觀察到較大尺寸的TSV蝕刻,因為不管蝕刻掩模材料的類型如何,通孔直徑都在減小。

就采用二氧化硅硬掩模的硅蝕刻速率而言,成功證明了TSV蝕刻掩模低至3微米直徑tsv的潛力。我們在直徑為2微米的TSV中觀察到非均勻蝕刻的TSV剖面,這被稱為負載效應。

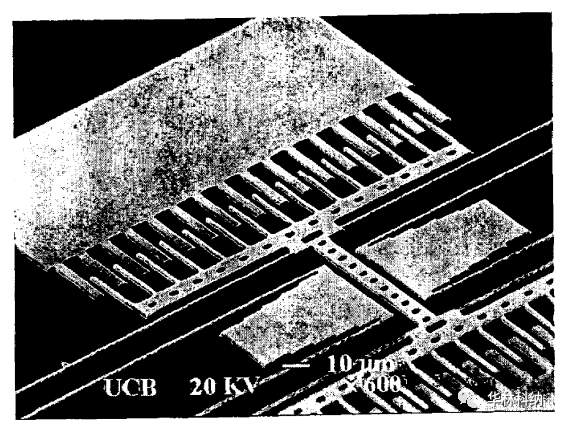

在半導體制造中使用的金屬候選物中,通常選擇鋁,因為它們易于制造并且與常規制造工藝步驟兼容。在需要銅金屬互連來減少互連延遲之前,鋁已經廣泛用于金屬互連。在許多半導體產品中,它仍然用于后段制程(BEOL)互連和焊盤。雖然在傳統的半導體制造工藝中不使用金屬蝕刻掩模,但是我們對這種用于成功制造tsv的更精細特征的耐用且可靠的蝕刻掩模感興趣。表4顯示了使用金屬硬掩模的通孔蝕刻結果。隨著圖案尺寸變得越來越小,也觀察到了ARDE,如先前用不同的候選掩模進行的實驗所示。

比較表3和表4中所示的蝕刻速率,兩種類型的硬掩模在各種尺寸的tsv中顯示出相似的蝕刻速率。與硬氧化物掩模不同,金屬掩模顯示出改善的底切和扇形塌陷,并且蝕刻輪廓總結在表4中。圖6示出了在2個微米直徑的TSV中的TSV蝕刻輪廓。

結論

在這個實驗中,我們華林科納半導體研究了用于制造更精細尺寸的硅通孔(tsv)的蝕刻掩模材料。傳統上用作硅蝕刻掩模的光致抗蝕劑可能不適合使用Bosch工藝的TSV制造的更精細的特征,并且我們建議對更精細的tsv使用硬掩模以減少底切和塌陷的扇形的數量。鋁中的硬金屬掩模提供了直徑小至2微米的tsv的優良側壁輪廓。二氧化硅硬掩模在制造小于20微米、直徑小至幾微米的tsv時是有用的,但是氧化物掩模下的底切問題仍然存在。不考慮蝕刻硬掩模材料,觀察到來自離子遮蔽的ARDE。

審核編輯:符乾江

-

半導體

+關注

關注

334文章

27442瀏覽量

219462 -

蝕刻

+關注

關注

9文章

414瀏覽量

15429

發布評論請先 登錄

相關推薦

一種用非金屬掩模層蝕刻碳化硅的方法

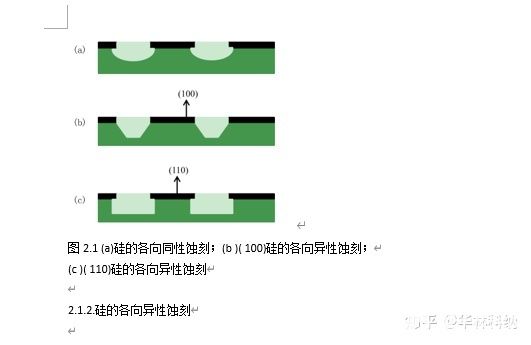

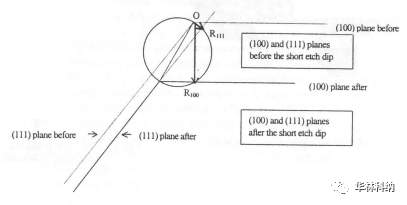

使用KOH各向異性蝕刻Si的光學器件的單掩模微制造(下)

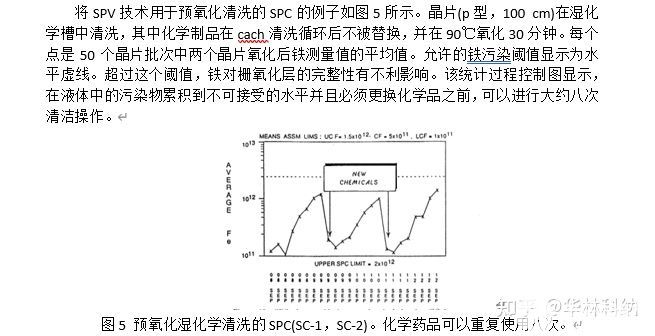

硅濕法蝕刻中的表面活性劑

掩模曝光劑量的精細控制工藝設計

氫氧化鉀在凸角處的蝕刻行為

各向同性和各向異性工藝如何用于改善硅濕蝕刻

詳解單晶硅的各向異性蝕刻特性

采用濕蝕刻技術制備黑硅

不同掩模材料對400nm瀝青光柵蝕刻特性的影響

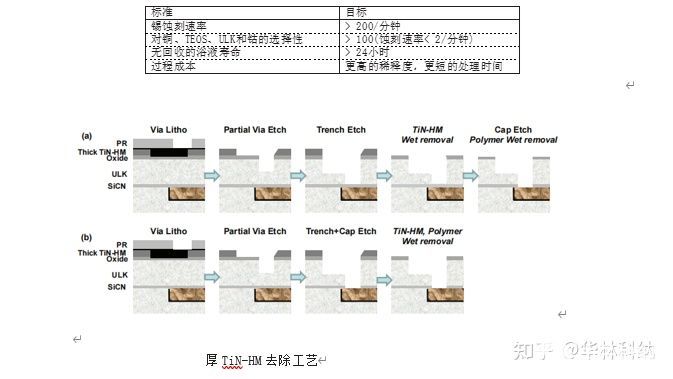

TiN硬掩模濕法去除工藝的介紹

一種穿過襯底的通孔蝕刻工藝

使用硬掩模進行更精細的硅通孔蝕刻

使用硬掩模進行更精細的硅通孔蝕刻

評論