高速Serdes均衡技術介紹

FPGA高速收發器的接收通道上有2種均衡模式:CTLE(連續時間線性均衡)和DFE(判決反饋均衡)。1連續時間線性均衡

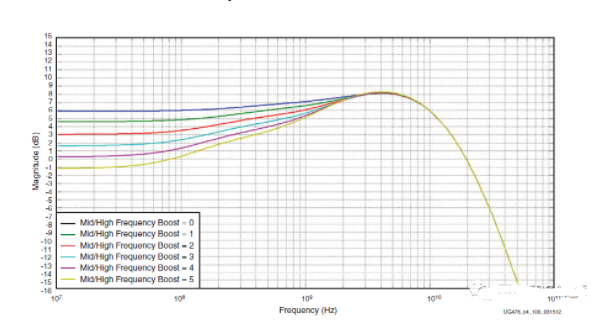

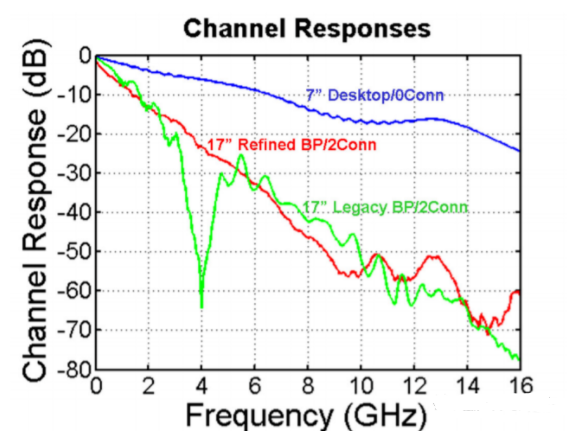

CTLE(連續時間線性均衡)是一種應用于接收的線性濾波器,可衰減低頻信號分量,放大奈奎斯特頻率附近的分量,并衰減更高頻率,這樣就抵消了通道的低通特性。如下圖所示,可以調整 CTLE 增益以優化低頻衰減與高頻放大的比率。CTLE的缺點是放大高頻分量的同時噪聲和串擾也被放大。和上一篇提到的發送預加重一樣,兩者都通過反轉通道的低通特性來解決通道損耗的問題,所以它們的功能其實很相似。在GT wizard中選擇LPM 模式就是使用CTLE模式,FPGA里面的CTLE參數已經是自動調整了,不需要我們去設置。CTLE模式的功耗比DFE模式小10%-15%,在通道損耗小于12db時候建議使用LPM模式。板內互聯情況下通道衰減基本上都小于12db,使用LPM模式是一個比較好的的選擇。

2判決反饋均衡

DFE(判決反饋均衡)是一種非線性均衡器,在上一篇文章里面我們提到發送數據在經過有損通道后,高頻成分被衰減,帶來的影響是前一個bit數據污染了后來一個數據,引起了ISI(碼間干擾)。

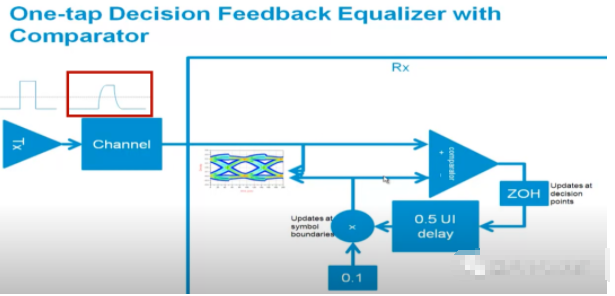

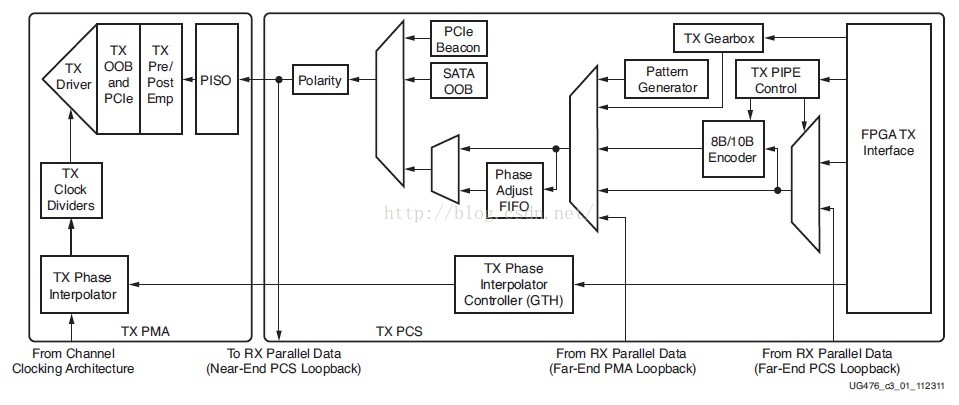

DFE的解決思路是:如果我們知道前一個bit對后面幾個bit的影響有多大,在收到后面bit的時候把前面bit的影響去除,那就得到了干凈的數據。下圖中Rx框圖內是DFE模塊的結構。

這個是1個tap的判決反饋均衡器,Tx發送的數據是0-1-0, 經過有損通道后因為ISI的影響,我們可以看到圖中紅圈接收的0-1-0 波形有些畸變。我們假設前一個數據對后面的數據影響因素是10%。

DFE 模塊中的slicer切片器就是一個采樣保持器。串行數據經過CDR后恢復出時鐘,時鐘會在數據的中心位置采樣數據。采樣數據1經過延遲0.5個符號周期(UI)后,把采樣數據1乘0.1也就是衰減10%,在后續接收到數據0時候減去衰減10%的前一個接收數據1,這樣我們就消除了前面的數據1對后面數據0的影響。這就是判決-反饋的含義。

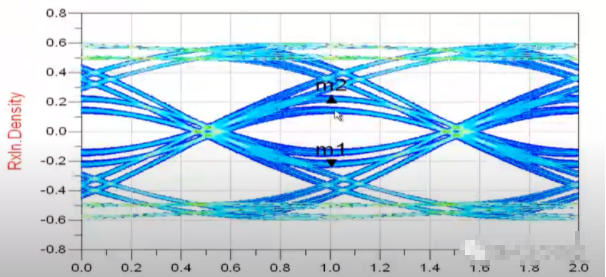

我們可能有些疑問為何延遲不是1個符號周期,而是0.5個符號周期?下圖是不使用DFE均衡,我們看到接收的眼圖比較小。

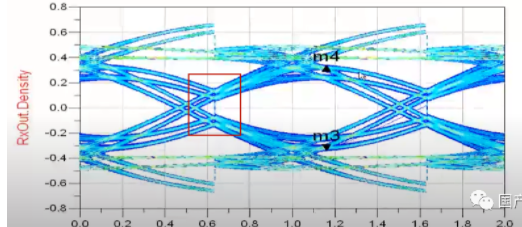

下圖是使用DFE均衡后,眼圖張開的比上圖要大,我們注意紅圈位置是數據的變化沿,DFE延遲0.5個UI,因此在下一個數據的變化沿處就開始減去前一個bit帶來的影響,而不是只在數據的采樣位置才起作用,這樣的效果是整個的眼圖都變大了,所以DFE的眼圖看起來有不連續性。

3DFE特點介紹

DFE的優點:

1)DFE和CTLE相比不會放大噪聲和串擾,數據經過衰減很大的通道后接收的數據信號幅度已經很小了,這個時候高頻的噪聲和串擾對信號影響就會很大。

2)在高速收發器通過背板連接的應用中,因為過孔和連接器阻抗不匹配引起反射,通道的衰減就像圖中淺綠的線,在某些頻率點衰減很大。在這種情況下CTLE的效果就比較差,DFE的效果就會比較好。

DFE的缺點:

1)設計DFE比CTLE難度大,這個是芯片設計的事情,我們不需要關心。

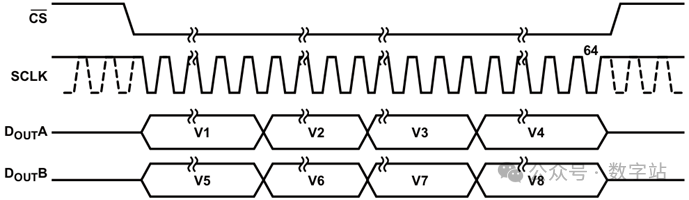

2)目前DFE的參數在FPGA中都是算法自動調整,不需要我們去設置,但是我們能看出DFE有一個錯誤傳播的特點,如果前面一個bit判斷錯誤,DFE算法會在后面幾個bit中起到負面作用。在使用8B10B編碼的協議而且數據沒有加擾的情況下,如果線路上長時間發送固定碼型會使得DFE自動調整算法漂移,引起負面效果。因此在8B/10B編碼而且數據沒有加擾的協議里面是不建議使用DFE的。我們都知道更高速的協議使用的都是64B/66B或者128B/130B編碼,這種編碼下數據都是加擾的。而且速率高通道衰減也大,所以DFE一般用在這種場合。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604293 -

收發器

+關注

關注

10文章

3438瀏覽量

106068 -

濾波器

+關注

關注

161文章

7845瀏覽量

178393

發布評論請先 登錄

相關推薦

FPGA高速收發器的GTX發送端解析

FPGA設計之GTP、GTX、GTH以及GTZ四種串行高速收發器

視頻: Artix-7 FPGA:如何在大批量應用中使用高速SerDes

FPGA高速收發器設計要遵循哪些原則?

高速ADC與高速串行收發器

基于XilinxVirtex?-6FPGA 11.18 Gbps收發器的高速互操作性

Logos系列FPGA高速串行收發器(HSST)用戶指南

FPGA高速收發器的高速Serdes均衡技術

FPGA高速收發器的高速Serdes均衡技術

評論