本發(fā)明涉及一種在集成電路制造中減少漏電流的方法,更具體地說,涉及一種在集成電路制造中通過新的預(yù)氧化清洗順序減少超薄柵氧化物漏電流的方法。

根據(jù)本發(fā)明的目的,實現(xiàn)了一種預(yù)氧化清洗襯底表面的新方法。我們?nèi)A林科納使用多步清洗工藝清洗晶片的半導(dǎo)體襯底表面,其中清洗工藝的最后一步包括用HMSO和HCO的溶液清洗,由此在晶片表面上形成化學(xué)氧化物初始層。此后,晶片的表面被氧化以形成熱氧化層,其中在集成電路的制造中,化學(xué)氧化層和熱氧化層一起形成柵氧化層。

優(yōu)選實施例的描述

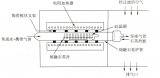

現(xiàn)在更具體地參考圖1,示出了部分完成的集成電路的一部分電路。示出了優(yōu)選由單晶硅構(gòu)成的半導(dǎo)體襯底10。集成電路器件的每個有源區(qū)將與其他有源區(qū)隔離。例如,硅的局部氧化(LOCOS)可以用于形成場氧化區(qū),或者可以形成諸如12的淺溝槽隔離(STI)區(qū)。

對于深亞微米CMOS技術(shù),柵極氧化層必須超薄,可能在15到20埃的數(shù)量級。為了減少漏電流,在形成超薄柵氧化層之前,半導(dǎo)體襯底的表面必須非常干凈。

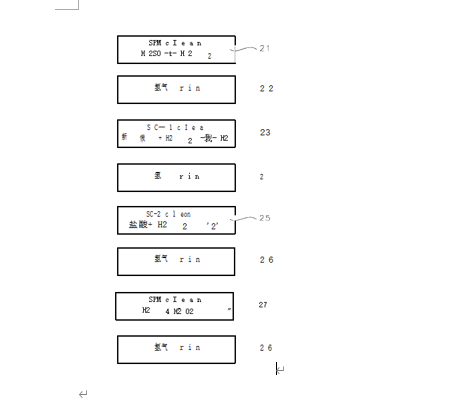

例如,圖2是說明本發(fā)明優(yōu)選實施例中的清潔步驟的流程圖。首先,執(zhí)行SPM清潔(21)。使用HMSO 4+HCO的溶液清洗晶片。然后用水沖洗晶片,通常是去離子水。該第一清洗步驟去除重金屬離子和有機材料,例如抗蝕劑。

傳統(tǒng)上,SPM清潔劑用于去除光刻膠或重金屬離子。此時添加最終的SPM步驟并不明顯,因為這些材料已經(jīng)被去除。然而,發(fā)明人已經(jīng)發(fā)現(xiàn)-

當(dāng)使用本發(fā)明的新型預(yù)氧化工藝時,在漏電流方面獲得了驚人的顯著改善。

現(xiàn)在參考圖3,初始化學(xué)氧化物層14顯示在襯底的表面上。柵極氧化是50,以形成柵氧化層16。柵極氧化物層14和16具有約15至30埃的組合厚度。應(yīng)當(dāng)注意,附圖不是按比例繪制的。氧化物層14/16非常薄。

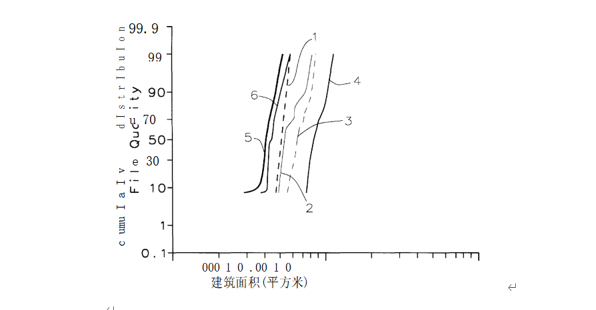

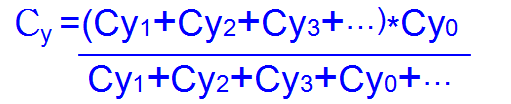

采用新型預(yù)氧化清洗工藝本發(fā)明的過程已經(jīng)被實施和測試。測試中采用了各種預(yù)氧化清洗方法。泄漏電流密度60(埃/厘米')的厚度清潔過程。圖5示出了NMOS的結(jié)果,圖6示出了PMOS的結(jié)果。在這兩個圖中,fi1m質(zhì)量的累積分布沿縱軸顯示。橫軸表示漏電流65密度。

本發(fā)明的方法(晶片號5)具有

NMOS和PMOS的最低漏電流密度值。

如本領(lǐng)域中常規(guī)的那樣繼續(xù)處理。可以在柵極氧化物層14/16上的有源區(qū)中制造半導(dǎo)體器件結(jié)構(gòu)。例如,圖4示出了具有側(cè)壁隔離物24、源區(qū)和漏區(qū)26、通過絕緣層28和鈍化層32接觸源區(qū)和漏區(qū)之一的導(dǎo)電層30的柵電極20。

本發(fā)明的方法提供了簡單的30

和降低漏電流有效方法,特別是對于超薄柵氧化層。本發(fā)明的新型氧化前清洗工藝執(zhí)行SPM清洗作為最后的清洗步驟,從而形成初始化學(xué)物質(zhì)

用鹽酸+HCO+HCO清洗;和

在每個清洗步驟之后進行HCO漂洗,其中最后的清洗步驟包括用含有HMSO和HCO的溶液進行清洗。

5.根據(jù)權(quán)利要求1的方法,其中所述化學(xué)氧化物初始層的厚度約為10-12埃。

6.根據(jù)權(quán)利要求1所述的方法,其中所述熱氧化層由包含快速熱處理和爐處理的組中的一種形成。

7.根據(jù)權(quán)利要求1的方法,其中所述熱氧化層的厚度在大約15和30埃之間。

8.根據(jù)權(quán)利要求1的方法,其中所述化學(xué)氧化物初始層和所述熱氧化物層一起具有約15至30埃的厚度。

9.一種在晶片上集成電路的制造中形成柵氧化層的方法,包括:

用多步清洗工藝清洗所述晶片的半導(dǎo)體襯底表面,包括:用HMSO+HCO溶液清洗;

用NH,O,+HCO,+HCO清洗;用鹽酸+HCO+HCO清洗;和

在每個清洗步驟之后進行HCO清洗,其中所述多步清洗工藝的最后一步包括用包含HMSO和HCO的溶液進行清洗,由此在所述晶片的所述表面上形成化學(xué)氧化物初始層;和

此后氧化所述晶片的所述表面以形成熱氧化物層,其中在所述集成電路的制造中,所述化學(xué)氧化物層和所述熱氧化物層一起形成所述柵極氧化物層。

10.根據(jù)權(quán)利要求9的方法,其中所述化學(xué)氧化物初始層的厚度在大約10和12埃之間。

11.根據(jù)權(quán)利要求9的方法,其中所述熱

形成熱柵極氧化物之前的氧化物層。化學(xué)氧化物層充當(dāng)緩沖層,以防止熱氧化期間硅表面粗糙化。

雖然已經(jīng)參照本發(fā)明的優(yōu)選實施例具體示出和描述了本發(fā)明,但是本領(lǐng)域技術(shù)人員將理解,在不脫離本發(fā)明的精神和范圍的情況下,可以進行形式和細節(jié)上的各種改變。

審核編輯:符乾江

-

芯片

+關(guān)注

關(guān)注

455文章

50721瀏覽量

423172 -

集成電路

+關(guān)注

關(guān)注

5387文章

11534瀏覽量

361650 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27295瀏覽量

218112

發(fā)布評論請先 登錄

相關(guān)推薦

MOS管泄漏電流的類型和產(chǎn)生原因

直流輸電系統(tǒng)氧化鋅ZnO電阻設(shè)計方案

電容器漏電流的產(chǎn)生原因和降低方法

金屬氧化物壓敏電阻的沖擊破壞機理&高能壓敏電阻分析

金屬氧化物壓敏電阻 (MOV) 概述:工作和應(yīng)用

MOS管中漏電流產(chǎn)生的主要六大原因

以二氧化碳為原料的清洗方式在工業(yè)中的應(yīng)用(一)

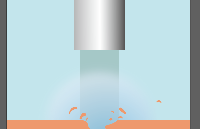

二氧化碳雪清洗技術(shù)在芯片制造中的關(guān)鍵突破

氧化誘導(dǎo)期如何檢測?

降低超薄柵氧化層漏電流的預(yù)氧化清洗方法

降低超薄柵氧化層漏電流的預(yù)氧化清洗方法

評論