芯片設計調試是一門困難的學科,而片上系統 (SoC) 設計則更是如此。這就像眾所周知的大海撈針。對于 SoC 設計,它是兩個大海撈針,一個用于軟件,另一個用于硬件。軟件開發團隊經常將集體矛頭指向硬件團隊,聲稱這是一個硬件錯誤,而硬件團隊則迅速回擊,聲稱這是一個軟件錯誤。如果沒有有效的驗證工具來查明問題,就很難知道誰是對的。這就是硬件仿真的用武之地。

硬件仿真對于調試硬件和測試 SoC 設計中硬件和軟件的集成非常重要,遠遠早于第一個芯片。當工程組的兩個不同部分(硬件設計師和軟件開發人員)使用仿真時,他們能夠共享相同的系統和設計表示。SoC 設計的組合軟件和硬件視圖使它們能夠協同工作以調試硬件和軟件交互。

作為大多數 SoC 驗證流程的基礎,硬件仿真允許工程團隊更有策略地進行規劃并實施基于多個抽象級別的調試方法。工程團隊不必彼此獨立地鉆進兩個干草堆。相反,他們可以跨嵌入式軟件和底層硬件之間的邊界跟蹤錯誤,以確定問題出在軟件還是硬件上。

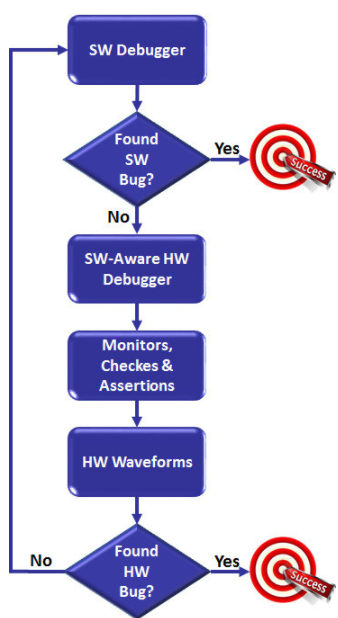

實現基于多個抽象級別的調試方法從最高級別的嵌入式軟件開始,然后在抽象級別向下移動以跟蹤各個硬件元素的行為。事實上,從包含數十億個時鐘周期的數據庫開始,軟件調試器可以將問題定位到幾百萬個時鐘周期內。在這個級別,軟件開發人員可以識別軟件代碼中的源代碼,或者他們的硬件設計同行可以使用軟件感知硬件調試方法來專注于較低的抽象級別。該方法要求通過硬件事務器實現監視器、檢查器和斷言,以避免速度下降并幫助將問題縮小到幾千個周期。

一旦審查了這兩個級別收集的數據,硬件仿真允許工程組向下移動到信號級別。它可以通過所識別時間段的寄存器傳輸電平(RTL)波形分析信息,并追蹤其可能的來源。要么發現了硬件錯誤,要么清除了硬件故障。如果是后者,它會迫使決定回到軟件環境。

導航多個級別的調試抽象

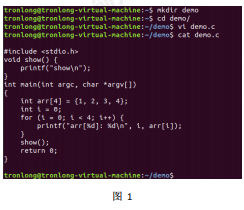

在不同的抽象級別之間導航——從軟件到硬件再到后面——避免了長時間的模擬運行和大量的詳細數據(圖 1)。

【圖1 | 硬件仿真為軟件和硬件調試提供了一個生態系統。]

軟件模擬器無法實現多級調試方法,因為它們太慢而無法有效執行嵌入式軟件。實際上,它們將運行數月來處理數十億個設計周期,這些設計的大小達到數億個專用集成電路 (ASIC) 等效門。對于消費電子設備或任何其他電子設備的供應商來說,這是一個不可接受的時間限制。

雖然仍然被廣泛使用,但在驗證場景中推動其成功的原始仿真風格的在線仿真 (ICE) 模式現在在基于事務的驗證中面臨著可行的替代方案。從概念上講,這個想法很簡單。測試是在高級抽象上編寫的,從高級命令到位級信號的轉換從測試臺轉移到稱為事務器的專用實體中。通過將事務處理器映射到硬件仿真器上,與基于仿真的驗證相比,可以輕松實現 5 或 6 個數量級的加速。

工程組使用事務處理程序來構建虛擬測試環境,而不是 ICE 物理目標系統,方法是用一組等效的事務處理程序替換一組基于 I/O 協議的速度適配器(圖 2)。

【圖2 | 一個完整的虛擬測試環境包括通過事務建模的所有 SoC 外圍接口。]

基于事務的加速簡化了設計調試。通過完全控制并非由硬件測試臺提供的設計時鐘,調試變得更加容易和高效。通過控制時鐘頻率,可以停止仿真的被測設計 (DUT) 模型、讀取其內存內容、強制某些寄存器或轉儲波形。

傳統上,在 ICE 環境中調試需要由來自目標系統的不可控時鐘驅動的硬件邏輯分析儀。該設置導致了不確定的行為并損害了調試 DUT 的能力。硬件仿真供應商最近通過將其轉換為確定性行為的方法解決了 ICE 外圍設備的隨機行為。

多層次的協同驗證視角

一旦軟件設計人員和硬件開發人員使用硬件仿真體驗了基于事務的驗證,他們的整個驗證視角就會發生變化。無需繁瑣的 ICE 硬件即可快速設置強大的測試環境的能力意味著更容易和更有效的調試。目標可能是相同的——在更短的時間內做出更好的設計——但現在的體驗可能會變得不那么具有挑戰性。

工程團隊發現現代硬件仿真器是測試硬件和在 SoC 設計中集成硬件和軟件的必要條件。它使他們能夠更有策略地進行規劃并成功實施硬件/軟件聯合驗證。

審核編輯:郭婷

-

寄存器

+關注

關注

31文章

5336瀏覽量

120260 -

soc

+關注

關注

38文章

4163瀏覽量

218176 -

仿真器

+關注

關注

14文章

1017瀏覽量

83727

發布評論請先 登錄

相關推薦

單片機Debug與仿真區別

自動控制系統的調試方法 自動控制系統與傳統控制系統的比較

用OPA340仿真出來的效果和硬件調試基本相符,二倍時150K增益開始下降,為什么?

【干貨分享】硬件在環仿真(HiL)測試

上海 10月25日-26日《硬件電路設計、調試與工程案例分析》公開課即將開始!

多級調試方法的硬件仿真

多級調試方法的硬件仿真

評論