在新的電力電子時代,更高功率的開關被集成到大型片上系統 (SoC) 設計中,傳統方法正被更復雜的結構所取代。這不可避免地增加了設計的復雜性,在這里,下一代仿真工具可以幫助設計人員更詳細、更準確地預測系統、RTL 和門級的功耗。

FinFET工藝技術的出現,帶來了靜態泄漏的重大改進;然而,動態功率仍然是智能設備和數據中心芯片的主要關注點。因此,一種新模型正在出現,它在仿真期間繪制開關活動并將信息傳遞給功率分析工具。

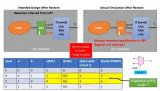

1. 傳統的功率分析包括分兩步執行的基于文件的流程。

傳統的功耗估計方法采用基于文件的流程,該流程被饋送到功耗分析工具中。模擬器或仿真器以開關活動交換格式 (SAIF) 文件或信號數據庫文件(如 FSDB 或 VCD)跟蹤開關活動。這些文件被饋送到功率估計工具,以找出平均和峰值功率使用。

這種方法適用于具有幾百萬門的較小芯片,但對于較大的 SoC 設計,文件變得難以管理。因此,功耗估算工具讀取和處理這些文件需要很長時間,有時無法處理大文件。

替換基于文件的流程

Mentor Graphics 的 Veloce 仿真系統使工程師能夠準確預測大型芯片的功耗,首先消除基于文件的兩步流程,然后將仿真器與功耗分析工具緊密集成。

Veloce 電源應用程序(在實際操作系統和應用程序行為的幫助下)識別并縮放產生功率峰值的開關活動。它甚至包括識別可能威脅電源設計的開關活動時間框架。與基于文件的功率圖表(可能需要一周多的時間才能生成 1 億門設計的活動圖)不同,Veloce 只需 15 分鐘即可完成任務。

電源設計的下一階段是找出這些峰值在芯片設計中出現的位置以及導致它們的原因。輸入動態讀取波形API,它將當前基于 SAIF/FSDB/VCD 文件的方法替換為從仿真器到功率估計工具的實時流式切換數據。開關數據直接提供給功率分析工具(Ansys 的 PowerArtist),而不是通過文件傳遞。

2. Mentor 的 Veloce 仿真器通過將動態讀取波形 API 與功率分析工具集成,提供準確的門級功率分析。

總體而言,Veloce 電源應用程序和動態讀取波形 API 有助于在系統級別進行更高效的電源分析,這是基于文件的流程無法實現的。恰當的例子:Veloce 仿真器與功耗分析運行時集成的早期用戶見證了 5 到 10 倍的性能提升。這很強大。

審核編輯:郭婷

-

soc

+關注

關注

38文章

4193瀏覽量

218695 -

仿真器

+關注

關注

14文章

1019瀏覽量

83865 -

API

+關注

關注

2文章

1509瀏覽量

62246

發布評論請先 登錄

相關推薦

模擬IC設計中Spectre和HSPICE仿真工具的起源、差別和優劣勢

車載總線監控分析及仿真工具 - VBA

soc設計中的熱管理技巧

SOC芯片在汽車電子中的應用

低功耗SOC芯片的優勢

AM62A Edge AI零售掃描儀演示:SoC選型和功耗分析

multisim中邏輯分析儀怎么連接

SoC布局中各種IC簡介

低功耗藍牙 SoC 16 站點生產線工具套件DA14580PRODTLKT數據手冊

SOC設計中Clock Gating的基本原理與應用講解

演進中的電力電子設計:安森美先進仿真工具

分享一種大型SOC設計中功能ECO加速的解決方案

仿真工具重振大型SoC中的功耗分析

仿真工具重振大型SoC中的功耗分析

評論