對于許多芯片設計驗證工程師來說,VIP 很容易代表非常重要的財產,而不是驗證知識產權 (VIP)。

VIP 被認為是驗證方法的重要組成部分,因為它描述了可重復使用的驗證組件庫和預定義的功能塊,有助于驗證片上系統 (SoC) 設計中的復雜接口和協議的正確性。涵蓋 MIPI、SerDes、汽車、內存模型、網絡、存儲和視頻的字母表,它們消除了對多種協議專家的需求,因為他們根據協議規范的細節驗證設計。在此過程中,它們改進了調試、質量和覆蓋范圍,加速了項目交付,增加了投資回報并降低了硅片重新設計的風險。

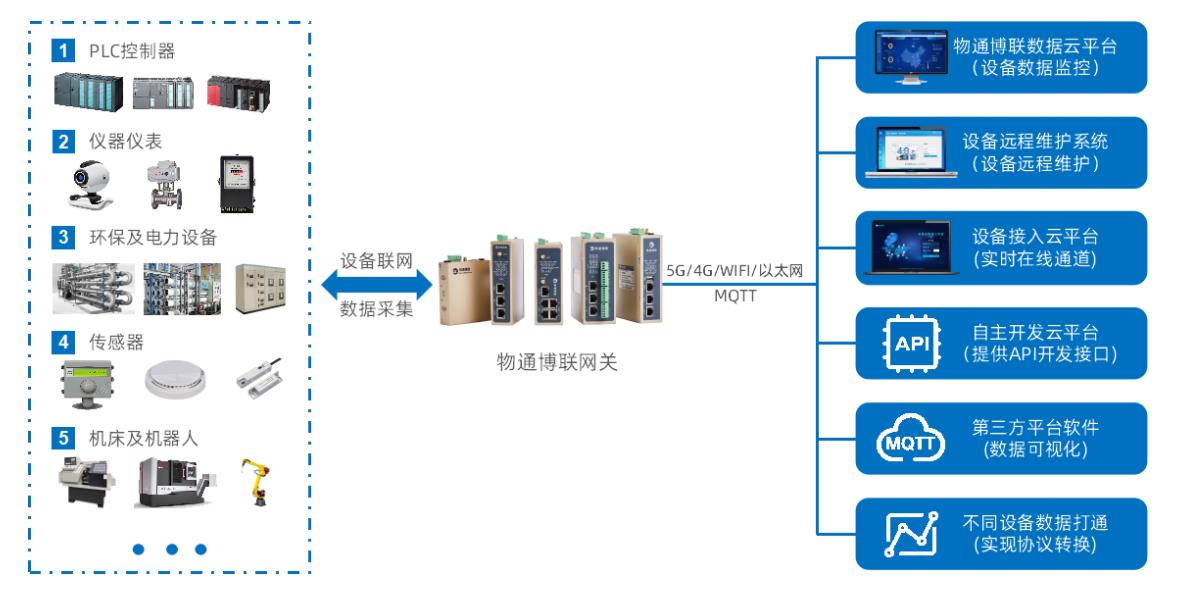

復雜 SoC 的測試平臺需要各種 VIP 模塊來驗證系統級功能并通過生成特定于應用程序的流量和檢查器來驗證目標性能。模塊被插入到測試臺中,用于設計檢查協議和接口的操作,無論是離散的還是組合的。它們使驗證工程師能夠檢查基本功能,例如系統啟動或更詳細的探索。由于設計復雜性不斷增加,這一點變得越來越重要。它們生成測試來刺激和驗證不同的接口和標準總線協議,例如事務/序列、驅動程序和配置組件。特定接口和測試套件的測試計劃連接到測試臺內的被測/驗證設計 (DUT),以模擬或仿真 IP 或 SoC 設計。

雖然 VIP 是一種經過驗證且值得信賴的驗證商品,但它不是一種驗證方法,與通用驗證方法 (UVM)、用于構建測試平臺的 Accellera 互操作性標準或開放驗證方法 (OVM)、方法和模塊庫不同。他們創建了一個基礎架構來支持行業標準接口硬件驗證語言 (HVL)、SystemVerilog 和 SystemC 以及方法、UVM 和 OVM。VIP 是符合行業標準的即插即用模塊,具有特定用途:驗證系統級功能并驗證目標性能,同時支持所有流行的驗證方法平臺。

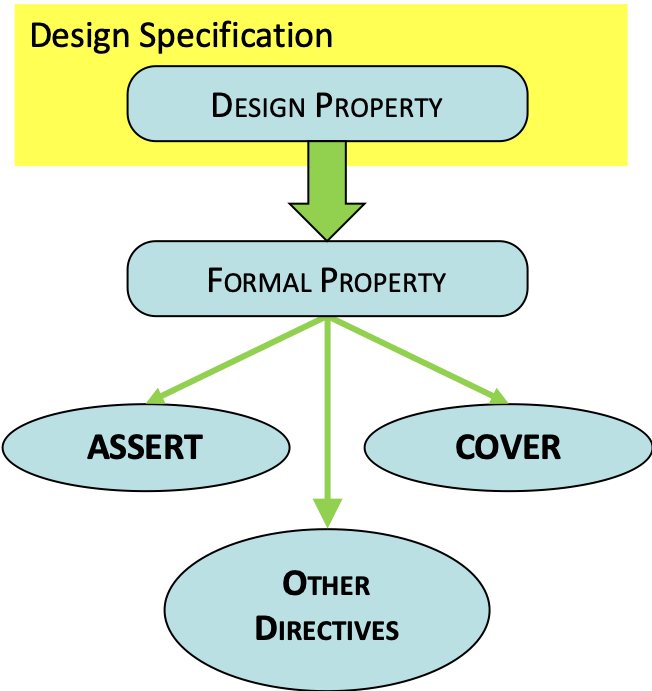

驗證工程師指出需要在良好集成的流程中實現全面的代碼覆蓋和功能覆蓋。VIP 支持無縫的覆蓋驅動驗證流程,在模擬、仿真或形式驗證之間沒有覆蓋差距。它可用于設計流程中的多個階段,并可供設計項目的多個供應商使用。

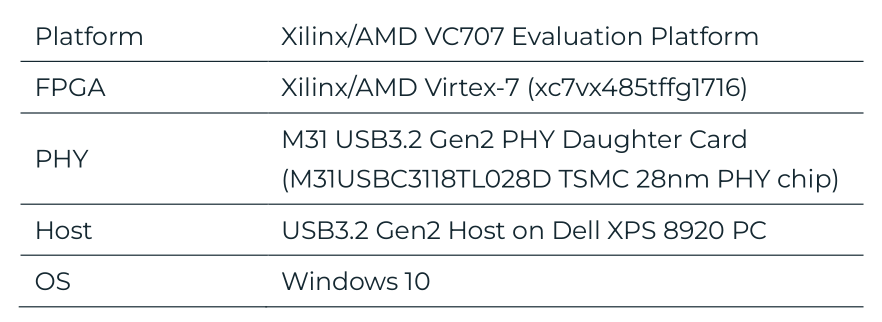

例如,用于仿真和 FPGA 原型設計的 VIP 塊以可綜合寄存器傳輸級 (RTL) 代碼的形式出現。完全的 API 兼容性將設計從模擬轉移到仿真。這些 VIP 模塊包括內置智能調試器,提供快速編譯和系統級仿真運行時間以及快速固件/軟件開發。基礎設施框架或測試平臺帶有激勵生成器、監視器、記分板/檢查器和功能覆蓋模型。

在仿真平臺中,VIP 不應與特定的仿真器綁定。在仿真平臺中,不應將 VIP 綁定到仿真器。同樣,VIP 不應與特定的正式

引擎。對于理想的設計,VIP 需要與平臺無關,甚至在平臺內,驗證引擎也需要與驗證引擎無關,以便驗證工程師無縫地從一個平臺遷移到另一個平臺,而不會在此過程中產生任何開銷。

無論是非常重要的財產還是驗證知識產權,驗證小組都將這些模塊用作其驗證策略的一部分,并將 VIP 視為芯片設計驗證流程的重要組成部分。

審核編輯:郭婷

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603977 -

soc

+關注

關注

38文章

4173瀏覽量

218424 -

仿真器

+關注

關注

14文章

1018瀏覽量

83790

發布評論請先 登錄

相關推薦

數字芯片設計驗證經驗分享文章 實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼

工業物聯網系統的組成部分

物聯網泵房的功能和組成部分

嵌入式系統的硬件組成部分

新思科技PCIe 7.0驗證IP(VIP)的特性

機器學習中的交叉驗證方法

大規模 SoC 原型驗證面臨哪些技術挑戰?

驗證IP:芯片設計驗證的重要組成部分

驗證IP:芯片設計驗證的重要組成部分

評論