SystemVerilog的RTL綜合子集

SystemVerilog既是一種硬件設(shè)計(jì)語言,也是一種硬件驗(yàn)證語言。IEEE SystemVerilog官方標(biāo)準(zhǔn)沒有區(qū)分這兩個(gè)目標(biāo),也沒有指定完整SystemVerilog語言的可綜合子集。相反,IEEE讓提供RTL綜合編譯器的公司來定義特定產(chǎn)品支持哪些SystemVerilog語言結(jié)構(gòu)。

由于缺乏SystemVerilog綜合標(biāo)準(zhǔn),每個(gè)綜合編譯器可能支持SystemVerilog標(biāo)準(zhǔn)的不同子集。這意味著設(shè)計(jì)工程師在編寫用于綜合的SV模型時(shí)需要小心。必須參考要使用的綜合編譯器的文檔,并遵循為一個(gè)綜合編譯器編寫的編譯器模型的語言子集,使用不同的綜合編譯器可能需要根據(jù)綜合器特性進(jìn)行修改。

接下來看下今天的主角-FPGA建模概念

FPGA的建模

本文的目的是了解SystemVerilog建模風(fēng)格如何受到ASIC和FPGA技術(shù)的影響。有關(guān)ASIC和FPGA實(shí)現(xiàn)的詳細(xì)信息以及這些技術(shù)的適當(dāng)應(yīng)用留給其他工程書籍討論。然而,為了實(shí)現(xiàn)RTL建模最佳實(shí)踐的目標(biāo),理解ASIC和FPGA的基本概念非常重要。

標(biāo)準(zhǔn)單元ASICASIC是專用集成電路的縮寫。與可執(zhí)行多種功能(如微處理器)的通用IC不同,ASIC設(shè)計(jì)用于執(zhí)行特定任務(wù)(因此得名為“application specific”)。控制器、音頻格式轉(zhuǎn)換和視頻處理是適用于ASIC的示例。ASIC還可以包括一個(gè)或多個(gè)嵌入式處理器,以便執(zhí)行特定任務(wù)同時(shí)可以進(jìn)行通用操作。帶有嵌入式處理器的ASIC通常被稱為片上系統(tǒng)(SoC,主流設(shè)計(jì))。

提供ASIC的公司稱為ASIC供應(yīng)商(ASIC vendors)。其中一些供應(yīng)商提供ASIC技術(shù)并進(jìn)行ICs實(shí)際制造和生產(chǎn)的一部分。其他ASIC供應(yīng)商為ASIC提供技術(shù),但將制造和生產(chǎn)留給其他公司。

大多數(shù)ASIC技術(shù)使用標(biāo)準(zhǔn)單元(standard cells),這些單元是預(yù)先設(shè)計(jì)的邏輯塊,由一到幾個(gè)邏輯門組成。ASIC單元庫可能有幾百個(gè)標(biāo)準(zhǔn)單元,如AND、NAND、OR、NOR、Exclusive-OR, Exclusive-NOR,2-to-l MUX- 2選1 MUX、D型觸發(fā)器、鎖存器等。每個(gè)單元都有明確的電氣特性,如傳播延遲、建立和保持時(shí)間以及寄生電容。

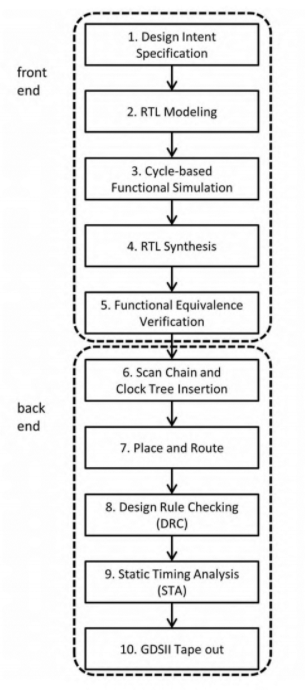

設(shè)計(jì)ASIC涉及從庫中選擇合適的單元,并將它們連接在一起以執(zhí)行所需的功能。在整個(gè)過程中使用EDA軟件工具進(jìn)行設(shè)計(jì)。ASIC設(shè)計(jì)的典型流程如圖1-5所示:

圖1-5:典型的基于RTL的ASIC設(shè)計(jì)流程

圖1-5所示的步驟是:

1、當(dāng)然,第一步是說明設(shè)計(jì)的意圖。

2、所需的功能在抽象的RTL建模級(jí)別進(jìn)行建模。在這個(gè)階段,重點(diǎn)是功能,而不是物理實(shí)現(xiàn)。

3、仿真并驗(yàn)證功能。

4、綜合,將RTL功能映射到適合目標(biāo)ASIC類型的標(biāo)準(zhǔn)單元。綜合的輸出稱為門級(jí)網(wǎng)表(gate-level netlist),該綜合過程在后面有更詳細(xì)的描述。

5、仿真或邏輯等價(jià)檢查器(Logic Equivalence Checkers)(形式驗(yàn)證的一種形式)用于驗(yàn)證門級(jí)實(shí)現(xiàn)在功能上等同于RTL功能。

6、時(shí)鐘樹合成用于在整個(gè)設(shè)計(jì)中均勻分布時(shí)鐘驅(qū)動(dòng)。通常,掃描鏈插入到工具中以增加設(shè)計(jì)的可測(cè)試性。

7、Place and route(放置和布線)軟件計(jì)算如何在實(shí)際硅中布局,以及如何布線。place and route軟件的輸出是一個(gè)圖形數(shù)據(jù)系統(tǒng)文件(GDSII,發(fā)音為gee dee ess two)。GDSII是一種二進(jìn)制格式,其中包含有關(guān)實(shí)際在硅中構(gòu)建IC所需的幾何形狀(多邊形polygons)和其他數(shù)據(jù)的信息。

8、進(jìn)行設(shè)計(jì)規(guī)則檢查(DRC),以確保ASIC制造廠定義的所有規(guī)則均得到遵守,如加載門扇出,

9、在考慮互連網(wǎng)絡(luò)和時(shí)鐘樹傾斜的延遲效應(yīng)后,執(zhí)行靜態(tài)時(shí)序分析(STA)以確保滿足建立/保持時(shí)間。

10、最后一步是將GDSII文件和其他數(shù)據(jù)發(fā)送給制造廠,用于制造ASIC。將這些文件傳遞給制造廠被稱為“taping out”ASIC,因?yàn)樵贏SIC設(shè)計(jì)的早期,是使用磁帶將這些文件發(fā)送給鑄造廠:

在本文中,ASIC設(shè)計(jì)流程中的這些步驟已被概括。有許多細(xì)節(jié)被遺漏了,并不是所有的公司都遵循這個(gè)確切的流程。有時(shí),步驟9(靜態(tài)時(shí)序分析)在設(shè)計(jì)流程的早期執(zhí)行,并且可能在流程中執(zhí)行多次。

本文的重點(diǎn)是用于仿真和合成的RTL建模,圖1-5中的步驟2和步驟3。此級(jí)別的建模處于設(shè)計(jì)過程的前端。時(shí)鐘樹、掃描鏈和時(shí)序分析等設(shè)計(jì)細(xì)節(jié)將在設(shè)計(jì)流程的后面介紹,不在本文的范圍之內(nèi)。在RTL級(jí)別,設(shè)計(jì)工程師專注于實(shí)現(xiàn)所需的功能;而不是實(shí)施細(xì)節(jié)。然而,理解在建模、仿真和合成的前端步驟之后會(huì)發(fā)生什么仍然很重要。RTL編碼風(fēng)格會(huì)影響設(shè)計(jì)流程中后期使用的工具的有效性。

還有其他類型的ASIC技術(shù)不使用標(biāo)準(zhǔn)單元,如全定制、門陣列和結(jié)構(gòu)化ASIC。SystemVerilog可以以類似的方式用于設(shè)計(jì)這些其他類型的ASIC,盡管所涉及的軟件工具可能有所不同。所使用的綜合編譯器——以及這些編譯器支持的SystemVerilog語言結(jié)構(gòu)——可能與這些其他技術(shù)非常不同。

FPGAFPGA是現(xiàn)場可編程門陣列(Field Programmable Gate Array)的縮寫。FPGA是一種集成電路,包含固定數(shù)量的邏輯塊,可在IC制造后進(jìn)行重新配置(而ASIC的內(nèi)容和布局必須在制造前確定)。從歷史上看,F(xiàn)PGA不能包含ASIC那么多的功能,只能以較慢的時(shí)鐘速度運(yùn)行,這是RTL級(jí)設(shè)計(jì)時(shí)的重要考慮因素。FPGA技術(shù)的最新進(jìn)展顯著縮小了FPGA和ASIC之間的差異。通常,F(xiàn)PGA可用于實(shí)現(xiàn)與ASIC相同的功能。

FPGA包含一系列稱為可配置邏輯塊(CLB)的小型邏輯元件。一些FPGA供應(yīng)商將這些塊稱為邏輯陣列塊(LABs)。典型的CLB可能包含一個(gè)或多個(gè)查找表(LUT)、一些多路復(fù)用器(MUX)和存儲(chǔ)元件(如D型觸發(fā)器)。大多數(shù)FPGA中的查找表都是用邏輯運(yùn)算(如AND、OR和XOR)編程的小型RAM。從LUT中選擇所需的操作允許以多種方式使用CLB,從簡單的AND或XOR門到更復(fù)雜的組合功能。某些FPGA中的CLB還可能具有其他功能,例如加法器。MUX允許組合結(jié)果直接從CLB輸出(異步輸出),或在存儲(chǔ)單元中輸出(同步輸出)。

FPGA使用包含數(shù)百或數(shù)千個(gè)CLB的陣列進(jìn)行制造,以及可“編程”到所需CLB配置的可配置互連-FPGA還包含I/O焊盤,可配置為連接到CLB陣列的一列或一行。

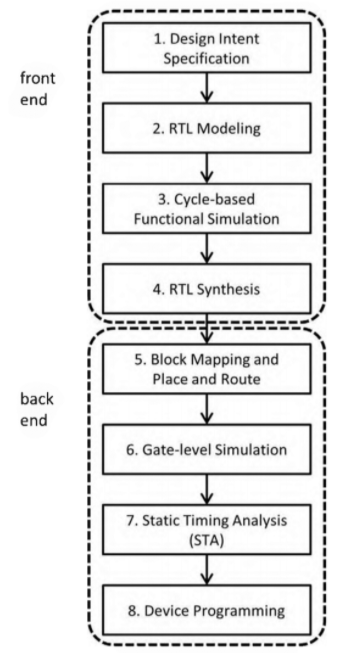

復(fù)雜FPGA的典型設(shè)計(jì)流程如圖1-6所示。

圖1-6:典型的基于RTL的FPGA設(shè)計(jì)

FPGA的前端設(shè)計(jì)流程類似于ASIC,但后端不同。FPGA的后端部分與ASIC的主要區(qū)別在于FPGA的布局和布線。對(duì)于ASIC,place and route軟件決定IC的制造方式。對(duì)于FPGA,綜合和布局布線軟件詳細(xì)說明了如何對(duì)FPGA進(jìn)行編程。本文重點(diǎn)介紹前端步驟2和3,RTL建模和仿真,其中ASIC和FPGA設(shè)計(jì)之間幾乎沒有區(qū)別。

ASIC和FPGA的RTL編碼樣式

理想情況下,相同的RTL代碼可以同時(shí)用于ASIC或FPGA。在“RTL級(jí)別”工作時(shí),工程重點(diǎn)是設(shè)計(jì)和驗(yàn)證功能,而不必關(guān)心實(shí)施細(xì)節(jié)。綜合編譯器的作用是將RTL功能映射到特定的ASIC或FPGA技術(shù)。

對(duì)于ASIC和FPGA來說,大多數(shù)(但不是全部)RTL代碼都能很好地綜合。然而,這種普遍性也有例外。RTL模型的一些方面需要考慮設(shè)計(jì)是在ASIC還是FPGA中進(jìn)行綜合,這些方面包括:

復(fù)位。大多數(shù)ASIC單元庫包括同步和異步復(fù)位觸發(fā)器。設(shè)計(jì)工程師可以使用被認(rèn)為最適合設(shè)計(jì)的復(fù)位類型來編寫RTL模型,一些FPGA沒有那么靈活,只有一種復(fù)位類型的觸發(fā)器(通常是同步的)。雖然綜合編譯器可以將帶有異步復(fù)位的RTL模型映射到門級(jí)同步復(fù)位中,或者反之亦然,但需要額外的邏輯門。許多FPGA還支持ASIC不具備的全局復(fù)位功能和預(yù)置上電上電觸發(fā)器的狀態(tài)。后面會(huì)更詳細(xì)地討論復(fù)位建模。

向量/矢量大小。ASIC在最大矢量寬度和矢量運(yùn)算方面基本不受限制。在大向量上進(jìn)行復(fù)雜操作需要大量邏輯門,但大多數(shù)ASIC中使用的標(biāo)準(zhǔn)單元架構(gòu)可以適應(yīng)這些操作。FPGA在這方面比較嚴(yán)格。由于可用CLB的數(shù)量或CLB之間互連路由的復(fù)雜性,預(yù)定義的CLB數(shù)量及其在FPGA中的位置可能會(huì)限制在非常大的向量上實(shí)現(xiàn)復(fù)雜操作的能力。ASIC和FPGA之間的這種差異意味著,即使在RTL抽象級(jí)別,設(shè)計(jì)工程師也必須牢記設(shè)計(jì)的功能會(huì)受到設(shè)備的限制。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602994 -

asic

+關(guān)注

關(guān)注

34文章

1199瀏覽量

120436

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

典型的基于RTL的ASIC設(shè)計(jì)流程分析

典型的基于RTL的ASIC設(shè)計(jì)流程分析

評(píng)論