RISC-V 被稱(chēng)為開(kāi)放標(biāo)準(zhǔn)指令集架構(gòu) (ISA),其基本指令已被凍結(jié)以最小化復(fù)雜性。但最近它添加了廣泛的自定義擴(kuò)展和增強(qiáng)功能,使其在構(gòu)建特定應(yīng)用系統(tǒng)的 SoC 設(shè)計(jì)人員中越來(lái)越受歡迎。

這些架構(gòu)中采用的定制功能通常通過(guò)硬件/軟件協(xié)同設(shè)計(jì)策略得到增強(qiáng),該策略優(yōu)化軟件以最大限度地發(fā)揮 RISC-V 處理器 IP 的專(zhuān)業(yè)能力。

但無(wú)論系統(tǒng)是否在軟硬件協(xié)同設(shè)計(jì)環(huán)境中開(kāi)發(fā),構(gòu)建穩(wěn)定的 SoC 設(shè)計(jì)和驗(yàn)證流程的過(guò)程仍然涉及大量設(shè)置和耗時(shí)的手動(dòng)更改。研究估計(jì) SoC 驗(yàn)證占用了 SoC 總設(shè)計(jì)時(shí)間和成本的 50-80%,而且使用 RISC-V 處理器的驗(yàn)證工程師的工作量比 Arm SoC 還要多,因?yàn)?CPU 本身以及任何定制都必須經(jīng)過(guò)驗(yàn)證。

RISC-硬件設(shè)計(jì)驗(yàn)證提供商 Imperas 最近的一份聲明稱(chēng):“開(kāi)源 IP 的日益普及也促進(jìn)了將驗(yàn)證作為 SoC 項(xiàng)目初始階段的傳入質(zhì)量檢查的團(tuán)隊(duì)的增長(zhǎng)。” V 處理器模型和用于軟件仿真的虛擬原型,讀取。“此外,修改或擴(kuò)展基本核心功能的設(shè)計(jì)選項(xiàng)從一開(kāi)始就取決于一個(gè)有效的設(shè)計(jì)驗(yàn)證框架。”

圍繞可定制的 RISC-V IP 規(guī)范化驗(yàn)證

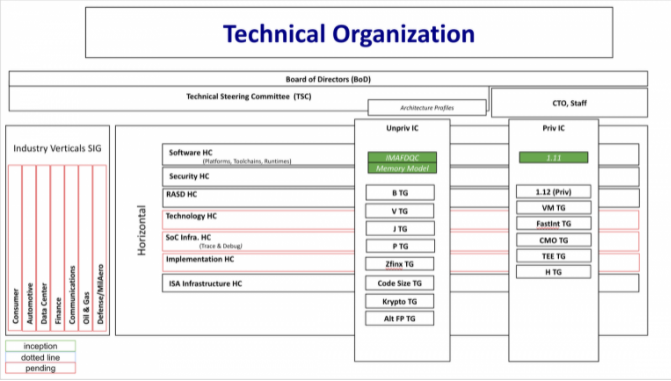

事實(shí)上,隨著 RISC-V 的成熟,越來(lái)越多的設(shè)計(jì)團(tuán)隊(duì)選擇“修改或擴(kuò)展基本核心功能”,以至于 RISC-V 基金會(huì)已經(jīng)組織了特殊興趣小組來(lái)規(guī)范目標(biāo)用例的擴(kuò)展功能集。這些工作組可以在下圖的左側(cè)看到,自春季發(fā)布該表以來(lái),其中許多已經(jīng)從待處理轉(zhuǎn)變?yōu)榛顒?dòng)。

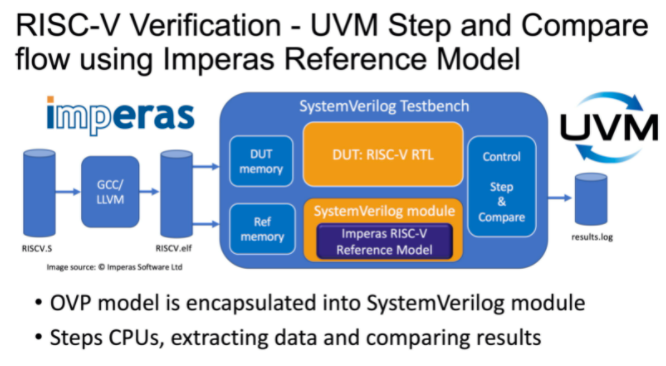

作為回應(yīng),ImperasDV 工具正在尋求通過(guò)與當(dāng)前 UVM SystemVerilog 技術(shù)兼容的“黃金參考模型”來(lái)簡(jiǎn)化 RISC-V SoC 設(shè)計(jì)驗(yàn)證過(guò)程。它的環(huán)境采用鎖步比較設(shè)計(jì)驗(yàn)證方法,允許在 Verilog 或 SystemVerilog 中編程的被測(cè)設(shè)備 (DUT) 運(yùn)行和構(gòu)建裝配級(jí)程序。這有助于解決異步事件,從而在發(fā)現(xiàn)錯(cuò)誤時(shí)減少調(diào)試分析時(shí)間。

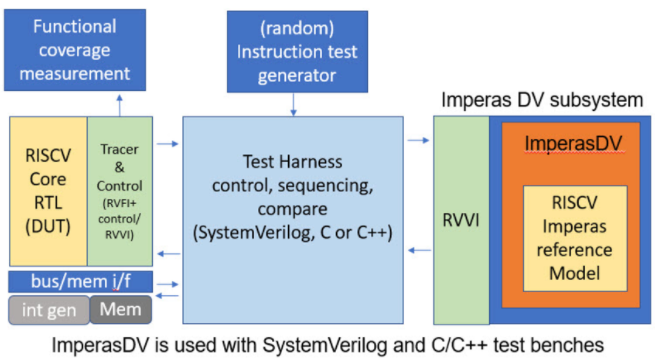

該工具的主要組成部分是:

指令測(cè)試生成器

RTL DUT 子系統(tǒng)

功能覆蓋測(cè)量

測(cè)試臺(tái)/線束

命令 DV 子系統(tǒng)

該工具的外殼可容納整個(gè) RISC-V ISA,包括特權(quán)操作模式,并與最新的 Vector、DSP/SIMD、Bitmanip 和 Crypto (Scalar) 擴(kuò)展兼容。從架構(gòu)的角度來(lái)看,ImperasDV 提供了一個(gè)支持 RISC-V 驗(yàn)證接口 (RVVI) 標(biāo)準(zhǔn)的驗(yàn)證環(huán)境。這簡(jiǎn)化了客戶 RTL、參考模型和測(cè)試平臺(tái)之間的集成。

如前所述,該集成有助于復(fù)雜超標(biāo)量流水線的鎖步和比較驗(yàn)證,并且該平臺(tái)可以容納多個(gè)硬件線程并完成無(wú)序指令。Imperas 的黃金參考模型確保平臺(tái)評(píng)估的操作數(shù)據(jù)正確執(zhí)行,即使跨不同版本,這要?dú)w功于對(duì)特定修訂的可配置版本控制支持。

開(kāi)源協(xié)同設(shè)計(jì)現(xiàn)在開(kāi)始

ImperasDV RISC-V 驗(yàn)證工具鏈已被許多半導(dǎo)體行業(yè)領(lǐng)先的 RISC-V 供應(yīng)商采用,其中一些供應(yīng)商已經(jīng)擁有可工作的硅原型,目前正在開(kāi)展第二代設(shè)計(jì)。其中包括 Codasip、EM Microelectronics (Swatch)、NSITEXE (Denso)、Nvidia Networking (Mellanox)、OpenHW Group、MIPS Technology、Seagate Technology、Silicon Labs 和 Valtrix Systems,以及其他尚未公開(kāi)的公司。

當(dāng)然,我們還沒(méi)有解決硬件/軟件協(xié)同設(shè)計(jì)等式的另一面:嵌入式軟件開(kāi)發(fā)。在這里,Imperas 還通過(guò)建模和仿真解決方案加快設(shè)計(jì)周期,只是這些解決方案基于開(kāi)源開(kāi)放虛擬平臺(tái) (OVP) 模型。

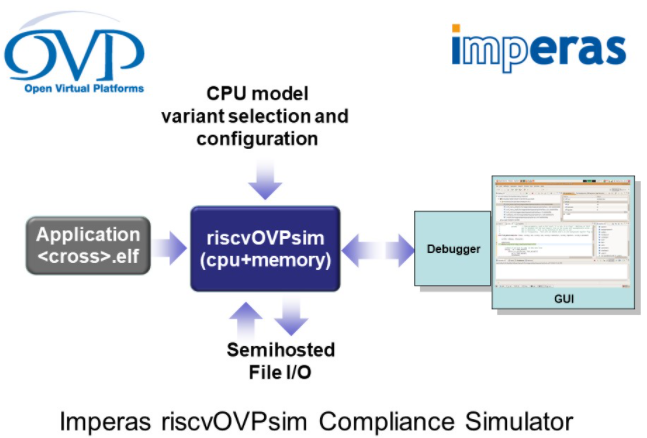

該公司的riscvOVPsim 指令集模擬器 (ISS)允許以高達(dá) 1,000 MIPS 的速度開(kāi)發(fā)和調(diào)試針對(duì) RISC-V 處理器目標(biāo)的代碼。它利用 Imperas 的 OVP 快速處理器模型庫(kù)來(lái)提供指令精確的單核 RISC-V 配置和變體,甚至被 RISC-V 基金會(huì)的合規(guī)性框架和測(cè)試套件使用。

最重要的是,可以從 GitHub 免費(fèi)下載riscvOVPsim,并且可以在www.ovpworld.org/riscvOVPsimPlus找到包含新 RISC-V 矢量擴(kuò)展的增強(qiáng)測(cè)試套件。

riscvOVPsim 的可用升級(jí)包括虛擬平臺(tái)開(kāi)發(fā)和仿真、多核軟件開(kāi)發(fā)、可擴(kuò)展平臺(tái)套件和多處理器主機(jī) (MPonMP) 加速軟件上的 QuantumLeap 多處理器目標(biāo)。

Imperas 產(chǎn)品組合以及來(lái)自快速發(fā)展的 RISC-V 生態(tài)系統(tǒng)的其他工具,為您今天開(kāi)始自己的開(kāi)放式處理器設(shè)計(jì)提供了足夠的資源。

作者:Brandon Lewis,Saumitra Jagdale

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229657 -

soc

+關(guān)注

關(guān)注

38文章

4163瀏覽量

218169 -

仿真

+關(guān)注

關(guān)注

50文章

4071瀏覽量

133552

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Rivos全新產(chǎn)品采用Andes晶心科技NX45 RISC-V處理器

《RISC-V能否復(fù)制Linux 的成功?》

RISC-V,即將進(jìn)入應(yīng)用的爆發(fā)期

risc-v在人工智能圖像處理應(yīng)用前景分析

RISC-V適合什么樣的應(yīng)用場(chǎng)景

RISC-V在中國(guó)的發(fā)展機(jī)遇有哪些場(chǎng)景?

淺析RISC-V領(lǐng)先ARM的優(yōu)勢(shì)

請(qǐng)問(wèn)ESP32s3 ULP RISC-V協(xié)處理器是否支持ADC的讀取?

RISC-V有哪些優(yōu)點(diǎn)和缺點(diǎn)

RISC-V有哪些優(yōu)缺點(diǎn)?是堅(jiān)持ARM方向還是投入risc-V的懷抱?

Achronix FPGA增加對(duì)Bluespec提供的基于Linux的RISC-V軟處理器的支持,以實(shí)現(xiàn)可擴(kuò)展數(shù)據(jù)處理

淺談RISC-V微架構(gòu)驗(yàn)證方式

fpga和risc-v處理器的區(qū)別

芯來(lái)科技正式發(fā)布基于RISC-V處理器的HSM子系統(tǒng)解決方案

定制RISC-V處理器簡(jiǎn)化設(shè)計(jì)驗(yàn)證

定制RISC-V處理器簡(jiǎn)化設(shè)計(jì)驗(yàn)證

評(píng)論