| $unit是一個危險的共享名稱空間,充滿危險。它的使用會導致設計難以編譯和維護。 |

| 下列unit代表$unit |

| 筆記 |

|---|

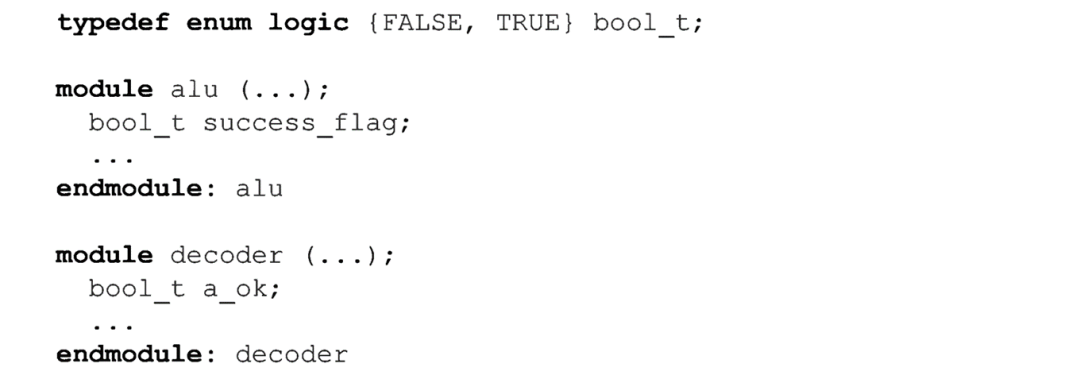

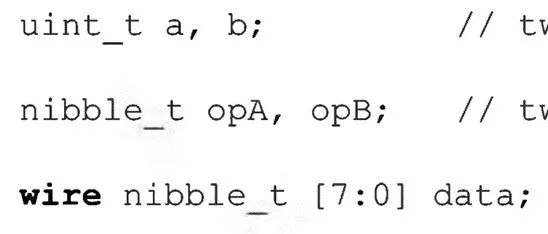

在將包添加到SystemVerilog標準之前,SV提供了一種不同的機制來創建多個模塊共享的定義。這個機制是一個名為unit的偽全局名稱空間,也稱unit 編譯單元或聲明空間。聲明空間之外的任何聲明都在unit聲明空間中。在下面的示例中,bool_t的定義在兩個模塊之外,因此在unit聲明空間中。

unit聲明空間可以包含與包相同類型的用戶定義,并且具有相同的綜合限制。然而,與包不同的是,unit聲明空間可能導致設計代碼難以維護,EDA也難以編譯。使用unit的一些危險包括

以unit聲明空間的定義可能分散在許多文件中,使代碼維護和代碼重用成為一場噩夢,當引用包中用戶自定義類型、任務、函數或其他標識符名稱時,相對容易找到和維護標識符名稱的定義。總是有一個顯式的包引用或包導入語句來顯示在哪里可以找到定義。當在unit聲明空間中定義了用戶自定義類型、任務、函數或其他標識符時,該定義可以位于構成設計和驗證測試臺源代碼的任何文件、任何目錄、任何服務器中。定位、維護和重新定義是困難的。

當unit聲明空間中的定義位于多個文件中時,必須按照特定的順序編譯這些文件。

SystemVerilog要求在引用定義之前對其進行編譯。當unit聲明分散在許多文件中時,按照正確的順序編譯所有文件可能會很困難,甚至是不可能的。

更改unit定義需要重新編譯所有源代碼文件。

對unit聲明空間中定義的任何更改都需要重新編譯構成設計和驗證測試臺的所有源代碼,因為任何地方的任何文件都可以無需導入地使用該定義。許多軟件工具不會強制要求重新編譯所有文件,但如果不重新編譯,設計模塊最終可能使用過時的定義。

對于仿真和綜合,unit聲明空間可以是相同,但通常是不同的。

編譯器的每次調用都會啟動一個新的unit聲明空間,該空間不共享其他unit聲明空間中的聲明。許多SystemVerilog仿真器一起編譯多個文件。這些工具將看到一個unit空間。一個文件中的unit定義對于單個編譯中的任何后續文件都是可見的。大多數SystemVerilog綜合編譯器和一些仿真器都支持單獨的文件編譯,每個文件都可以獨立編譯。這些工具將看到幾個斷開連接的unit聲明空間。一個文件中的unit定義對任何其他文件都不可見。

很容易出現定義不同的重復標識符名稱。

在SystemVerilog中,在同一名稱空間中多次定義同一名稱是非法的。如果一個文件在unit聲明空間中定義了bool_t用戶自定義類型,而另一個文件在unit聲明空間中也定義了bool_t用戶自定義類型,那么這兩個文件永遠不能一起編譯,因為這兩個定義最終會在相同的unit空間中結束。為了避免這種沖突,工程師必須使用’define 和 ’ifdef添加條件編譯指令,以便只編譯編譯器遇到的第一個定義。

包可以導入到unit中,但其危害與直接在unit中定義的危害相同。此外,必須注意不要將同一個包多次導入同一unit聲明空間,這是非法的。

| 避免像Bubonic plague一樣使用$unit!相反,使用包來共享定義。 |

| 包避免了$unit的所有危害,包提供了一個易于維護和重用的受控聲明空間。 |

| 最佳實踐指南4-2 |

|---|

審核編輯 :李倩

-

模塊

+關注

關注

7文章

2789瀏覽量

50510 -

Verilog

+關注

關注

29文章

1367瀏覽量

112350 -

編譯

+關注

關注

0文章

679瀏覽量

34082

原文標題:SystemVerilog(十二)-$unit聲明空間

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PanDao應用:輸入中頻空間公差,最小中頻波長

嵌入式學習-飛凌嵌入式ElfBoard ELF 1板卡-內核空間與用戶空間的數據拷貝之數據拷貝介紹

飛凌嵌入式ElfBoard ELF 1板卡-內核空間與用戶空間的數據拷貝之數據拷貝介紹

LBE大空間火熱,如何落地文旅場景?

大疆發布DJI O4 Air Unit系列:圖傳性能再升級

聲明式資源管理方法

TüV萊茵為京東方液晶顯示面板頒發碳足跡核查聲明

TüV南德授予上海瑞斯達組織溫室氣體核查聲明

新品|無刷電機運動執行套件 — RollerCAN Unit &amp; RollerCAN Lite

電壓空間矢量分量的極性是什么

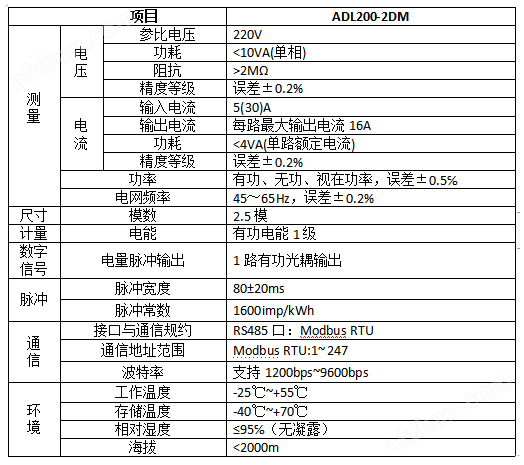

安科瑞ADL200-2DM宿舍預付費電表 照明空調單獨計量

新品|無刷直流電機運動執行套件|Roller485 Unit

評論