人工智能(AI)和邊緣計算的部署正在推動超大規模數據中心經歷模式轉變。諸如AI賦能的物聯網邊緣應用的5G、視頻流的大量數據以及全自動駕駛汽車的Zettabytes級數據等趨勢,要求超大規模數據中心能夠支持呈指數級增長的數據量和實施分布式低延遲處理。這些趨勢還導致了更復雜和更昂貴的數據中心存儲架構,用于支持不同負載下,不同接口配置的硬盤驅動器與固態驅動器(SSD)組合。本文將解釋如何使用PCI Express(PCIe)5.0/6.0 PHY IP在數據中心存儲設計中實現U.2/U.3連接。

存儲架構的演變

系統公司在設計服務器時面臨的一個主要挑戰,是升級存儲架構以滿足當前和未來的數據中心要求。這些升級包括集成多個背板、中間板和控制器,卻也增加了系統的復雜性和成本。

解決該挑戰的一種方法是,利用一個通用基礎設施,實現支持三種SSD協議(串行連接SCSI(SAS)、SATA和NVMe)的驅動器整合,從而優化存儲架構。

首先,SAS接口支持SATA SSD/HDD(硬盤驅動器)與SAS背板、主機總線適配器 (HBA)或獨立磁盤RAID冗余陣列(RAID)控制器互操作。但這不適用于NVMe SSD,需要利用支持NVMe的背板進行單獨的配置。

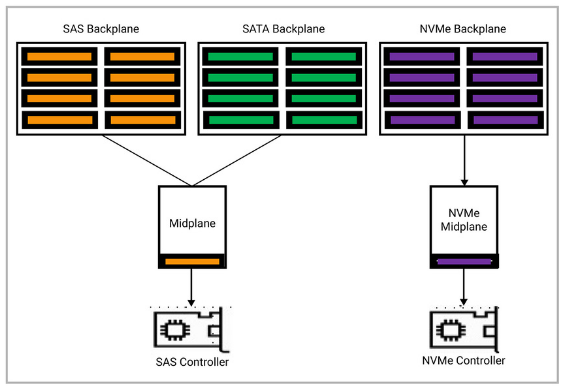

圖1顯示了帶有背板、擴展器或中間板和控制器的服務器存儲架構。

▲ 圖1:存儲架構需要不同的SAS、SATA 和 NVMe背板

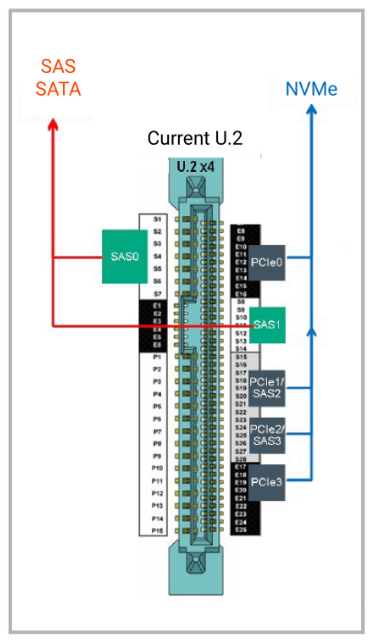

基于SFF-8639外形的U.2規范的出現是存儲驅動器整合的第一步。U.2外形支持多達4 PCI Express(PCIe)通道的NVMe SSD,以及多達雙通道的SAS/SATA SSD/HDD,如圖2所示。盡管U.2支持所有三個驅動器接口(NVMe、SAS和SATA),但由于它不能在同一插槽中提供可互換的SAS/SATA/NVMe支持,因此未對其進行優化。它仍然需要單獨的背板、中間板和控制器來支持NVMe。

▲ 圖2:U.2外形支持多達4 PCIe通道的NVMe SSD,以及最多雙通道的SAS/SATA SSD/HDD

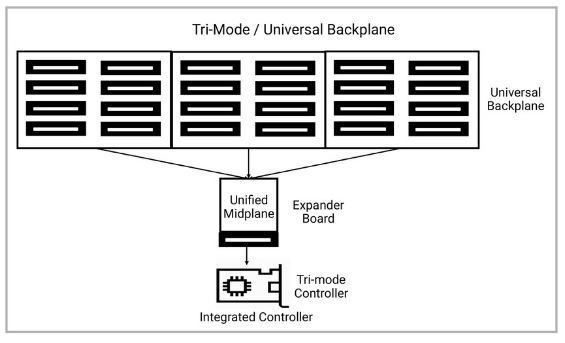

存儲架構隨著U.3規范的出現而進一步發展,U.3規范建立在SFF-8639連接器之上。U.3使用1個背板、1個中間板和1個控制器支持同一服務器插槽中的所有三個驅動器接口,從而實現真正的存儲驅動器整合,如圖3所示。U.3由存儲網絡行業協會 (SNIA)SSD外形(SFF)技術分會(TA)開發,并由SFF-TA-1001規范定義。它還向后兼容U.2,但U.2無法與U.3主機兼容。

▲ 圖3:U.3規范支持1個背板、1個中板和1個控制器,以提供真正的接口驅動器整合

U.3規范主要包括三模控制器、SFF-8639連接器和通用背板管理。

三模式控制器:在服務器主機和通用背板之間形成接口。它支持SAS、SATA和NVMe驅動器的相應協議,為服務器系統公司提供統一的解決方案,而不是SAS/SATA和NVMe使用單獨的控制器。這提供了靈活性,并允許根據最終應用的需要而混用驅動器。

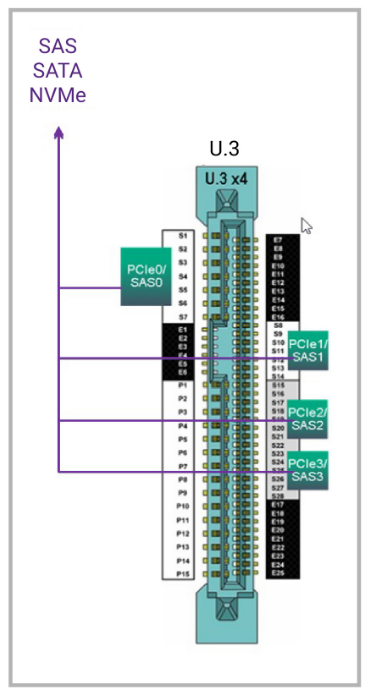

SFF-8639連接器:該連接器放置在驅動器托架上,并將SAS、SATA和NVMe驅動器連接到三模式控制器。主機檢測到兼容的通信協議。SFF-8639連接器使用可用引腳組合來識別已有驅動器。U.3的存儲驅動器整合功能,使服務器系統公司能夠通過使用單個連接器支持SAS/SATA和NVMe驅動器,以此來簡化其背板設計,如圖4所示。由于使用更少的組件,這也帶來了成本效益。

▲ 圖4:U.3連接器支持SAS、SATA和NVMe驅動器

通用背板管理(UBM):UBM由SSD Form Factor Working Group開發,由SFF-TA-1005規范定義,提供管理和控制SAS、SATA和NVMe背板的標準方法,以實現可配置性和靈活性。UBM提供了背板管理的兩個重要特性:

支持驅動器托架內存儲介質類型之間的互換性,例如在系統運行時在SAS、SATA和NVMe之間切換

無需對存儲驅動器或軟件棧做出任何改動,就能管理SAS、SATA和NVMe設備

U.3外形的優勢

U.3規范:

通過整合SAS、SATA和NVMe驅動器,并通過具有成本效益的電纜和組件來簡化系統,提供更高的靈活性和可配置性,同時降低系統復雜性和成本

可通過單個驅動器插槽來實施SAS、SATA和NVMe協議

支持跨服務器存儲協議的標準管理工具

整合SAS、SATA和NVMe驅動器的優勢,實現更好的性能+

提供支持NVMe的選項,NVMe的吸引力超過SAS和SATA

保持與U.2的向后兼容性

適用于U.2/U.3外形的PCIe IP支持

由于可擴展性和最低延遲等優勢,企業存儲正在從SATA遷移到NVMe。超大規模數據中心需要為業務數據準備更快的存儲,例如具有PCIe PHY接口的NVMe SSD,該接口由U.2/U.3架構支持。PCIe 4.0 PHY IP已經部署在NVMe SSD中,隨著性能要求從16GT/s翻倍到32GT/s,PCIe 5.0接口的重要性已經不言而喻。

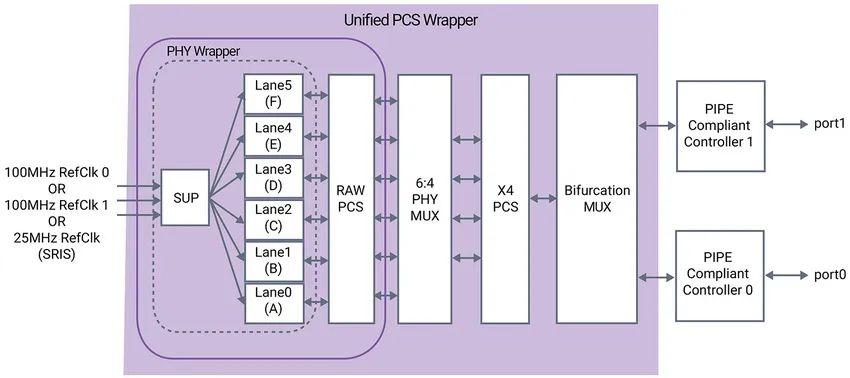

如圖5所示,定制、面積優化的6通道PCIe 5.0 PHY解決方案可用于支持U.2/U.3連接,其功能包括:

帶遲滯和數字時鐘邊緣計數器的參考時鐘檢測電路

支持25MHz參考時鐘

適用于25MHz參考時鐘的擴頻時鐘(SSC)和獨立參考時鐘獨立SSC(SRIS)

具有分叉多路復用器(MUX)和任何MUX通道的統一物理編碼子層(PCS)包裝器

世界一流的存儲公司已經在使用此類解決方案。

▲ 圖5:用于U.2/U.3連接的定制PCIe 5.0PHY

SSD公司已經在為U.2/U.3連接設計PCIe 6.0 PHY+Compute Express Link(CXL)IP解決方案。PCIe 6.0 PHY IP將改善內存帶寬,CXL IP將促進全新存儲架構的開發,因為它能為存儲系統的緩存提供更大的內存池。

隨著數據量和復雜性呈指數級增長,超大規模數據中心正在經歷模式轉變,并納入分布式低延遲處理。U.2/U.3存儲架構的實施對于這些數據中心至關重要,因為它能夠以優化的性能和成本實現不同的工作負載。U.3標準確保存儲設計符合當前和未來的數據中心要求。該規范使用1個背板、1個中板和1個控制器就能支持同一服務器插槽中的SAS、SATA和NVMe驅動器。除了系統靈活性外,U.3規范還提供SAS、SATA和NVMe之間的替換路徑。由于走線、電纜和連接器更少,U.3簡化了背板系統并降低了總體擁有成本。它還保持與U.2平臺的向后兼容性。若想輕松實現U.2/U.3連接,設計人員可以可慮采用新思科技為PCIe 5.0、PCIe6.0和CXL開發的新思科技IP。PCIe 5.0的新思科技IP提供定制的x6通道解決方案,支持U.2/U.3外形,新思科技PCIe 6.0 IP方案則可以滿足U.2/U.3的未來要求。

總之,新思科技提供經過硅驗證的完整PCIe控制器、PHY和驗證IP解決方案,并已成功實現與第三方設備的互操作性。該解決方案經過優化,可滿足目標應用的延遲、面積和功耗要求。

原文標題:數據量要上去,延遲要下來,數據中心存儲架構該如何升級?

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

數據中心

+關注

關注

16文章

4761瀏覽量

72034 -

存儲架構

+關注

關注

0文章

17瀏覽量

10103 -

新思科技

+關注

關注

5文章

796瀏覽量

50334

原文標題:數據量要上去,延遲要下來,數據中心存儲架構該如何升級?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體存儲器在數據中心中的應用

Solidigm發布高性能PCIe 5.0 SSD,引領數據中心存儲新紀元

美光推出9550系列數據中心PCIe 5.0 SSD

憶聯全場景存儲解決方案助力金融數據中心存力飛躍

英威騰數據中心解決方案實現安全升級和高效運轉

人工智能數據中心的新型連接解決方案

CXL技術:全面升級數據中心架構

超融合架構解決方案

傳統數據中心架構和葉脊架構網絡解決方案

數據中心存儲的趨勢

數據中心市場的關鍵以太網解決方案

數據中心存儲架構升級解決方案

數據中心存儲架構升級解決方案

評論