軟件定義無線電 (SDR) 出現后,射頻 (RF) 世界徹底改變。這些設備將射頻行業的主要技術范式從固定和笨重的模擬電子設備轉變為靈活緊湊的基于軟件的信號處理,顯著增加了商用現貨 (COTS) 無線電系統的適用范圍。因此,SDR 現在主導著 RF 市場,用于各種應用。然而,每個應用都有自己的要求,包括尺寸、重量和功率 (SWaP)、性能和成本,因此開發人員必須仔細設計 SDR 以符合市場需求。在設計流程中必須評估的主要瓶頸是 SWaP 和性能之間的權衡:每個 SDR 由許多不同的組件組成,

在本文中,我們將討論 SDR 如何通過各種性能、通道數和數字信號處理器 (DSP) 處理能力來滿足多個市場的需求,同時通常需要考慮 SWaP 和預算限制。事實上,與傳統的模擬對應物相比,僅使用 SDR 本身就可以將射頻系統的總尺寸和重量減少 80% 或更多,這非常適合多種應用,包括 MRI、雷達、頻譜監測、點對點點鏈接,以及測試和測量。然而,關鍵市場需要進一步降低 SWaP 和成本,這是通過降低某些組件的性能或特性總數來實現的,例如減小調諧范圍、接收 (Rx) 和發送 (Tx) 通道的數量、 DSP 能力和總帶寬。

SDR、電源要求和性能規格概述

在討論設計權衡之前,讓我們回顧一下 SDR 的基礎知識。SDR 本質上是一個收發器,具有復雜的嵌入式處理能力,以及用于通過軟件更改無線電參數的靈活/可重新配置平臺。通用 SDR 分為三個階段:

無線電前端 (RFE)

數字后端

混合信號接口。

RFE 由一個或多個 Rx 和 Tx 通道組成,能夠處理高達數十千兆赫 (GHz) 的寬調諧范圍內的信號。此外,市場上帶寬最高的 SDR 可提供每通道 3 GHz 的瞬時帶寬,并與多達 8 個獨立的 Rx/Tx 信號鏈一起工作。

另一方面,數字后端負責所有信號處理操作、控制功能、智能、數據存儲和通信協議。該階段由具有板載 DSP 功能的高端 FPGA 組成,針對調制、解調、上變頻、下變頻、數據打包和任何所需的特定應用功能(如安全方案或人工智能)進行了優化。FPGA 還與主機或網絡進行通信,將數據打包成以太網數據包,并通過 SFP+/qSFP+ 鏈路以 10-400 Gbps 的傳輸速率進行傳輸。由于 FPGA 能夠完全改變其內部結構,數字后端可以輕松地重新配置或即時升級,以適應最新的無線電協議和 DSP 算法。

最后,混合信號接口由專用的數模和模數轉換器 (DAC/ADC) 組成。SDR 的每個階段都由一組不同的組件組成,每個組件的設計和尺寸都可以設計為實現特定的 SWaP,高端 SDR 還兼容無線電處理軟件,例如 GNU radio。

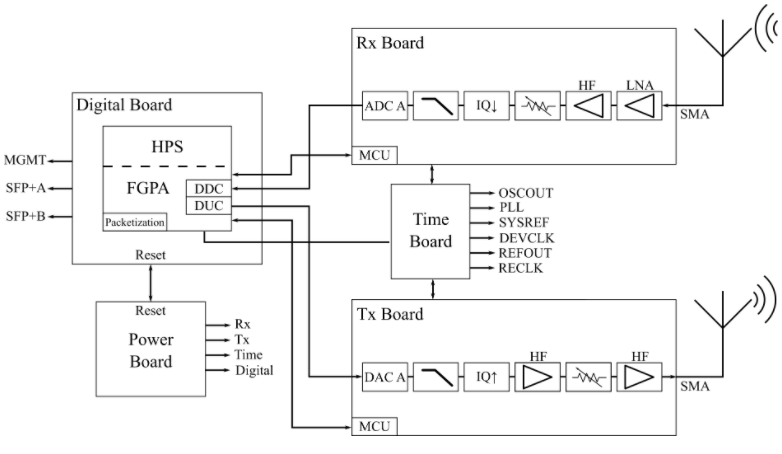

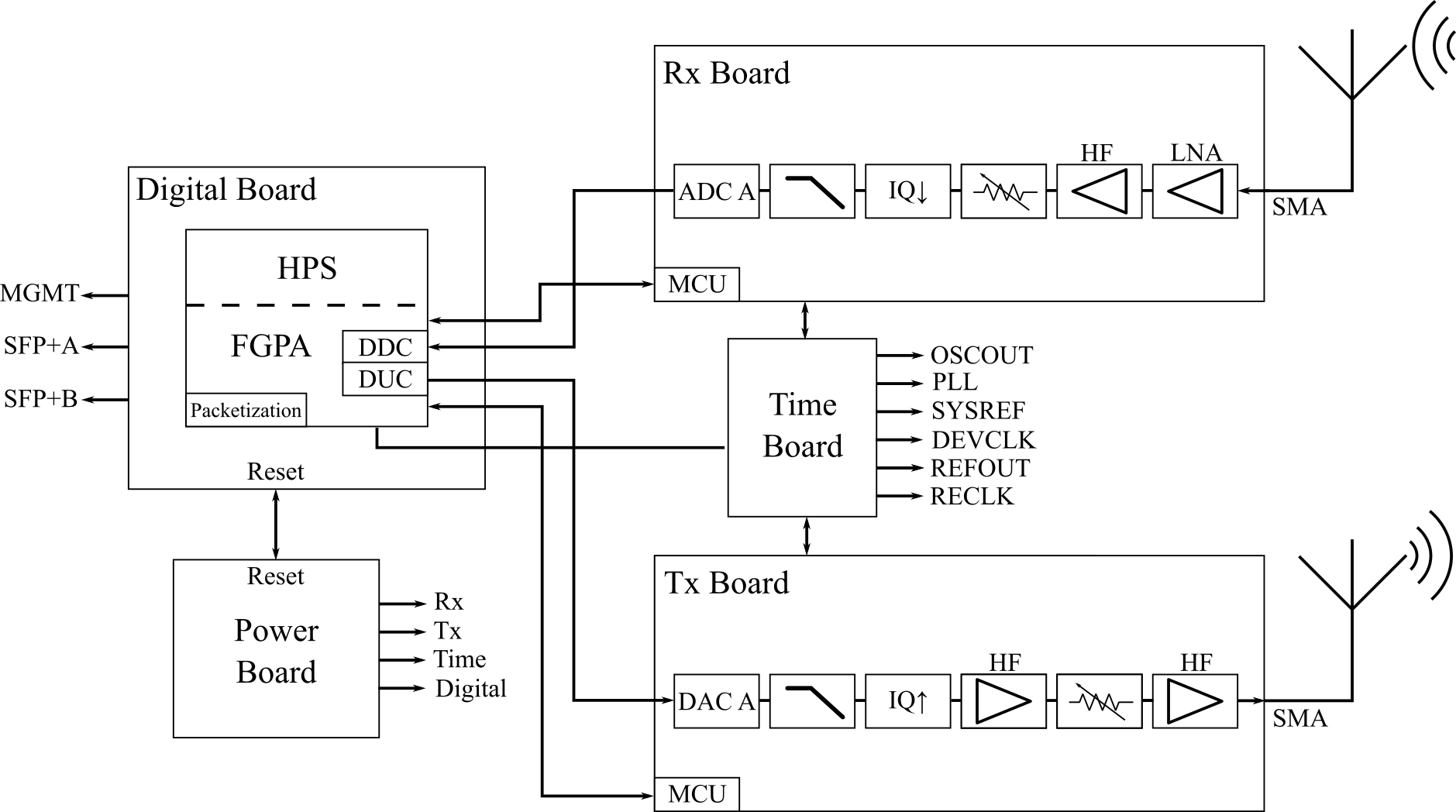

根據前面的硬件描述,市場上有幾種不同的 SDR 配置。高性能 SDR 通常需要使用 5 個板:Rx 板、Tx 板、數字板、電源板和時間板(見圖 1)。Rx 板只是接收信號的 RFE 的一部分,以 ADC 終止。Tx 板由 RFE 的傳輸通道組成,通常以 DAC 開頭。每個 Rx 和 Tx 板都可以由多輸入/多輸出 (MIMO) SDR 中的多個并行通道組成。數字板提供了一個接口來控制、配置和發送/接收 RFE 通道的數據,所有這些都由時間板保持同步。電源板只是將線路電力轉換為 RFE、數字和計時板可用電壓水平的電源。最后,

圖 1:SDR 板架構。(來源:每惡習)

任何電子系統中最基本的限制是功率要求:任何需要定制 PCB 設計的應用也需要功率預算。這是因為電源方案及其局限性在很大程度上取決于應用,因此對于具有不同目標的類似項目,電源預算可能會有很大差異。例如,使用電池供電的 SDR 的功率預算與連接到電網的 SDR 的預算有很大不同。此外,電源必須從電源板饋送到 SDR 收發器中的所有其他模塊。

由于每塊電路板都需要特定的穩定和干凈的電壓電平,并且必須不受電源波動的影響,因此穩壓器是配電中的關鍵組件。這些組件是集成電路,無論負載或輸入電壓如何變化,都能提供恒定的輸出電壓,并且在功率預算中也必須考慮到它們。

然而,由于必須執行大量計算,SDR 的最大功耗來源是 FPGA。FPGA 的功耗可以通過軟件進行優化,通過減少運算次數和優化信號處理鏈。繁重的計算會消耗大量的能量。例如,JESD204 收發器消耗大量功率。

另一個重要因素是 RFE:RFE 的功耗隨著特征數量、工作帶寬、調諧范圍和通道數量的增加而增加。一些組件比其他組件需要更多的功率,因此在設計流程中必須為每個組件權衡功率和性能之間的權衡。

就像功率需求一樣,性能需求也高度依賴于應用,可以用無線電鏈路預算來描述。無線電鏈路預算方程用于確定如何更改設計以實現一定水平的性能,這由接收功率強度表示(方程 1)。計算出鏈路預算后,可以檢查設計是否能夠滿足性能要求(例如誤碼率、信噪比 (SNR) 和線性度)。

RxPower(dBm) = TxPower(dBm) + 增益(dBm) – 損耗(dBm)(1)

SDR 領域有幾種不同的性能要求,對設計和應用有不同的影響。在這里,我們討論一些最重要的:

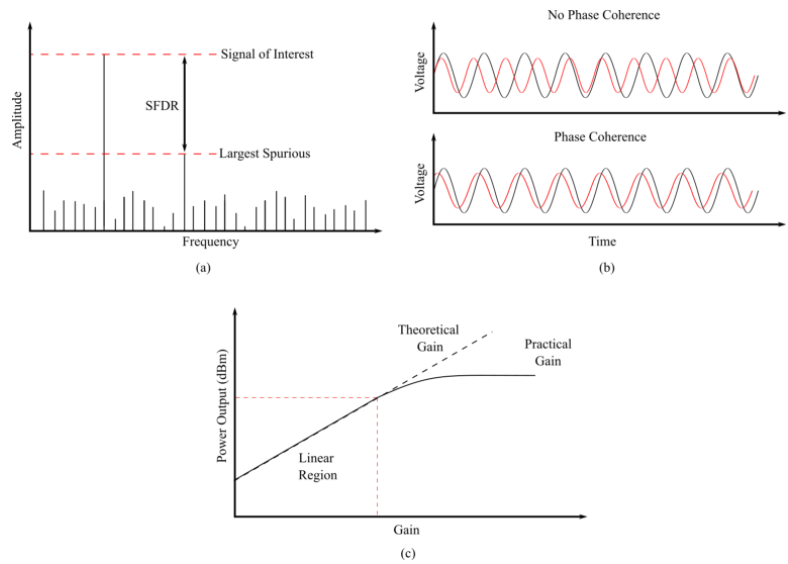

動態范圍:也稱為無雜散動態范圍 (SFDR),定義了基波諧波強度與輸出中最高雜散信號之間的比率。它用于定義 SDR 的動態性能。這可以在圖 2a 中看到。

相位一致性:量化 SDR 模塊的相位同步程度。它依賴于時鐘板的質量和時鐘分布,因為時鐘信號必須由所有組件正確共享。這可以在圖 2b 中看到。

信噪比 (SNR):它是信號功率與接收到的總射頻噪聲之間的比率。它可能是無線電系統最重要的參數之一,具體取決于應用,并描述了在給定外部和內部條件的情況下接收到的電磁 (EM) 信號的質量。它取決于環境條件(降水、閃電、濕度、溫度)、RFE 的電子設備(熱噪聲、散粒噪聲、閃爍噪聲)和外部 EM 發射器(傳輸線、發電廠、發電機、電話)。

靈敏度:接收器可以檢測到的最低信號。它與 SDR 和 SFDR 密切相關。

數據吞吐量:描述數據發送到主機或網絡的速度。在 MIMO 和頻譜監測應用中尤為重要。

調諧范圍: SDR 可以接收和發送的最大頻率范圍。這顯著影響了設備的適用范圍。

RF 輸出增益: Tx 信號鏈末端的輸出功率,它定義了可以傳輸多少功率。

RF Input Gain:接收機輸入端的 LNA 增益,極大地影響 SNR 和整體信號增益。

線性度:描述信號鏈引入的失真量(諧波和互調),特別是來自放大器的失真。這可以在圖 2c 中看到。

圖 2:性能指標包括 (a) SFDR、(b) 相位相干性和 (c) 線性。(來源:每惡習)

盡管有許多與功率對比相關的限制在性能權衡方面,僅向系統添加 SDR 就可以通過將射頻/模擬和大多數計算功能集成在一個系統中來顯著降低整個系統的復雜性。然而,特別提款權本身提出了一些挑戰。例如,調諧范圍越高,時鐘方案就越復雜,以應對頻率的增加。這也增加了 RFE 的復雜性,進而顯著影響功率要求。無線電鏈的數量也增加了功耗,因此 MIMO 板將比單通道 SDR 具有更高的功率需求。事實上,當不需要接收(或發送)功能時,某些應用需要僅具有發送(或接收)功能的 SDR。功率需求也隨著 RFE 增益(輸入和輸出)和 ADC 分辨率的增加而增加,因此實現更好的 SNR、SFDR、線性度和靈敏度通常伴隨著所需功率的增加。最后但同樣重要的是,FPGA 中 DSP 操作的數量和復雜性是影響功耗的主要因素之一。例如,在需要對大量數據進行大量快速傅立葉變換 (FFT) 處理的應用中,FPGA 的效率將大大降低。這也凸顯了 FPGA 和 RFE 之間需要平衡的必要性,因為 RFE 性能的降低實際上會增加功耗,因為需要 FPGA 所需的更多處理功率。FPGA中DSP運算的數量和復雜度是影響功耗的主要因素之一。例如,在需要對大量數據進行大量快速傅立葉變換 (FFT) 處理的應用中,FPGA 的效率將大大降低。這也凸顯了 FPGA 和 RFE 之間需要平衡的必要性,因為 RFE 性能的降低實際上會增加功耗,因為需要 FPGA 所需的更多處理功率。FPGA中DSP運算的數量和復雜度是影響功耗的主要因素之一。例如,在需要對大量數據進行大量快速傅立葉變換 (FFT) 處理的應用中,FPGA 的效率將大大降低。這也凸顯了 FPGA 和 RFE 之間需要平衡的必要性,因為 RFE 性能的降低實際上會增加功耗,因為需要 FPGA 所需的更多處理功率。

除了功率,另一個重要的權衡是尺寸/重量與性能。在這種情況下,要求越小,電路板的問題就越多。例如,混合信號板可能會受到串擾、接地干擾、一般 EMI 效應和寄生阻抗的嚴重影響。如果來自數字電路的噪聲到達模擬信號路徑,噪聲性能就會下降。此外,隨著 IC 尺寸減小且沒有足夠空間放置大型散熱器,散熱也成為問題。一種有效的方法是使用差分信號和適當的接地。此外,模塊化 SDR,例如來自 Per Vices 的 SDR,可以通過根據應用移除/添加功能板來適應任何應用,從而使用相同的設備提供更緊湊的解決方案。

應用程序及其各自的要求

在討論 SWaP 限制時,衛星部署始終是最有問題的應用。機載 SDR 必須非常緊湊和輕便,以減少有效載荷,尤其是在納米衛星任務中。因此,在設計電路板時必須仔細考慮,以確保在緊湊的空間中散熱和信號完整性都可以接受。此外,電力需求由太陽能電池板和車載電池決定,因此能源供應可能會受到很大限制。衛星需要多個射頻通道,包括遙測和控制 (TT&C)、下行鏈路/上行鏈路和導航。但是,必須盡量減少通道總數以符合 SWaP 要求。在這種情況下,SDR 可以幫助優化 SWaP,因為可以遠程重新配置信道參數(頻率、調制、用途),

在地面站中,尺寸/重量要求較為寬松,但必須始終考慮功耗,尤其是在偏遠地區應用時。最重要的性能參數是通道靈敏度(主要由 SNR 和 SFDR 定義)和調諧范圍。因此,使用具有更高分辨率和采樣頻率的 ADC 是有意義的。這在來自太空的下行鏈路信號中尤為重要,其中高頻信號(X 和 K 波段)受到環境條件的嚴重衰減。高端 ADC 顯著增加了功耗,結合更高的數據吞吐量和快速的信號處理導致固有的更大 SWaP 要求,這對于性能和成本最重要的地面站通常不是問題。

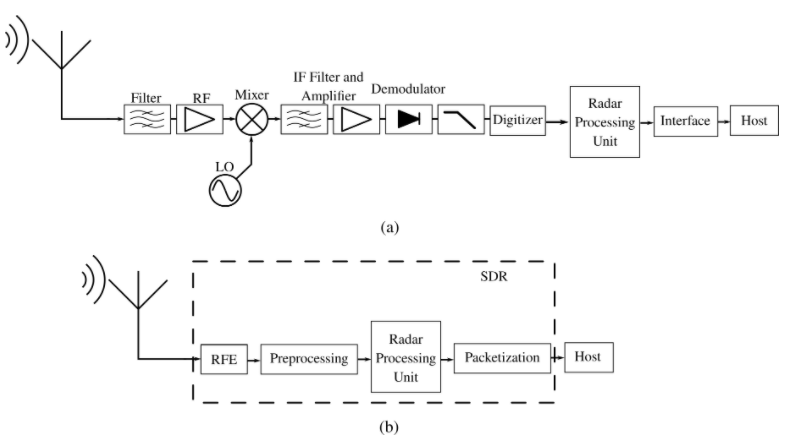

在復雜的雷達系統中,SDR 可以通過替換大型和笨重的傳統模擬系統來大大降低 SWaP 要求(圖 3)。SDR 可以在單個解決方案中實現波形生成、定時處理、RFE 和完整的信號處理鏈,從而減小雷達的總尺寸和復雜性。此外,關鍵雷達應用可以顯著受益于 MIMO SDR 的低噪聲系數和出色的相位相干性和穩定性,以緊湊的外形尺寸達到高性能水平。

圖 3:使用 (a) 傳統模擬射頻解決方案和 (b) 基于 SDR 的射頻系統的雷達接收器。(來源:每惡習)

另一個值得一提的應用是頻譜監測。在這些應用中,高數據吞吐量是強制性規范,因為必須實時接收大量數據并將其發送到主機。例如,當一次監測 1 GHz 的頻譜塊時,需要高性能設備。高端 COTS SDR,例如Cyan 模型來自 Per Vices,通過 4×40/100Gbps 以太網鏈路傳輸數據,由于需要 FPGA 打包的數量,它以增加功率要求為代價滿足頻譜監控要求。此外,還需要快速 FFT 處理,這大大增加了功率預算。隨著使用非常靈敏的線性放大器,消耗量也會增加,從而確保具有高檢測能力的平坦且寬的檢測帶寬。因此,設計具有有限 SWaP 要求的有效頻譜監控解決方案非常困難,但在許多高性能頻譜監控應用中,這不是問題。

結論

SDR 在市場的各個方面都主導著射頻行業。從硬件到軟件的范式轉換確保了更好的靈活性、更高水平的可重構性并降低了 SWaP 要求。然而,一些關鍵應用仍然需要具有優化 SWaP 屬性的 SDR。在設計級別,必須為每個應用程序評估兩個主要權衡:性能與功耗以及性能與尺寸/重量的權衡。在第一個方面,具有高性能的高端組件需要大量功率,因此通過減少功能數量或正確組件的性能水平可以顯著提高 SWaP。在第二種情況下,關鍵應用程序所需的尺寸減小通常會降低 SDR 的整體性能,這可以通過減少特征的數量來補償。一般來說,性能的提高會導致 SWaP 預算的增加,但適當的優化可以在不降低整體性能的情況下優化 SWaP。在這種情況下,模塊化 SDR 非常可取,因為它提供了可由應用工程師定制的 COTS 解決方案,因此可以針對特定任務進行優化。

Kaue Morcelles是一名電氣工程師,專注于電子設計和儀器儀表。學習和撰寫有關尖端技術的文章是他的熱情之一。

Brendon McHugh是一名技術作家和現場應用工程師。他擁有多倫多大學的理論和數學物理學學位。

-

pcb

+關注

關注

4358文章

23443瀏覽量

407750 -

射頻

+關注

關注

106文章

5737瀏覽量

169938 -

SDR

+關注

關注

7文章

235瀏覽量

51047 -

模數轉換器

+關注

關注

26文章

3315瀏覽量

128066

發布評論請先 登錄

SDR_SDR是什么意思

淺談軟件定義無線電SDR

基于混合信號RF IC的寬帶SDR設計方案

實現SDR所需的開發方法有哪些

運算放大器功耗與性能的權衡

運算放大器功耗與性能的權衡

運算放大器功耗與性能的權衡

Gowin I3C SDR IP的參考設計

理解高效MCU設計的功耗和性能權衡

軟件定義無線電中的尺寸、重量和功率與性能權衡

評論