使用 FPGA 的優勢之一是能夠實施經過驗證的知識產權,以快速、自信地完成橋接功能。看看一個常見但復雜的接口 PCI Express,就可以證明這些好處。

與其前身外圍組件互連 (PCI) 一樣,PCI Express (PCIe) 正在成為一種無處不在的系統接口。與 PCI 不同,PCIe 采用 SERDES 接口為用戶提供未來應用所需的可擴展性。隨著系統帶寬的增加,越來越多的應用正在轉向基于 SERDES 的接口,例如 PCIe。過去,專用 IC (ASIC) 和專用標準產品 (ASSP) 通常用于實施下一代接口解決方案。ASIC 和 ASSP 是流行的選擇,因為它們提供了低成本、低功耗的設計解決方案。

然而,幾個新的 FPGA 系列為 PCIe 接口提供了有吸引力的選擇。FPGA 提供了一個適應性強的平臺,它沒有 ASSP 的不靈活性,也沒有 ASIC 通常相關的較長的交付周期和大量的非經常性工程成本。具有嵌入式 SERDES 的新一代 FPGA 以低成本、低功耗的串行接口解決方案為設計人員提供了極其豐富、高價值的可編程架構。相同的 FPGA 可用于支持各種串行協議,如 PCIe、GbE、SGMII、XAUI、Serial RapidIO 等,為多種設計提供單一 FPGA 平臺。

PCIe 也正在成為控制平面應用程序的首選接口,取代舊的并行接口,如 PCI。新一代設備使用一個或多個 PCIe 鏈路。在大多數設備中,PCIe 內核被實現為 PCIe 端點。設計人員通常需要將這些設備連接到具有并行總線的上一代設備(例如具有并行總線接口的微處理器)。使用低成本、低功耗 FPGA 在 PCIe 和并行接口之間進行橋接可為設計人員提供解決此問題的靈活性,而不會超出其系統成本和功率預算。

設計挑戰

隨著設計人員從 PCI 遷移到 PCIe,協議的復雜性以及基于 SERDES 的設計所涉及的復雜性構成了重大挑戰。幸運的是,FPGA 與全功能 PCIe IP 內核、參考設計、硬件評估板和相關演示相結合,有助于消除 PCIe 設計人員面臨的陡峭學習曲線。FPGA 是基于 PCIe 的應用的理想平臺。因為它們是可編程的,所以 FPGA 使設計人員能夠靈活地在設計周期的后期解決設計問題,并加快周轉時間。隨著個別設計要求的發展,設計人員可以輕松更改或添加功能。FPGA 設計還允許設計人員進行更新以適應規范的變化,使他們能夠在未來證明其設計不會過時。可編程平臺使設計人員能夠使用相同的 FPGA 來實現連接到各種其他 PCIe 芯片組的接口解決方案:端點、根復合體或交換機。設計人員可以在FPGA中集成系統所需的其他功能,減少板上元件的數量,進一步降低系統的總成本。

橋接接口

FPGA 為系統設計提供了極其靈活的可編程平臺。包含 IP 內核、硬件平臺、演示設計、驅動程序和軟件的綜合解決方案包使設計人員能夠縮短開發周期,同時降低設計的復雜性。

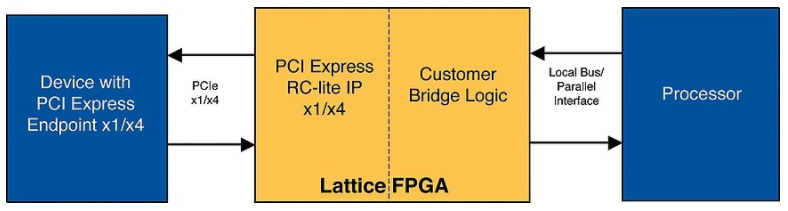

一個常見的設計要求是 PCIe 解決方案在 PCIe 串行接口(端點設備)和傳統并行總線接口之間進行橋接,如圖 1 所示。具有 PCIe 根復雜 IP 內核的 FPGA 為設計人員提供了實現所需的基本構建塊這樣的解決方案。或者,ASSP 和 ASIC 也可以實現此功能。然而,與 FPGA 不同,這些設備只能實現固定配置,無法更改以適應各種可用的并行總線接口。

圖 1:具有 PCIe 根復雜 IP 內核的 FPGA 在 PCIe 串行接口和傳統并行總線接口之間橋接。

另一方面,可編程 FPGA 平臺使設計人員能夠對其設計進行特定更改,以實現與其特定板上可用接口相匹配的特定橋接功能。設計人員還可以靈活地在單個 FPGA 中實現多個橋接或橋接的不同配置,從而減少板上的組件總數。FPGA 與 PCIe 根復雜 IP 核相結合,可以實現設計所需的多種其他橋接解決方案。

PCIe 根復合體

PCIe 端點作為上游設備運行,這是根復雜設備可以執行的功能。然而,就所使用的 FPGA 門而言,一個全功能的根復雜實現是相當昂貴的。相反,具有事務層功能子集的輕量級根復雜核心足以實現大多數橋接功能。

如圖 1 所示,這座橋由兩個基本組成部分組成。第一個塊是 PCIe 根復合體(或 Root Complex-lite)IP 內核,它與 PCIe 端點設備接口。第二個塊是連接到本地總線/并行接口的橋接邏輯。由于此實現是在可編程 FPGA 中實現的,因此設計人員可以根據特定接口需求靈活地定制設計。其他功能也可以集成到同一個 FPGA 中,從而消除板上的其他組件并降低總體材料成本。

實現更輕量級的 IP

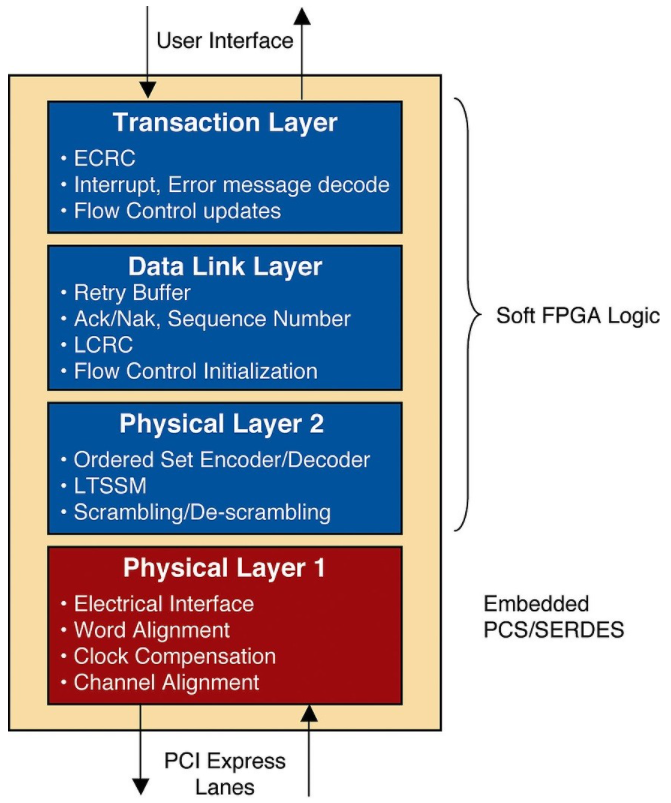

PCIe 是一個復雜的協議。提供功能齊全、經過充分驗證的 PCIe IP 內核可顯著降低設計復雜性。例如,萊迪思半導體的 PCIe Root Complex Lite (RC-lite) 內核實現了 x1 或 x4 根復合功能,主要用于 PCIe 橋接應用。如圖 2 所示,所有 PCIe 層均作為嵌入式 ASIC 塊和在 FPGA 中實現的 PCIe RC-lite 軟 IP 內核的組合來實現。各種模塊包括電 SERDES 接口、物理層、數據鏈路層和最小事務層,以支持實現 PCI Express 根復雜功能所需的協議棧。這種較輕的 IP 針對 PCIe 端點接口和并行本地總線接口之間的簡單橋接應用進行了優化。

圖 2: PCIe RC-lite IP 協議棧有助于降低 PCIe 橋接應用的設計復雜性。

在 LatticeECP2M 或 LatticeECP3 FPGA 中實現的 PCIe RC-lite IP 可實現低成本、低功耗的 PCIe 橋接應用,同時為設計人員提供定制橋接接口的靈活性。此外,PCIe 硬件評估板和各種參考設計、演示和軟件驅動程序可幫助設計人員啟動他們的 PCIe 設計并縮短上市時間。萊迪思還為設計人員提供了一個硬件評估板來測試 RC-lite IP 解決方案。設計人員可以在部署之前完成互操作性并驗證這些解決方案的系統級功能,從而節省通常與設計后調試和性能增強相關的時間和成本。

簡化橋接復雜性

PCIe 設計對設計人員提出了重大挑戰。對接口的要求各不相同,具體取決于 PCIe 設備是否必須連接到另一個端點、根聯合體或交換機。此外,設計通常需要一個 PCIe 端點設備和另一個具有并行總線接口的設備之間的連接。

設計人員可以在低成本、低功耗的 FPGA 平臺中實現這些功能,同時保留靈活可編程架構的所有優勢。在 FPGA 中使用 PCIe 根復雜 IP 功能提供了實現這些橋接功能的理想平臺。

審核編輯:郭婷

-

FPGA

+關注

關注

1629文章

21758瀏覽量

604241 -

接口

+關注

關注

33文章

8643瀏覽量

151387 -

PCIe

+關注

關注

15文章

1243瀏覽量

82767

發布評論請先 登錄

相關推薦

EE-86:將SHARC 2106x DSP與PLX 9080 PCI橋接芯片連接

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

通過PLX PCI9080橋接芯片實現TMS320C6000擴展總線與PCI總線的接口

KeyStone設備的PCI Express (PCle)常見問題

使用TI PCI-Express Gen5.0轉接驅動器進行眼圖掃描

XIO2001 PCI Express至PCI總線轉換橋接器數據表

在FPGA中實施PCI Express橋接解決方案

在FPGA中實施PCI Express橋接解決方案

評論