由于其平行照明,WLI PL非常適合用于測量具有高深寬比的等離子切割刻蝕溝槽,因為大部分光到達了刻蝕結構的底部,因此可以測量深度。

隨著經典摩爾定律晶體管的優(yōu)勢在單片芯片上縮小,先進封裝的采用正在加速。先進的封裝通過高密度互連實現了多個不同管芯的異構集成,從而提高了設備性能并減小了占位面積。先進的封裝體系結構,例如英特爾的嵌入式多芯片互連橋,臺積電的集成扇出和高帶寬內存(HBM),已經滿足了摩爾定律的要求,以滿足對更大的連接性,計算能力,速度和成本的需求在運輸,5G,物聯網,人工智能和高性能計算中的大趨勢的有效性。先進的封裝使行業(yè)能夠開發(fā)新的倒裝芯片工藝,2.5D中介層和TSV技術,以及最近的2D和3D扇出工藝,它們在最小的空間內具有高密度的連接。

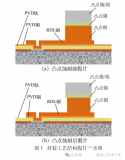

扇出晶圓級包裝(FOWLP)是當今增長最快的高級包裝領域之一。根據Yole Research,FOWLP預計將從2016年的3.2億美元增長到2022年的$ 2.5B。在FOWLP中,單個芯片組裝到由低成本聚合物材料制成的人造晶圓中,并具有額外的連接空間。 RDL將芯片上的連接重定向到邊緣區(qū)域。 FOWLP的優(yōu)勢包括由于更薄的封裝而提高了每瓦性能,并提供了更多的不同設計,但是這些新器件的制造帶來了新的測量挑戰(zhàn),包括測量深蝕刻溝槽的能力。

已建立的設備MicroProf?系列–來自的多傳感器技術FRT(FormFactor公司)–結合白光干涉儀WLI PL和WLI FL,在其他過程達到極限的生產,研究和開發(fā)的高級包裝領域,提供光學和非接觸式創(chuàng)新解決方案。例如,等離子切塊刻蝕溝槽的深度為50至200 μm,遠遠超出了AFM或輪廓儀尖端的范圍。許多光學方法(例如共聚焦顯微鏡)也因其孔徑而不適用于此測量,因為由于側壁的陰影,沒有來自溝槽底部的光可以回到傳感器中。另外,蝕刻工藝導致蝕刻溝槽中的表面變粗糙,并因此導致基板表面與溝槽底部之間的反射率的高差異,這可能導致測量期間的問題。

由于其平行照明,WLI PL非常適合于測量具有高深寬比的等離子切割蝕刻溝槽,因為大部分光到達蝕刻結構的底部,因此可以測量深度。根據表面紋理,可以測量最小寬度為2到3 μm,長寬比最高為50:1(深度與寬度)的結構。使用特殊的測量模式可以分兩個測量步驟進行測量。以這樣的方式測量襯底表面和結構的底部,以使得測量參數最佳地適應不同的表面條件。

測量技術的另一個問題通常是結構的橫向尺寸小,因為該方法的光學分辨率通常不夠高。例如,溝槽的溝槽寬度可以小于1 μm。 WLI FL使用一種特殊的算法來確定寬度最小為0.7 μm的蝕刻結構的深度。在這種情況下,長寬比可以達到3:1。這允許訪問以前未達到的尺寸。這種方法使得可以測量所有當前使用的TSV變體,包括直徑小于1微米的通孔,這些通孔不再可用光學方法檢測。

審核編輯:符乾江

-

芯片

+關注

關注

456文章

50886瀏覽量

424181 -

封裝技術

+關注

關注

12文章

549瀏覽量

67992

發(fā)布評論請先 登錄

相關推薦

先進封裝的核心概念、技術和發(fā)展趨勢

Chiplet在先進封裝中的重要性

先進封裝的技術趨勢

先進封裝技術的類型簡述

銳駿200V低壓和600V高壓MOS對于電機控制和電源管理

電偶腐蝕對先進封裝銅蝕刻工藝的影響

采用先進的封裝技術來測量深腐蝕溝槽

采用先進的封裝技術來測量深腐蝕溝槽

評論