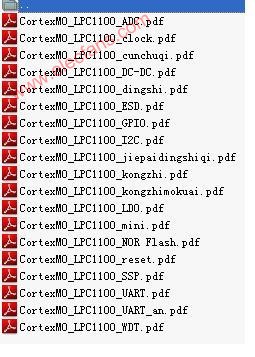

目錄

工程問題

原理/layout圖

優點

缺點

原理

選型

熱計算

計算 LDO 工作時的結溫

工程問題

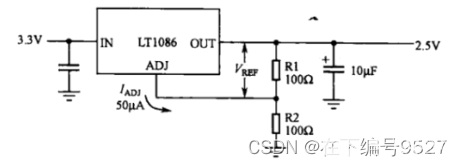

1 LDO 輸出電源電平低于設置值

某款LDO芯片在3.3V轉2.5時,輸出了2.3v,忽略了Dropout(壓差的要求),此款為1v壓差

應選取低壓差的LDO器件。

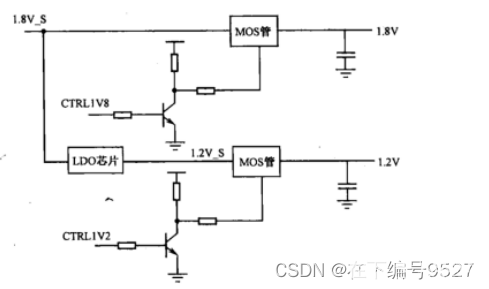

2 電源芯片欠壓保護電路導 致上電時序不滿足設計的要求

雖然1.8V先于1.2V上電,但1.2V卻延時了將近2s才上電。由于1.8V導通后,電壓被容性負載拉低,1.8V-S的電壓被迅速拉低,使得流向LDO的電壓變得很小, 觸發了欠壓保護,直到充電完畢,LDO才開啟。

需要在1.8V的MOS的柵極加個電容,減緩MOS導通速度。

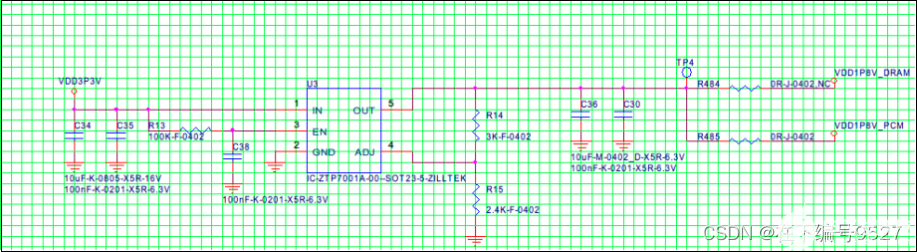

原理/layout圖

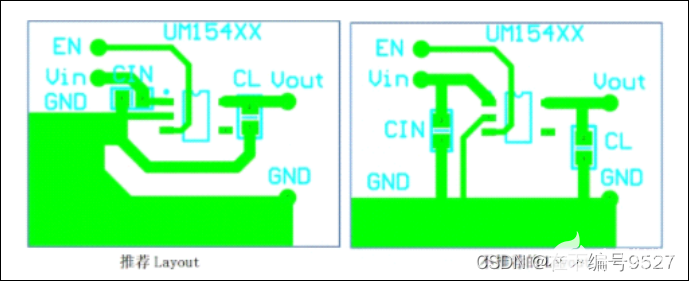

可以看出,左邊的電容正極緊挨vin,且形成的地環路明顯小于右邊。同時注意,ldo和電容的地要在同一層。

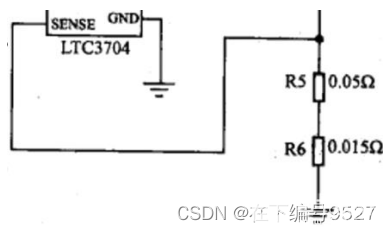

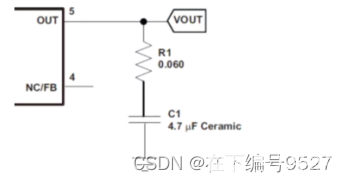

有些LDO是6腳,多了SENSE過流感應腳,僅在大電流場合下使用,大于5A,一般小電流

不用。

但SENSE 功能會導致電源芯片輸出電壓不穩定。

(由于相鄰層高速信號高速翻轉導致耦合進去,紋波大,數據傳輸時出現誤碼)

PCB:由于回流路徑經過,所以R5與R6也需要粗印制線連接。

SENSE只是提供電流感應的功能,只需要考慮低噪聲。

不需要考慮大電流問題,因此用普通信號線連接,且遠離干擾源。

優點

對低頻噪聲的抑制效果明顯,高速瞬態響應。

能夠衰減開關模式電源產生的電壓紋波。

電壓輸入與輸出無延時。

沒有電感。

缺點

輸入與輸出壓差過大不適用。

壓差!負載電流越大,壓差越大,工作溫度越高,壓差越大。

散熱功耗(功率損耗):(輸入-輸出電壓)乘電流。

故只能輸出小功率,工作效率低, 能耗消耗大,電流輸出小。

最大功耗不能超過3W,否則散熱有問題,且LDO可能會損壞。

ldo的輸出電容的ESR不能過小,不然負反饋很難工作。

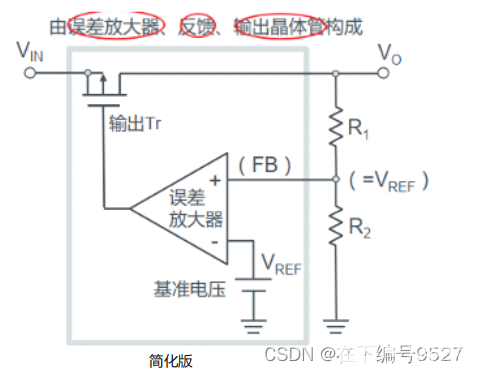

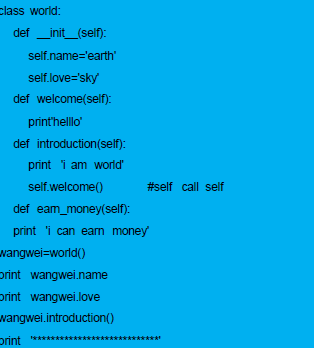

原理

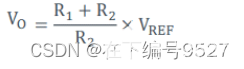

由差分放大器與工作在線性區的三極管組成。一般雙極穩壓器耐壓高且消耗電流偏大,

CMOS穩壓器耐壓偏低但消耗電流低,工作在線性區,當輸出電壓變小,反饋電壓也變小

差值變大,輸出電壓隨之變大。

想要更改啟動時間,變更FB的分壓電阻?

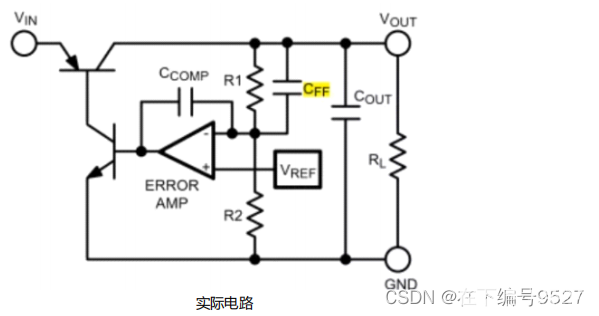

1. 并聯了前饋電容CFF,降低了誤差放大器的噪聲增益。

負反饋使得LDO的輸出噪聲不隨輸出電壓上升而大幅增加。

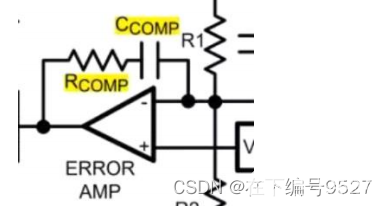

負反饋分析:

內部零點補償網絡:CFF和R1

形成了一個零點:ZFF=1/(2π×R1×CFF),該零點增加了正相移

也形成了一個極點:PFF=1/(2π×R1//R2×CFF)

傳統LDO的反饋回路的環路增益曲線由于輸出電阻較大,與負載電容作用后會產生

一個低頻極點P1,這個低頻極點帶來的附加相移使得反饋回路不穩定

用外部鉭電容(100mΩ量級)補償后,由于鉭電容擁有較高的ESR(如1ohm)

使得環路曲線中出現一個零點,高ESR將零點移至一個較低的頻率

這個零點帶來的反相相移的環路增益將為1

抵消掉之前低頻極點帶來的附加相移,使得反饋回路穩定

但ESR不能過大,不利于瞬態特性

2.并聯了輸出電容COUT,ESR補償

因為LDO屬于晶體管型,輸出阻抗高,所以需要并聯減小阻抗

利用坦電容特定的ESR和電容值可以為LDO進行補償。

采用MOS管后,將不需要特定的ESR來中和附加相移。

選型

壓差

ldo顧名思義,要求壓差要低

Vout≈vin-vdrop

功耗

(輸出電壓-輸入電壓)*電流

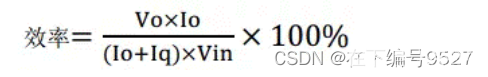

最大輸出效率

輸入電流等于輸出電流加上靜態功耗Iq*vin

電源紋波抑制比(PSRR)

越大越好,代表抑制輸入紋波的能力越強,一般給出的是1KHz下的值。

熱計算

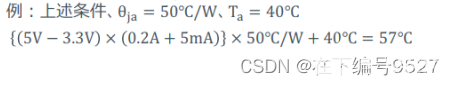

計算 LDO 工作時的結溫

輸出電壓:1.8V,輸入電壓:3.15與3.45V

電流變化從0-500mA,環境溫度50℃,熱阻28℃/W,求其結溫?

1 求出動態功耗與靜態功耗

靜態:(漏電流*輸入電壓)=15ma*3.45V

動態:(3.45-3.15)*500ma

2 結溫=總功耗*熱阻系數+環境溫度

=(輸入電壓-輸出電壓)*電流*熱阻+環境溫度

?

-

ldo

+關注

關注

35文章

2348瀏覽量

157261 -

電源芯片

+關注

關注

43文章

1193瀏覽量

79073

發布評論請先 登錄

深入LDO學習

深入LDO學習

評論