動態參數指標:這些參數本質上是動態的,取決于系統。例如,與 DDR/HBM 的通信效率在C綜合編譯時是未知的。 本文給大家提供利用axi_master接口指令端的幾個靜態參數的優化技巧,從擴展總線接口數量,擴展總線位寬,循環展開等角度入手。最核心的優化思想就是以資源面積換取高帶寬的以便并行計算。

熟記這本文幾個關鍵的設計點,讓你的HLS內核接口效率不再成為設計的瓶頸!

?

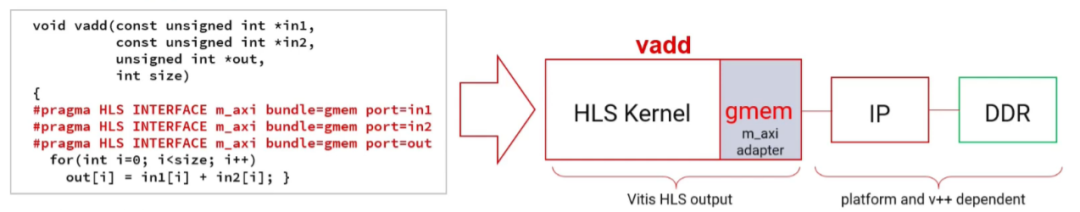

以上代碼在進行了c綜合后,我們所有的指針變量都會依據指令的設置映射到axi-master上,但是因為根據指令中所有的端口都綁定到了一條總線gmem上。所以在綜合的警告里面會提示:?

?

?

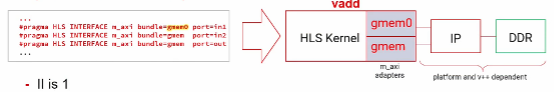

以上代碼在進行了c綜合后,我們所有的指針變量都會依據指令的設置映射到axi-master上,但是因為根據指令中所有的端口都綁定到了一條總線gmem上。所以在綜合的警告里面會提示:?

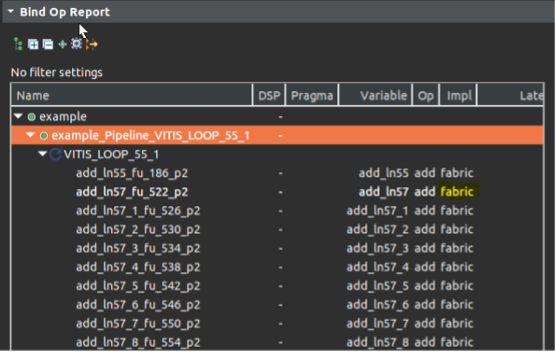

?WARNING: [HLS 200-885] The II Violation in module 'example_Pipeline_VITIS_LOOP_55_1' (loop 'VITIS_LOOP_55_1'):Unable to schedule bus request operation ('gmem_load_1_req', example.cpp:56) on port 'gmem' (example.cpp:56) due to limited memory ports(II = 1). Please consider using a memory core with more ports or partitioning the array.

因為在axi-master總線上最高只能支持一個讀入和一個寫出同時進行,如果綁定到一條總線則無法同時從總線讀入兩個數據,所以最終的循環的II=2。解決這個問題的方法就是用面積換速度,我們實例化兩條axi總線gmem和gmem0,最終達到II=1。 ?

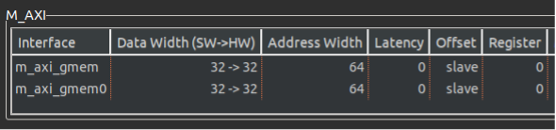

當總線數量滿足了我們并行讀入的要求后,讀取數據的位寬就成為了我們優化的方向:?

因為讀取的數據格式是int類型,所以這里的數據位寬就是32bit。

?

?

當總線數量滿足了我們并行讀入的要求后,讀取數據的位寬就成為了我們優化的方向:?

因為讀取的數據格式是int類型,所以這里的數據位寬就是32bit。

? ?

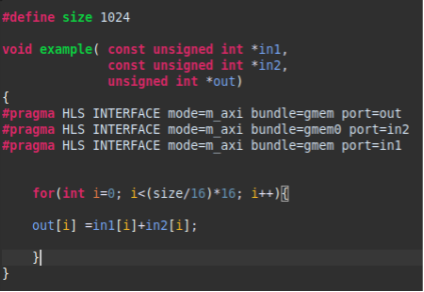

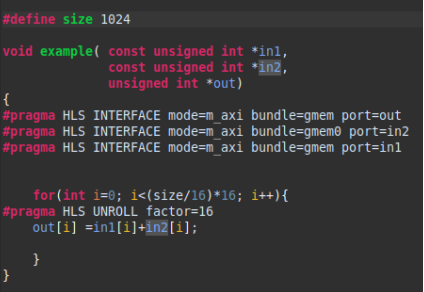

為了能夠轉移數據傳輸瓶頸,在Vitis kernel target flow中,數據位寬在512bit的時候能夠達到最高的數據吞吐效率。在Vitis HLS 中的新增了 max_widen_bitwidth 選項來自動將較短的數據位寬拼接到設定的較長的數據位寬選項。在這里我們可以將位寬設置到512bit的位寬,但是同時要向編譯器說明,原數據位寬和指定的擴展位寬成整數倍關系。這個操作很簡單,在數據讀取的循環邊界上,用(size/16)*16示意編譯器即可。

?

?

為了能夠轉移數據傳輸瓶頸,在Vitis kernel target flow中,數據位寬在512bit的時候能夠達到最高的數據吞吐效率。在Vitis HLS 中的新增了 max_widen_bitwidth 選項來自動將較短的數據位寬拼接到設定的較長的數據位寬選項。在這里我們可以將位寬設置到512bit的位寬,但是同時要向編譯器說明,原數據位寬和指定的擴展位寬成整數倍關系。這個操作很簡單,在數據讀取的循環邊界上,用(size/16)*16示意編譯器即可。

? ?

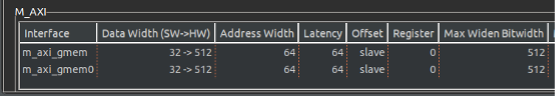

擴展位寬后的結果可以在綜合報告的接口部分看到數據位寬已經從32位擴展到512位。?

?

?

擴展位寬后的結果可以在綜合報告的接口部分看到數據位寬已經從32位擴展到512位。?

? ?

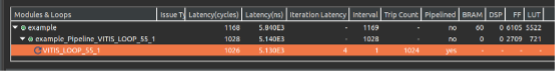

優化到這一步我們的設計可以進行大位寬的同步讀寫,但是發現循環的trip count還是執行了1024次, 也就是說雖然位寬拓展到512后,還是一個循環周期計算一次32bit的累加。實際上512bit的數據位寬可以允許16個累加計算并行執行。?

?

?

優化到這一步我們的設計可以進行大位寬的同步讀寫,但是發現循環的trip count還是執行了1024次, 也就是說雖然位寬拓展到512后,還是一個循環周期計算一次32bit的累加。實際上512bit的數據位寬可以允許16個累加計算并行執行。?

? ?

為了完成并行度的優化,我們需要在循環中添加系數為16的unroll 指令,這樣就可以生成16個并行執行累加計算的硬件模塊以及線程。?

?

?

為了完成并行度的優化,我們需要在循環中添加系數為16的unroll 指令,這樣就可以生成16個并行執行累加計算的硬件模塊以及線程。?

? ?

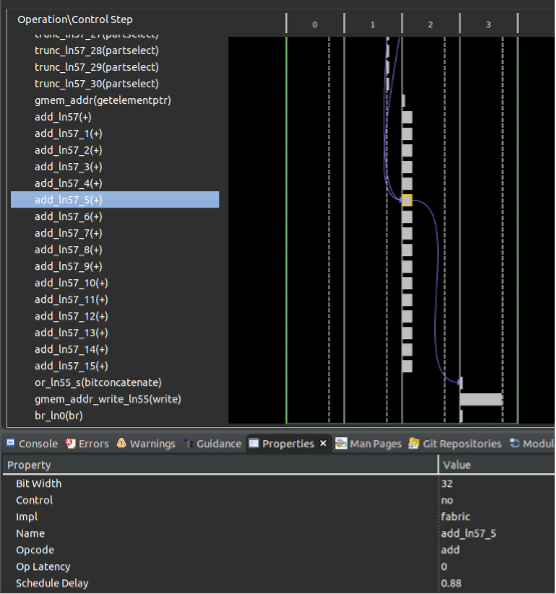

在循環中并行執行的累加操作,我們可以從schedule viewer中觀察到并行度,可以從bind_op窗口中觀察到operation實現所使用的硬件資源,可以從循環的trip_count 降低到了1024/16=64個周期,以及大大縮小的模塊的整個latency中得以證明。?

?

?

在循環中并行執行的累加操作,我們可以從schedule viewer中觀察到并行度,可以從bind_op窗口中觀察到operation實現所使用的硬件資源,可以從循環的trip_count 降低到了1024/16=64個周期,以及大大縮小的模塊的整個latency中得以證明。?

? ?

? ?

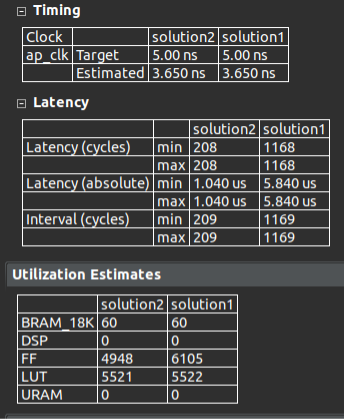

最后我們比較了一下并行執行16個累加計算前后的綜合結果,可以發現由于有數據的按位讀寫拆分拼接等操作,整個模塊的延遲雖然沒有縮短為16分之一,但是縮短為5分之一也是性能的極大提升了。?

?

?

最后我們比較了一下并行執行16個累加計算前后的綜合結果,可以發現由于有數據的按位讀寫拆分拼接等操作,整個模塊的延遲雖然沒有縮短為16分之一,但是縮短為5分之一也是性能的極大提升了。?

? ?

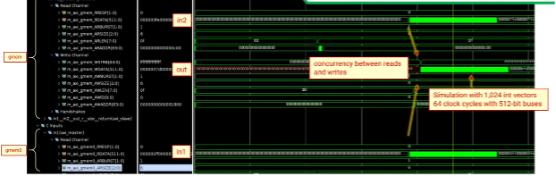

最后的最后,RTL級別的co-sim仿真才讓我們更加確信了數據的從兩個并行讀寫,循環執行的周期減小至了64個時鐘周期。?

?

?

最后的最后,RTL級別的co-sim仿真才讓我們更加確信了數據的從兩個并行讀寫,循環執行的周期減小至了64個時鐘周期。?

? ?

以上內容是設計者在AXI總線接口中使用傳統的數據類型時,提升數據傳輸效率和帶寬的一攬子有效方法:

?第一,擴展總線接口數量,以便并行讀寫。第二,擴展總線位寬,增加讀寫帶寬。第三,循環展開,例化更多計算資源以便并行計算。

本文的優化方式還是基于內核設計本身的,下一篇文章,我們將使用Alveo板卡做一些突發傳輸的實驗,深度定制傳輸需求,以真實仿真波形和測得的傳輸速度,從系統級別強化我們對于突發讀寫效率的認知。

審核編輯 :李倩

?

以上內容是設計者在AXI總線接口中使用傳統的數據類型時,提升數據傳輸效率和帶寬的一攬子有效方法:

?第一,擴展總線接口數量,以便并行讀寫。第二,擴展總線位寬,增加讀寫帶寬。第三,循環展開,例化更多計算資源以便并行計算。

本文的優化方式還是基于內核設計本身的,下一篇文章,我們將使用Alveo板卡做一些突發傳輸的實驗,深度定制傳輸需求,以真實仿真波形和測得的傳輸速度,從系統級別強化我們對于突發讀寫效率的認知。

審核編輯 :李倩-

接口

+關注

關注

33文章

8575瀏覽量

151021 -

靜態

+關注

關注

1文章

29瀏覽量

14542 -

代碼

+關注

關注

30文章

4779瀏覽量

68525

原文標題:開發者分享 | HLS, 巧用AXI_master總線接口指令的定制并提升數據帶寬-面積換速度

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

spi master接口的fpga實現

AMBA AXI4接口協議概述

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

有關PL端利用AXI總線控制PS端DDR進行讀寫(從機wready信號一直不拉高)

SoC設計中總線協議AXI4與AXI3的主要區別詳解

FPGA設計中,對SPI進行參數化結構設計

FPGA設計中,對SPI進行參數化結構設計

PCIe-AXI-Cont用戶手冊

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

電容6大特性參數,你知道幾個?

利用axi_master接口指令端的幾個靜態參數的優化技巧

利用axi_master接口指令端的幾個靜態參數的優化技巧

評論