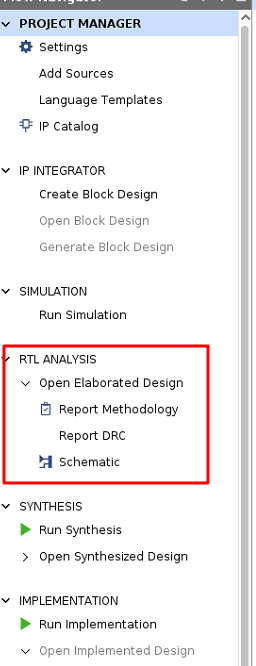

在FPGA設計里,設計仿真完成RTL代碼設計后便是交給設計套件進行綜合及布局布線。在綜合過程里,Vivado里提供的參數選項有點兒多,今天閑暇抽空梳理下。

-flatten_hierarchy

該參數提供三個可選項:

full:將我們整個設計層次打平,只保留頂層設計,對模塊間進行邊界優化(可以理解為我們整個設計被塞到一個Module里)。

none:完全保留設計原始層次,不執行任何邊界優化。該選項工具進行的優化最少,消耗的資源最多,層次保留最完整。

rebuild:在進行綜合時將原始設計打平,執行邊界優化,但將網表文件按照原始設計層次顯示。

對于在Verilog中使用的"keep_hierarchy"屬性優先級高于flatten_hierarchy。

gated_clock_conversion

在ASIC中門控時鐘用的比較多,而在FPGA設計中,門控時鐘并不是專用時鐘模塊生成,而且Vivado并不會對門控時鐘插入BUFG,在設計中應極力避免。該選項可將門控時鐘信號轉換為使能信號,從而避免門控時鐘的使用。該選項存在三個參數:

off:不允許門控時鐘轉換。

on:允許門控時鐘轉換,Verilog里添加“gated_clocked”的門控時鐘將會自動轉換。

auto:Verilog中添加“gated_clocked”的門控時鐘或者工具檢測到門控時鐘而且有相應可用的時鐘約束選項時將進行門控時鐘轉換。

當門控時鐘負載較少且時鐘頻率并不高時可以適當使用門控時鐘,但建議手動插入BUFG。

-fanout_limit

該選項用于設定信號所能承受的最大負載。該選項對于設計中的控制信號,如置位,復位和使能信號是無效的。

-fanout_limit只是一個宏觀指導原則,并非強制命令。如果需要很明確的對某個信號降扇出,應使用MAX_FANOUT而不是-fanout_limit。

MAX_FANOUT可應用于RTL代碼中,也可應用于XDC中,優先級高于-fanout_limit。當需要控制扇出的寄存器與負載不在同一層次時,flatten_hierarchy不要設置為none模式,否則將會無法生效。

-directive

Vivado提供的一些優化策略:

RuntimeOptimized:執行較少的時序優化及RTL優化以降低運行時間。

AreaOptimized_high:執行常規面積優化,包括強制執行三進制加法器,在比較器中使用新閾值以使用進位鏈以及實現面積優化的多路復用器。

AreaOptimized_medium:執行常規面積優化,包括更改控制集優化的閾值,強制執行三進制加法器,將推理的乘法器閾值降低到DSP模塊,將移位寄存器移入BRAM,在比較器中使用較低閾值以使用進位鏈,以及進行區域優化的MUX操作。

AlternateRoutability:通過算法提升路由能力(使用更少的MUXF和CARRYs)。

AreaMapLargeShiftRegToBRAM:檢測大型移位寄存器,并使用專用的Block RAM實現它們。

AreaMultThresholdDSP:減少DSP的推斷及使用。

FewerCarryChains:通過LUT使用降低進位鏈的使用。

-retiming

在不改變原始設計及功能時通過調整LUT和寄存器位置來進行時序優化調整。

-fsm_extraction

設定狀態機編碼方式,默認為auto,此時Vivado會自行決定最佳的編碼方式。

-keep_equivalent_registers

當勾選時,對于輸入的同源寄存器,綜合時將會被合成一個。如下例所示:

always@(posedge clk)begin rx<=a; ry<=a; r<=b;??resa<=rx & r;??resb<=ry^y;end

當該選項不勾選時,rx,ry將會被合并成一個寄存器。

-resource_shring

對算數運算符通過資源共享優化設計資源,有三個可選項:auto、on、off。設置為auto時,工具會根據時序要求進行調整。

-control_set_opt_threshold

觸發器的控制集由時鐘信號,復位/置位吸納后和使能信號構成,通常只有{clk,set/rst,ce}均相同的觸發器才可以被放在一個SLICE中。該選項將時鐘使能優化的閾值設置為較少的控制集。默認值為自動,這意味著該工具將根據目標設備選擇一個值。支持任何正整數值。

給定值是工具將控制集移入寄存器的D邏輯所需的扇出數量。如果扇出大于該值,則該工具嘗試使該信號驅動該寄存器上的control_set_pin。

-no_lc

使能該選項時,工具將不會嘗試LUT的整合。雖然LUT整合能夠降低LUT的使用,但也有可能導致布局布線擁塞。當“LUT as Logic”超過15%時,建議勾選該選項。

-no_slrextract -shreg_min_size

移位寄存器可以被綜合成LUT實現。-shreg_min_size用于管理移位寄存器是否映射為LUT,默認值為3.當移位寄存器的深度不超過-shereg_min_size時,最終采用移位寄存器實現,否則采用FF+LUT+FF形式實現。

-no_slrextract用于阻止工具將移位寄存器映射為LUT。優先級高于-shreg_min_size。

其他選項我們基本就用不上了,若需使用可參照ug901手冊。

原文標題:亂花漸欲迷人眼—Vivado之Synthesis

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

Vivado

+關注

關注

19文章

812瀏覽量

66470 -

RTL代碼

+關注

關注

0文章

4瀏覽量

6816

原文標題:亂花漸欲迷人眼—Vivado之Synthesis

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何在Vitis中把設置信息傳遞到底層的Vivado

Vivado for ZYBO無法提供該怎么辦?

Vivado的參數propragation有什么不同嗎?

Vivado 2017.1和Vivado 2016.4性能對比分析

深度解讀Vivado之Synthesis

關于Vivado non-project模式

Vivado中的Elaborate是做什么的?

簡述Vivado中的Elaborate的作用

Vivado綜合參數設置

Vivado IP核Shared Logic選項配置

Vivado設計套件用戶:使用Vivado IDE的指南

tcpdump常用的選項參數詳細總結

如何禁止vivado自動生成 bufg

每次Vivado編譯的結果都一樣嗎

Vivado提供的參數選項

Vivado提供的參數選項

評論