一、如何得到LUT與REG的使用比例 riple

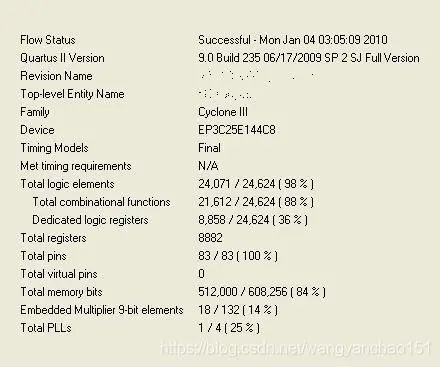

我們先看一個FPGA工程的編譯結果報告:

在這個報告中,我們可以看到如下信息:

Total logic elements 24071/24624(98%): 該芯片中共有24624個LE資源,其中的98%在這個工程的這次編譯中得到了使用。 riple

Total combinational functions 21612/24624(88%): 該芯片的24624個LE資源中,88%用于實現組合邏輯。 riple

Dedicated logic registers 8858/24624(36%): 該芯片的24624個LE資源中,36%用于實現寄存器,即時序邏輯。 riple

就是從上述信息中,我得到了組合邏輯與時序邏輯的使用比例——21612/8858 = 2.4:1。 riple

二、一份更詳細的資源利用率報告 riple

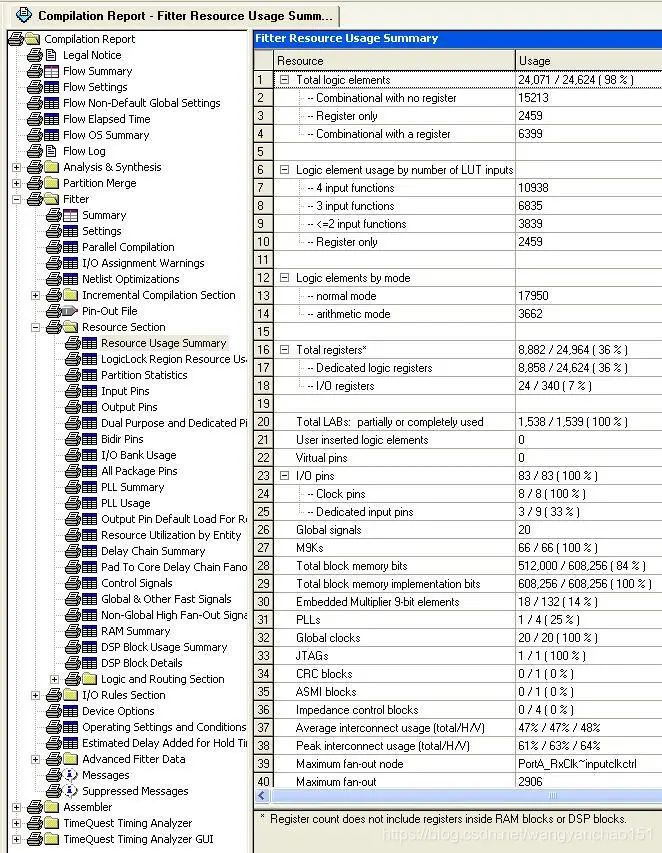

在這個報告中,有一點可能會令人困惑:為什么Total combinational functions與Dedicated logic registers之和(30470)大于Total logic elements(24071),甚至大于該芯片的總資源(24624)。我們再來看一份更詳細的資源使用報告——Fitter Resource Usage Summary:

這份報告包含很多信息,在這里我們只需要關心Total logic elements一項。Total logic elements 24071/24624(98%)由三種使用情況不同的LE資源組成:僅用于實現組合邏輯的LE(Combinational with no register 15213),僅用于實現時序邏輯的LE(Register only 2459),同時用于實現組合邏輯和時序邏輯的LE(Combinational with a register 6399)。 riple

三、從Resource Property Editor看LE的使用情況 riple

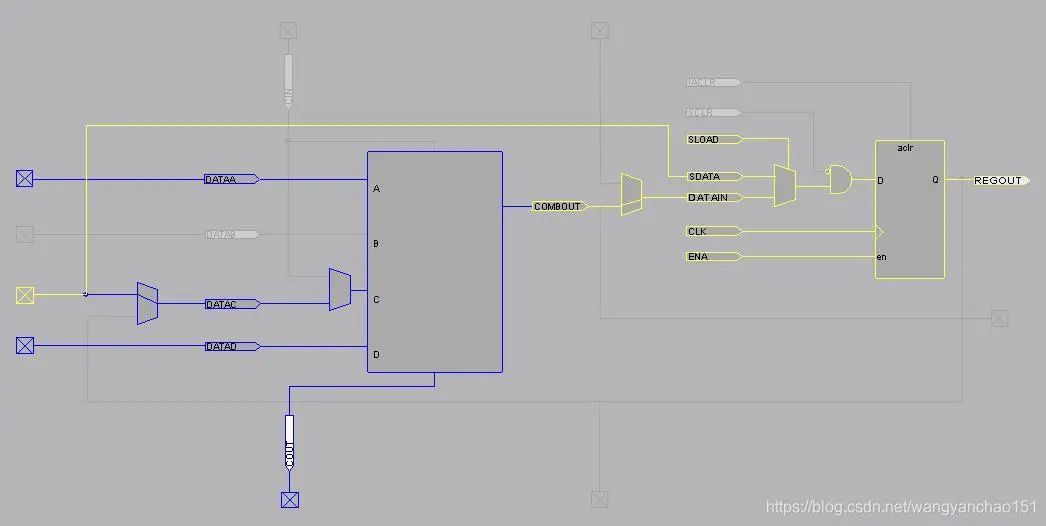

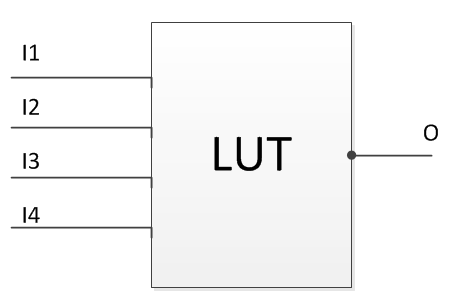

在進一步分析這些數據之前,我們有必要回顧一下FPGA的基本組成元素LE(Logic Element)的結構和功能。以Altera的Cyclone III系列FPGA芯片為例,其LE內部結構如下圖所示:

這個LE同時用于實現組合邏輯和時序邏輯,其中藍色部分為組合邏輯(一個4輸入LUT),其中黃色高亮部分為時序邏輯(一個D觸發器)。 riple

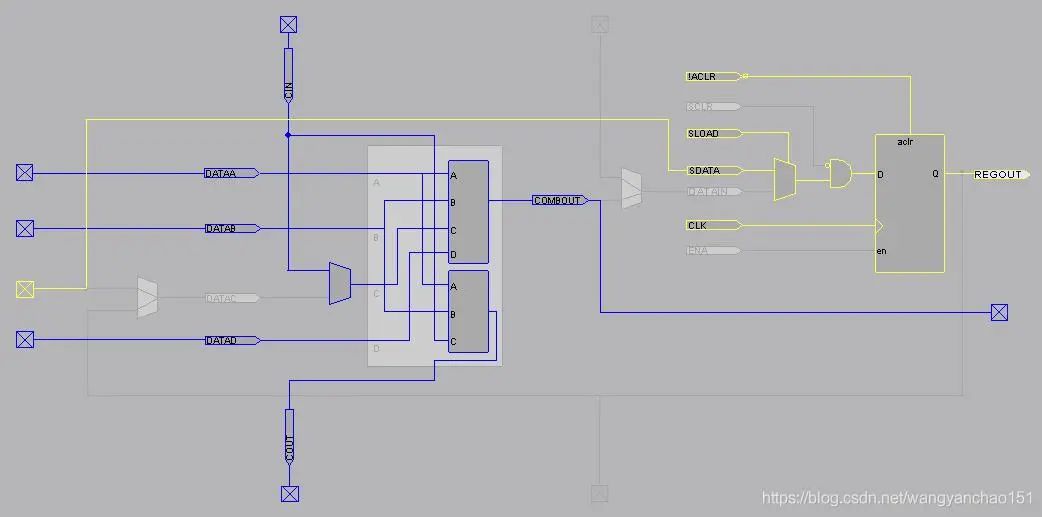

我們再來看一個更有趣的LE:

這個LE也同時用于實現組合邏輯和時序邏輯,與上一幅圖不同的地方在于,這里的組合邏輯(4輸入LUT)與時序邏輯(REG)并沒有連接關系。組合邏輯從COMBOUT直接輸出,時序邏輯從REGOUT輸出。這種互不相關的組合邏輯與時序邏輯共用同一個LE的情況很特殊,這是采用了Register Packing資源優化技術之后的實現方式。如果沒有采用這一資源優化技術,就要用兩個LE來分別實現相應的組合邏輯和時序邏輯。 riple

明白了上面這兩幅圖,大家也能由此類推,想象出僅用于實現組合邏輯的LE(Combinational with no register)和僅用于實現時序邏輯的LE(Register only)該是什么樣子。 riple

四、“數字終于對(湊)上了!” riple

我們回到前面關于資源利用率分析的部分。有了上面介紹的知識,大家應該能夠把資源利用率報告中三種使用情況不同的LE區分開了。 riple

我們把“同時用于實現組合邏輯和時序邏輯的LE(6399)”分別加到“僅用于實現組合邏輯的LE(15213)”和“僅用于實現時序邏輯的LE(2459)”上面,就可以得到“全部組合邏輯”(Total combinational functions = 6399 + 15213 = 21612)和“全部寄存器”(Dedicated logic registers = 6399 + 2459 = 8858)兩個數值了。這兩個數值就是第一幅圖中關于資源利用率的匯總報告結果,它們的比例恰好就是2.4:1。 riple

由于6399這個數字被使用了兩次,所以我們最初關于“Total combinational functions與Dedicated logic registers之和(30470 = (6399 + 15213) + (6399 + 2459))大于Total logic elements(24071 = 6399 + 15213 + 2459)”的困惑也得到了解答。 riple

五、總結 riple

由于FPGA設計中用到的組合邏輯與時序邏輯的數量不均衡,部分LE會僅用于實現組合邏輯或時序邏輯;進一步,由于布局位置的限制,單獨實現組合邏輯或時序邏輯的兩個LE可能不能合并到一個LE中實現。所以,在資源利用率報告中會出現三種使用情況不同的LE。 riple

由于過長的組合邏輯鏈(級聯的LUT)會引入較大的延時,而時序邏輯(REG)能夠把較長的組合邏輯鏈分割成較短的組合邏輯鏈,有效地縮短關鍵路徑和次關鍵路徑的長度,進而提高該FPGA設計的整體時序性能,所以組合邏輯與時序邏輯的使用比例可以作為評價一個FPGA設計時序性能的輔助參數。 riple

過于復雜的組合邏輯也會占用多個LE。我們在編寫HDL代碼的時候,不能單獨把減少Register的使用量作為節省資源的手段,而應該兼顧組合邏輯與時序邏輯,根據目標PLD器件的底層結構,編寫組合邏輯和時序邏輯比例符合PLD器件資源比例的代碼。 riple

原文標題:如何分析FPGA的片上資源使用情況

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1643文章

21956瀏覽量

614024 -

數據

+關注

關注

8文章

7239瀏覽量

90990 -

Reg

+關注

關注

0文章

20瀏覽量

11625 -

LUT

+關注

關注

0文章

50瀏覽量

12774

原文標題:如何分析FPGA的片上資源使用情況

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

應用于CNN中卷積運算的LUT乘法器設計

初識FPGA CLB之LUT實現邏輯函數

“按層次結構使用”中的LUT數量不正確

使用的LUT觸發器對的數量與Slice Register和Slice LUT的關系是什么?

如何計算FPGA的片上資源使用情況

請問如何將Memory LUT用作邏輯LUT?

LUT如何構成邏輯函數

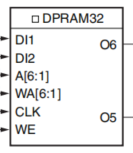

介紹SLICEM里的LUT如何形成RAM資源

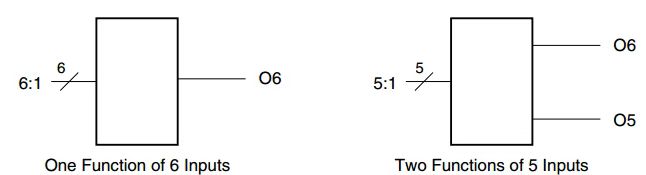

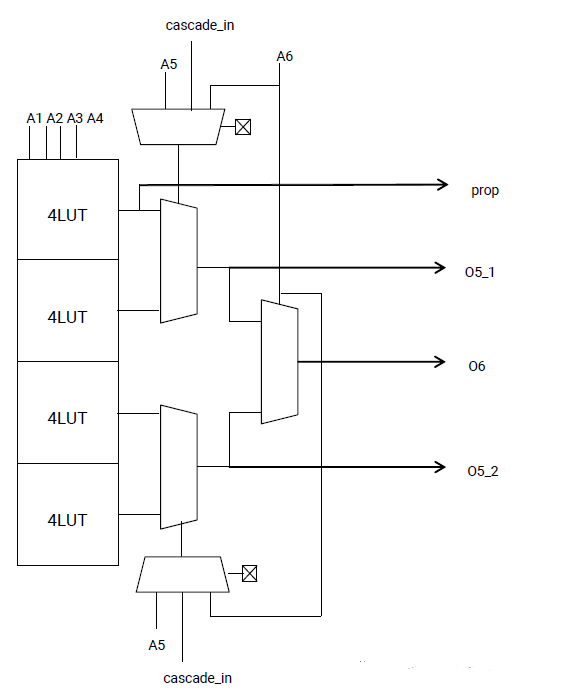

物理可級聯的LUT的優勢在哪?

MAX6345LUT+T PMIC - 監控器

MAX6827LUT+T PMIC - 監控器

MAX6828LUT+T PMIC - 監控器

評論