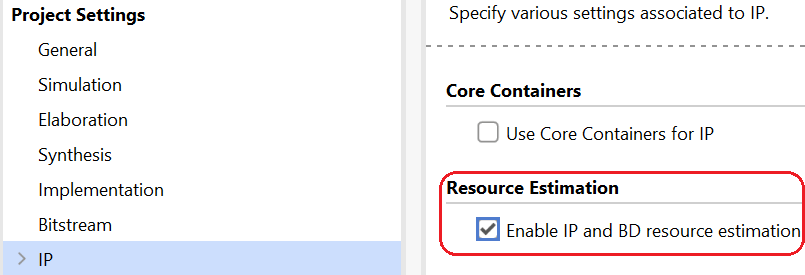

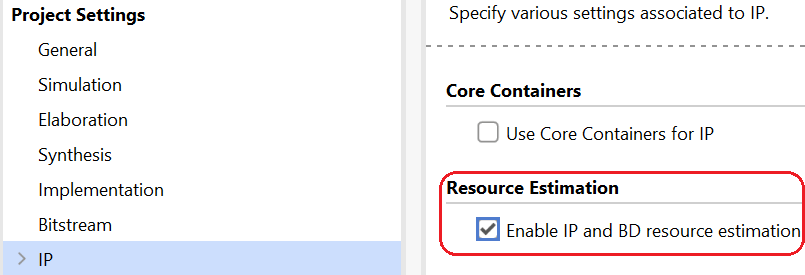

Vivado 2022.1已正式發布,今天我們就來看看其中的一個新特性。基于機器學習的資源評估對于Vivado IP Catalog中的IP,在2022.1之前的版本中我們只有在綜合之后才能看到其資源利用率。從資源評估的角度而言,信息是滯后的。Vivado 2022.1引入了基于機器學習的資源評估方法,在IP定制結束即可看到其資源使用情況。使用此功能需要首先勾選如下圖所示選項。

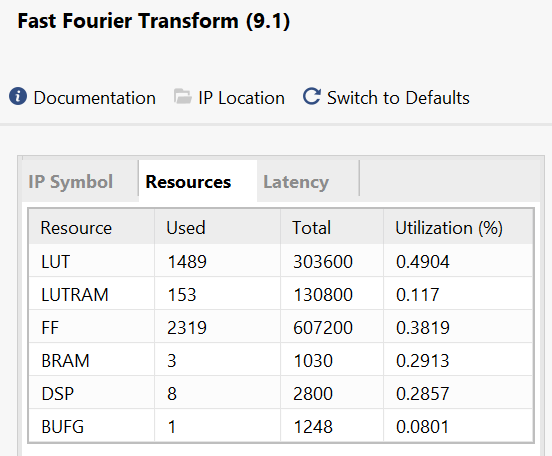

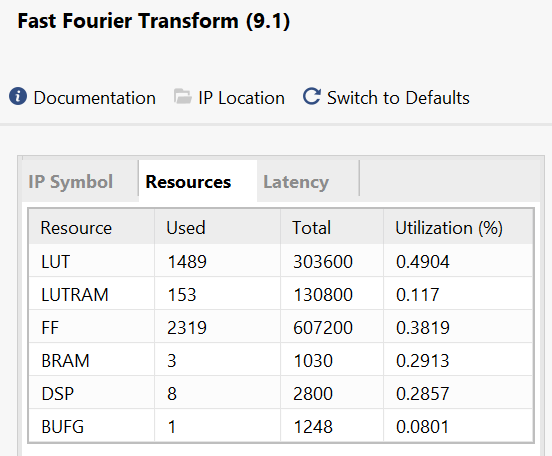

我們來看一個例子,打開FFT IP Core,填寫參數,即可在Resources下看到具體的資源利用情況,如下圖所示。

使用此方法,我們可以快速獲取IP的資源利用率,而不必等到對IP進行OOC綜合之后才能知道具體資源使用情況,這對于設計初期的資源評估很有意義。此外,此功能對于基于IPI(IP Integrator)的Block Design也是開放的。因此,對于BD中的IP也可以借助此功能快速獲取資源利用率。

原文標題:基于機器學習的資源評估

文章出處:【微信公眾號:TeacherGaoFPGAHub】歡迎添加關注!文章轉載請注明出處。

審核編輯:彭靜

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:基于機器學習的資源評估

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

相關推薦

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal Adaptive SoC 進行設計的重大改進。此版本為 AMD Versal 自適應 SoC

![的頭像]() 發表于

發表于 11-22 13:54

?297次閱讀

I Agree,然后點擊 Next: 選擇 Vivado HL System Edition(一般選擇這個設計套件比較完整,它比 Vivado HL Design Edition 多了一個 System Generator for DSP with Mat

![的頭像]() 發表于

發表于 11-16 09:53

?1115次閱讀

很多FPGA工程師都有這種困惑,Vivado每次編譯的結果都一樣嗎? 在AMD官網上,有這樣一個帖子: Are Vivado results repeatable for identical

![的頭像]() 發表于

發表于 11-11 11:23

?406次閱讀

vivado導入其他版本的項目的時候,IP核被鎖,無法解開,請問該如何解決。

使用軟件:vivado 2019.2

導入項目使用版本:vivado 2018

發表于 11-08 21:29

本博客提供了基于2023.2 Vivado的參考工程,展示如何使用Microblaze 地執行(XIP)程序,并提供一個簡單的bootloader。

![的頭像]() 發表于

發表于 10-29 14:23

?379次閱讀

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

![的頭像]() 發表于

發表于 10-24 15:08

?358次閱讀

,但是在Vivado里面打開用sublime寫的代碼之后,經常出現中文亂碼,讓人很不舒服。究其原因就是一般來說第三方的編輯器是采用utf8的編碼方式,而vivado的text editor不是這種方式。

![的頭像]() 發表于

發表于 10-15 17:24

?823次閱讀

隨著FPGA規模的增大,設計復雜度的增加,Vivado編譯時間成為一個不可回避的話題。尤其是一些基于SSI芯片的設計,如VU9P/VU13P/VU19P等,布局布線時間更是顯著增加。當然,對于一些設計而言,十幾個小時是合理的。但我們依然試圖分析設計存在的問題以期縮短編譯時間。

![的頭像]() 發表于

發表于 09-18 10:43

?1024次閱讀

從綜合角度看,Vivado 2024.1對SystemVerilog和VHDL-2019的一些特性開始支持。先看SystemVerilog。

![的頭像]() 發表于

發表于 09-18 10:34

?933次閱讀

Vivado 2024.1已正式發布,今天我們就來看看新版本帶來了哪些新特性。

![的頭像]() 發表于

發表于 09-18 10:30

?1417次閱讀

今天給大俠帶來Vivado經典案例:使用Simulink設計FIR濾波器,話不多說,上貨。

FIR(Finite Impulse Response)濾波器:有限長單位沖激響應濾波器,又稱為非遞歸

發表于 04-17 17:29

Xilinx Vivado開發環境編譯HDL時,對時鐘信號設置了編譯規則,如果時鐘由于硬件設計原因分配到了普通IO上,而非_SRCC或者_MRCC專用時鐘管腳上時,編譯器就會提示錯誤。

![的頭像]() 發表于

發表于 04-15 11:38

?5620次閱讀

在設計過程的每個階段,設計者均可以打開Vivado集成開發環境,對存儲器中保存的當前設計進行分析和操作。

發表于 04-03 09:36

?1041次閱讀

將設置設計的輸出路徑,設置設計輸出路徑的步驟如下所示。 第一步:如圖4.3所示,在“Vivado%”提示符后輸入命令“set outputDir ./gate_Created_Data/top_output”。

發表于 04-03 09:34

?1751次閱讀

電子發燒友網站提供《使用P4和Vivado工具簡化數據包處理設計.pdf》資料免費下載

發表于 01-26 17:49

?0次下載

Vivado 2022.1的新特性

Vivado 2022.1的新特性

評論