01

評估階段

Intel & AMD 等芯片廠商每年會發布一款新平臺Design guide,各大生產商會在接下來的6~9個月,或者更快的時間內設計出相關產品,搶占市場。針對消費類的產品,唯快不破!

離開Samsung前做的最后的一個平臺

MRT市場會根據市場調研以及最新平臺的新功能,給到研發中心一個設計需求及相關高低配置。消費類產品一般有高低價位,針對PC,高低配的差別,除了存儲容量,更大的體現于獨立顯卡和集成顯卡。當然,消費者關注的外表材質,也會因為配置而有所不同。

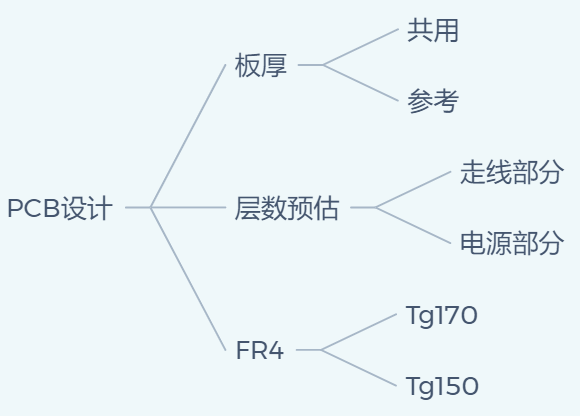

一、PCB設計

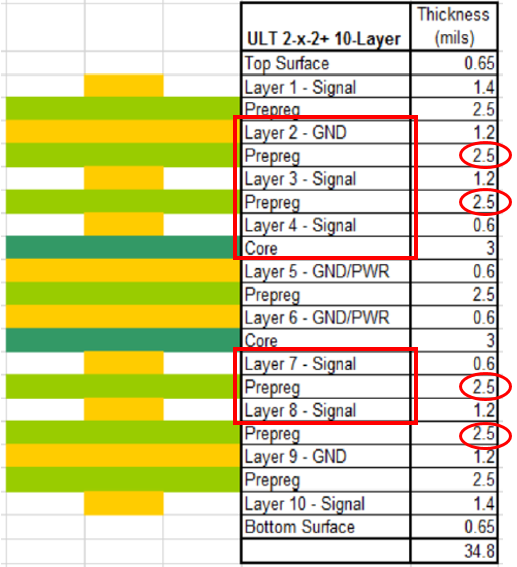

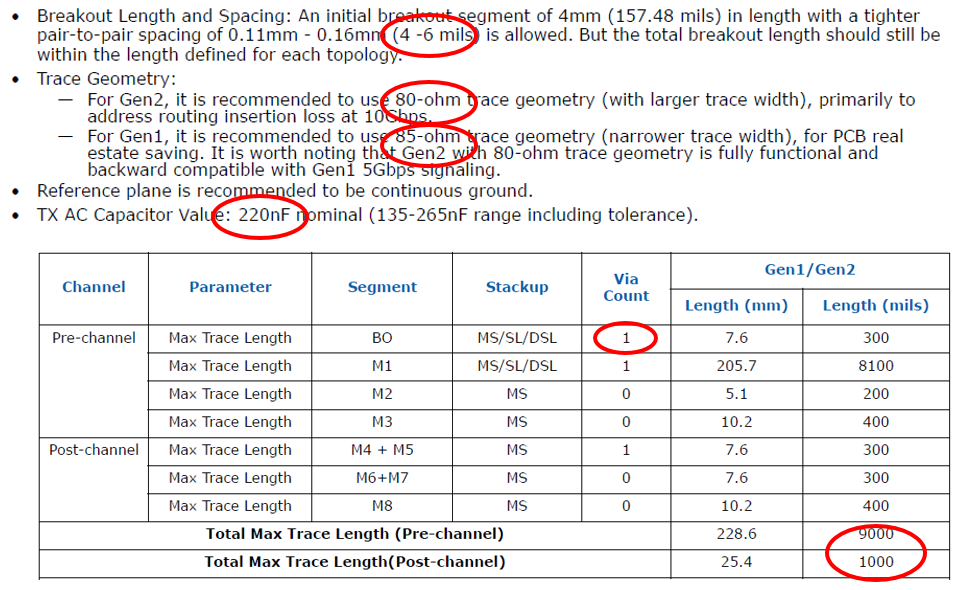

機構工程師會根據平臺資料和先行評估,給到我們一個PCB板的厚度范圍。如果這個范圍在先期的平臺中有使用過的機種符合,我們會盡量共用之前的PCB板厚和疊層,共用的主要好處是在PCB生產過程中的阻抗管控,特別是回板周期的保證。

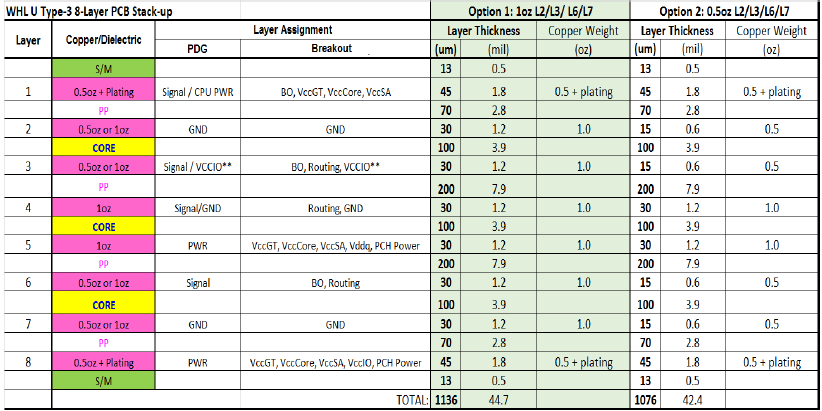

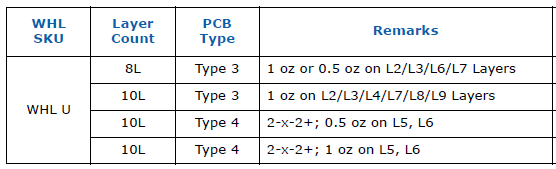

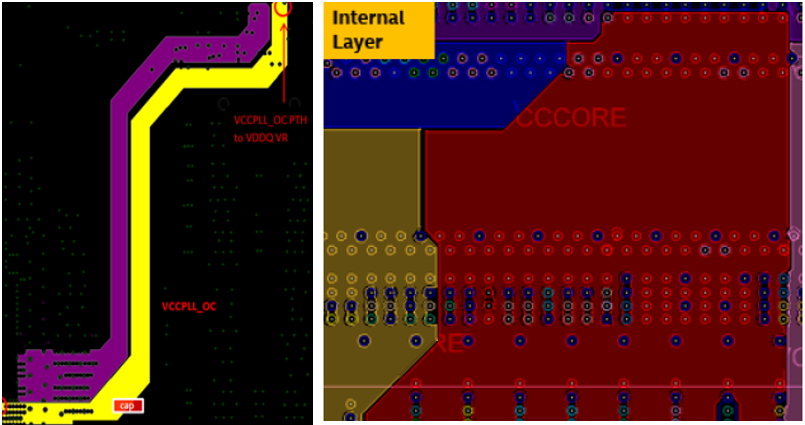

如果不能共用,我們會參考平臺設計規范中給出的疊層,下圖為8-Layer參考疊層:

當然,平臺也會給出不同板厚不同疊層的多種選擇:

這樣,各家廠商會根據自身產品的定位和配置來做出選擇。

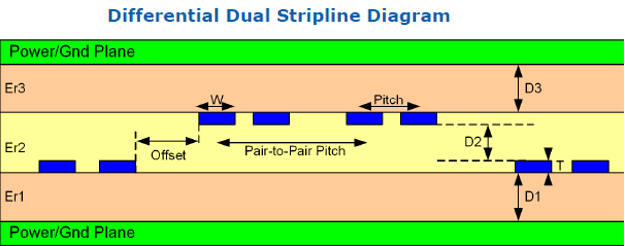

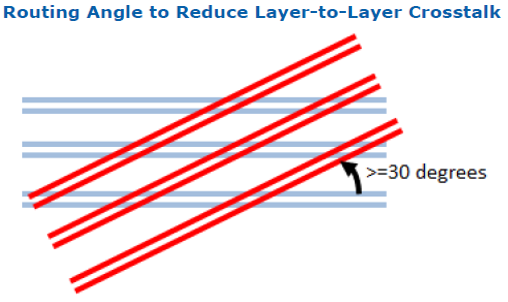

需要指出的是,不同于高速產品(服務器&交換機等),消費類產品特別是Notebook是走線密度特別大的,經常會走雙帶線。針對上下層的串擾,只是給出走線Overlap建議,根本沒有提到返回路徑完整性。

30度的建議看起來容易,其實Layout操作起來還是很麻煩的。針對Overlap重復度,之前還做過相關設計經驗總結,現在應該不適用了。

從WHL平臺開始,市面上出現了很多游戲本和超極本,為了追求產品的超薄,需要管控PCB板厚,也就需要控制介質厚度,沒有所謂的遠端參考,更多地需要對完整地平面做各種切割來保證電源完整性。

等到轉換賽道,從事更高速率的產品設計中,這些操作是不敢想象的。產品的不同,側重點也有所不同,認知也有所不同,這正是一葉障目。

走線部分:

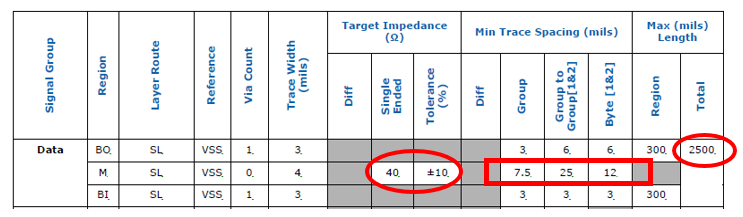

根據阻抗軟件算出差分阻抗的線寬線距,內存和顯存單端阻抗的線寬。然后根據走線guide來評估走線范圍是否滿足走線間距及相互間距的要求。其實也就是滿足Inter pair& Intra pair,至于其他雜線間距的要求都是可調的。

內存和顯存走線也按照這種方式方法進行預估,其實內存和顯卡的走線相對固定,只是可能因為配置不同,走線數量(DQ&CMD)的變化而增加層數而已。

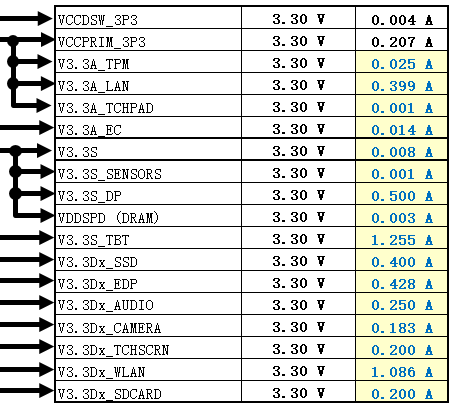

電源部分:

對各部分電源進行簡單分層,重點關注電流負載需求大的CORE電,需要考慮不同層面的結合與轉換,來保證其電源完整性。

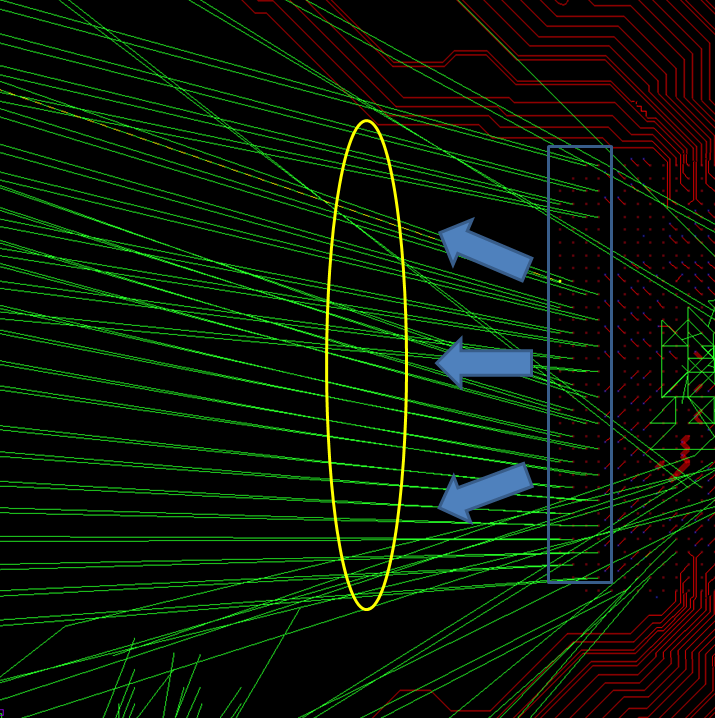

上面的步驟都是前期布局預估,布線層數還沒完全確定。這時候需要Layout工程師來做相關工作:高速信號狹窄部分走線;內存和顯存擺放大器件;鋪選電源路徑。

通過這些工作,來最終確定PCB板層數。根據確定的層數,我們最終確定板厚和疊層。

至于板材的選擇,因為消費類產品成本的限制,一般不會有損耗要求,只會給出FR4 的Tg,讓板廠自行決定選材,印象中,有使用過TU768。不管板廠選擇什么板材,必須進行相關阻抗的管控,特別是針對內存的單端線阻抗管控,內存相關的Margin 測試管控比較嚴格。

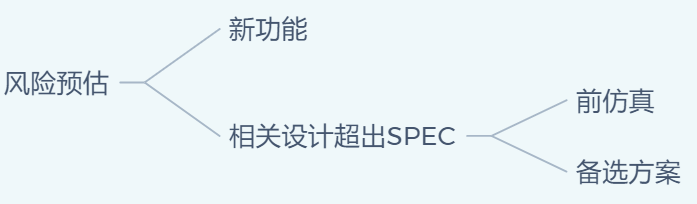

二、風險預估

各個工種會根據自身的設計規范給出風險預警。針對信號完整性這邊,無非就是板型的限制造成信號線長不符合要求,走線空間不符合要求等等。一般新平臺的新功能,因為沒有設計經驗,比如WHL Type C 的充電功能、Thunderbolt功能等都會預警。如果時間上來得及,會對一些風險點進行前仿真,如線長超出SPEC。

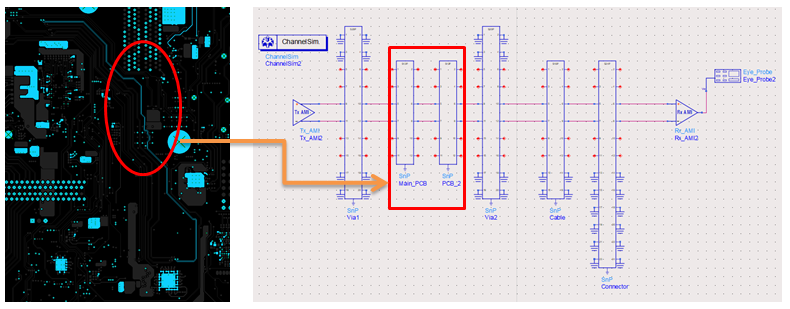

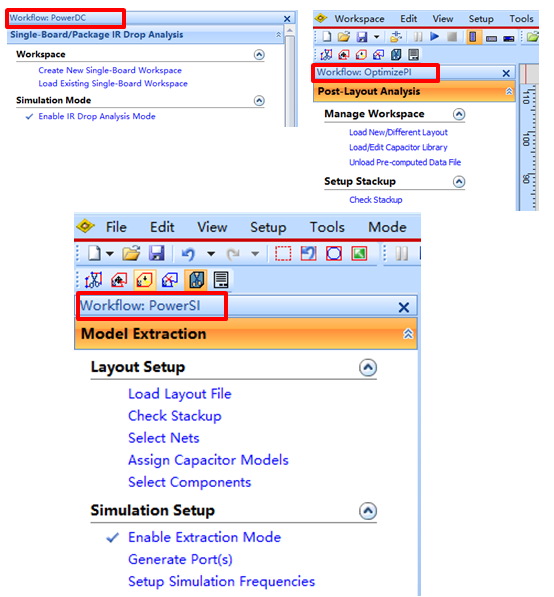

比如,設計中有PCIe信號超過SPEC或者經驗值。Layout工程師先行設計出相關部分的走線,然后用PowerSI提取出S參數,用ADS模擬鏈路搭建,仿真出結果。

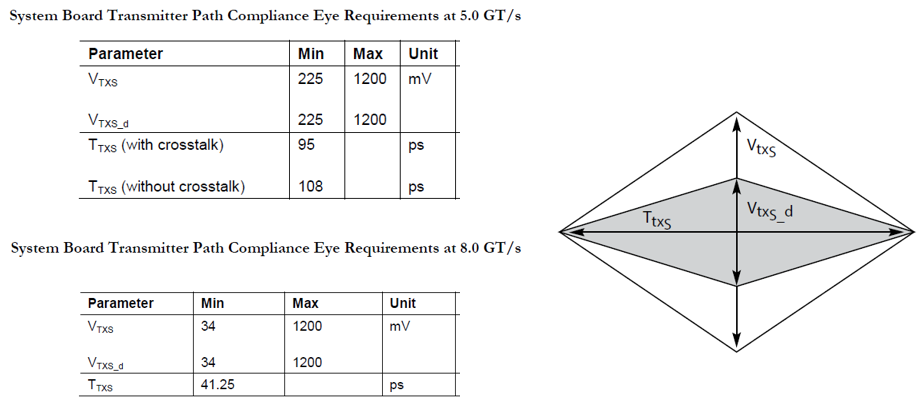

將得到的眼圖及相關指標,與協議規范的標準或者模板進行對比,來衡量是否符合標準。不符合的情況下,評估風險級別。

針對相關的風險點,給出備選方案。

02

設計階段

進入設計階段,需要輸出詳細的設計規則給到Layout 工程師。設計細則有很多,很多公司也大同小異,每個公司也會有相應的文檔格式和輸出。

一、信號部分

這部分我們重點關注的是高速線、內存&顯存的部分:

高速線(PCIe,USB,HDMI,SATA)差分阻抗線寬線距,組內&組間距離(Inter pair &Intra pair)。

內存&顯卡的阻抗(40?&50?)及組內&組間距離(16mil);

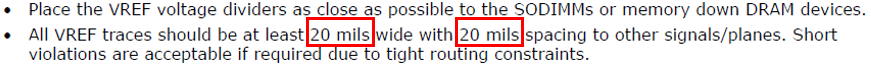

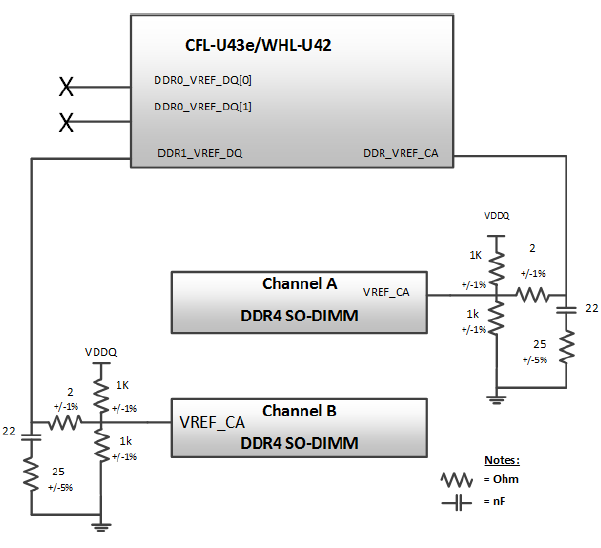

Reference Voltage(VREF)

除了上面重點部分,其他信號走線的規則,比如電源部分與信號線的距離以及一些其他相關規定,這里就不一一列舉了。

二、電源部分

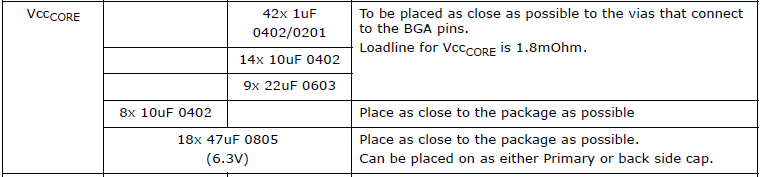

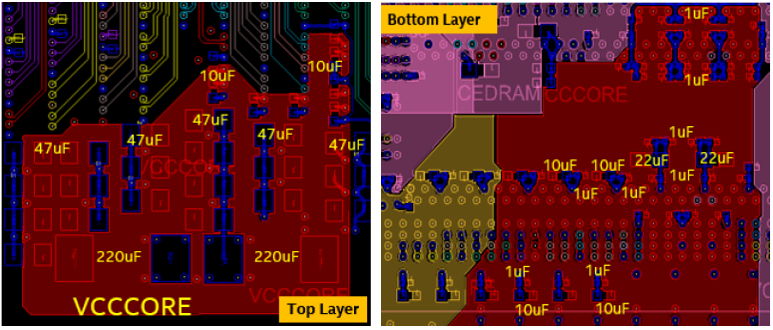

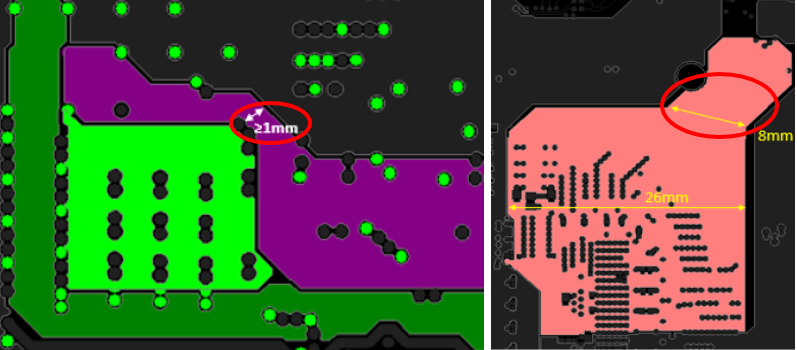

電源部分我們重點關注兩點:電容擺放&電源路徑。

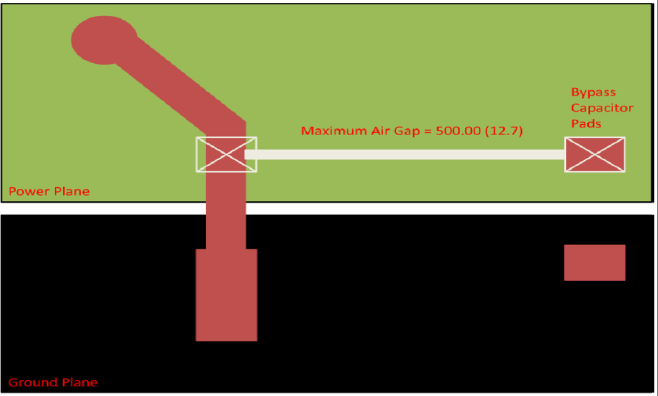

電容擺放:

我們需要先確定去耦電容的種類和大體數量,然后框選去耦電容的擺放范圍。擺放原則一般遵循去耦半徑范圍大小來擺放。小電容靠前,大電容靠后,有空間擺放的時候,也可以考慮部分大電容靠前,來防止電壓過沖保護。這里前后的概念是基于終端用電Pin區域來說的。

去耦電容的數量部分,在后期產品量產后,會對其進行優化。減少電容數量,來降低產品成本。電容數量的減小,可以通過電容優化仿真和結合后期電源紋波測試的margin來評估。

電源路徑:

先期我們會根據相關設計規范文件,找出各部分電源的最大承載電源,根據承載電流做出電源樹(Power Tree),來評估和確定主次路徑電流大小。

根據電源樹,來分配各部分電源大體的主次路徑。協調各層各部分電源的鋪墊方式及大小。一般按40mil/1A的電源來預估電源Shape的寬度。針對有些電的負載比較,一般考慮在內層給于補充,來保證其負載,同時在轉換電源層的時候,要注意打孔的數量。銅皮1oz,Via10過孔通流在1A預估。

這里需要特別強調的是:整個電源路徑,一定要關注其狹窄部分,這部分特別影響通流能力。比如5V的電,跟后期測試相關節后的IR Drop有很大的關系。

三、設計檢查

PCB Gerber前檢查的條目也很多,每個公司也會有自己的Checklist。信號方面主要是HSD相關高速線的檢查。

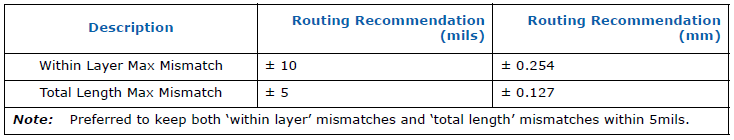

線長匹配檢查:

我們會輸出一個等長表格,來確保整個高速線的匹配。

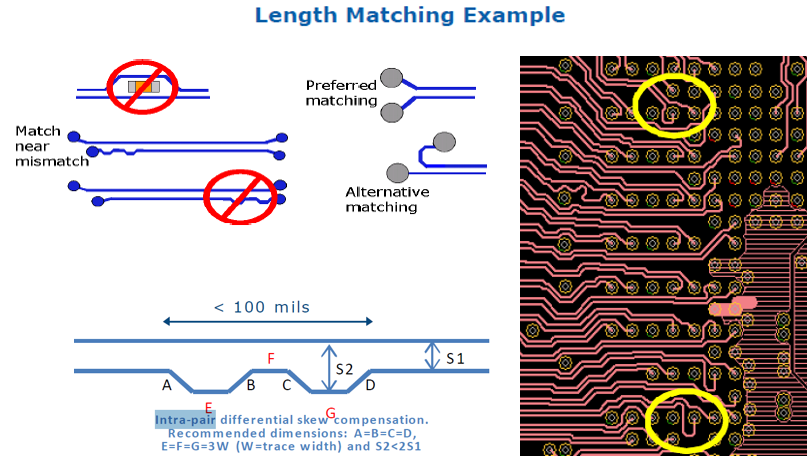

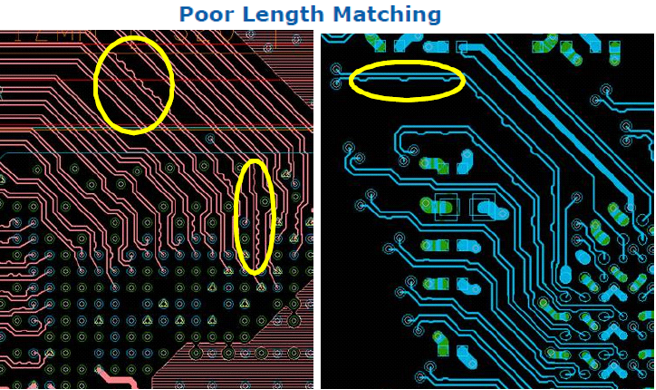

匹配方式:

會給出參考線長匹配方式及一些差的匹配方式:

路徑檢查:

保證走線路徑相互對稱,轉換過孔處有回流地孔,遠離干擾源(如電源)等。

03

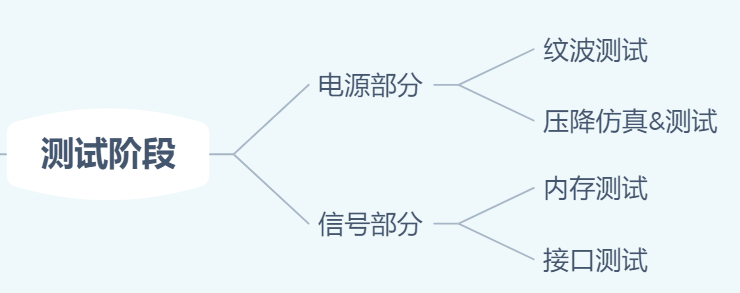

測試階段

PCB Gerber之后,一般在10~15天回板。這段時間,需要整理相關資料,準備測試階段的工作。

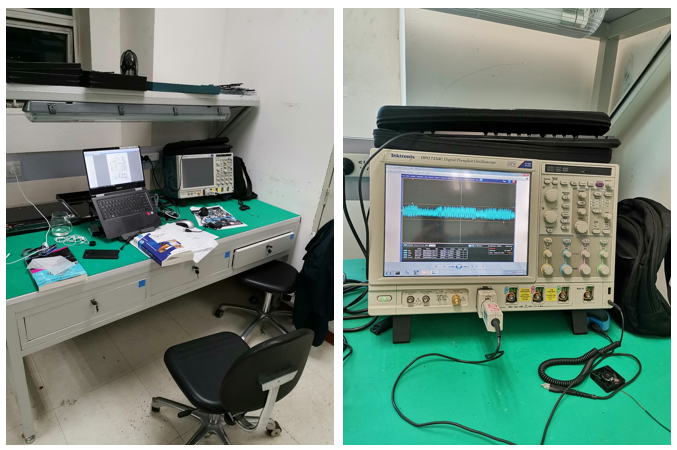

因為消費類產品的時效性,測試的時間一般在10~15天。測試的Item很多,時間關系,一般只測高配版本。一般這段時間會一直耗在實驗室,直到測試&問題解決才能出關坐回辦公室。

一、電源部分

電源測試的Item很多,這里只講講其中幾個。

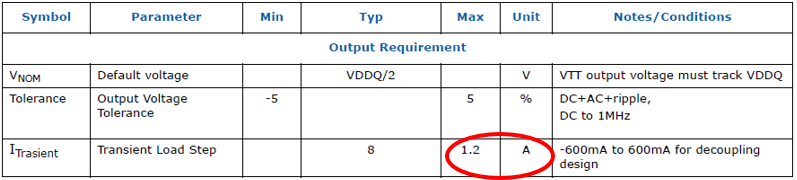

紋波測試:

電源紋波測試量很大,需要讓測試主板在高性能狀態,一般會運行相關測試軟件,然后用示波器點測終端的耦合電容。同一個電不同容值,不同的電不同容值,都要點測。

紋波測試重點關注Pk-Pk值,終端的標準是+/-5%,源端+/-3%的標準,測試標準因產品而定。紋波測試的作用,除了終端電源的完整性,也為后期量產后,機種降成本(Costdown)設計提供測試數據。

如果有些電測試有問題,就得需要從源端、電源路徑、終端耦合電容的擺放等多方面找出問題,然后解決。

檢查電容擺放位置(0.5 inches)之內

降低成本:

量產后,可以結合OptimizePI,降低機種成本。通過OptimizePI仿真,可以優化減少耦合電容種類和數量。再根據紋波實測的結果,給出優化的結果。可以的話,通過相關的PCB測試板重工認證。不知道現在的版本有沒有更新優化的版本,能夠給出優化后電容擺放的范圍。

壓降測試:

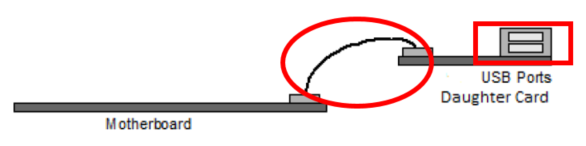

壓降測試的原因是PDN有阻抗,負載電流從源端到終端,會有壓降的產生。以USB3.0為例,終端的電壓值需要≥4.75V,才能保證終端設備的識別。特別是小板上的USB3.0接口。印象中,開發過一款產品,賣點就是小板上有USB3.0接口,因為要經過FPC Cable,接口的壓降問題就搞了很長時間。

IR Drop 壓降測試除了可以用軟件Power DC仿真跑出電壓值,還可以使用測試夾具抽載(USB3.0&1A,USB2.0&500 mA),測出終端的電壓值,看其是否符合SPEC。

針對Drop風險比較大的鏈路,PowerDC搭建仿真,根據仿真結果,給出風險預估。但是這種,只能針對主板帶終端接口的鏈路。PowerDC搭建仿真,是沒辦法導入FPC Cable模型,來預估帶Cable 的壓降,不知道現在版本,可不可以導入使用。

PI 仿真三大件

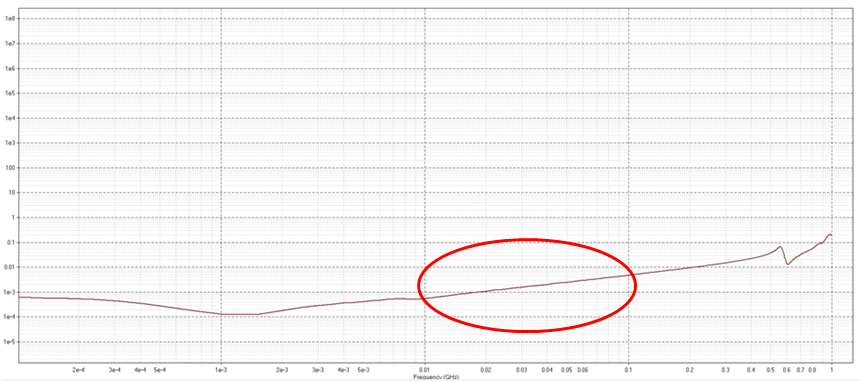

PowerSI 提取AC PDN 電阻,不同于高頻段的噪聲由芯片過濾, PCB板耦合電容作用于兆級別。

二、信號部分

信號的測試不僅僅是高速信號相關測試,時鐘的部分也要進行測試(保持時間,建立時間等)。這里只講印象比較深刻的幾個。

內存測試:

一般默認VREF的電為System Memory Voltage一半,比如DDR4是1.2V,即為600 mV。測試方法:將分壓電阻拿掉,用外部Power Supply 對其供電,以600 mV為基準,上下調節電壓值,同時運行Memory Stress Test。一般測試時間≥2H。一直降低或提高測試值,直到測試Fail。此時測試值和600 mV的差值即可認為VREF Margin。

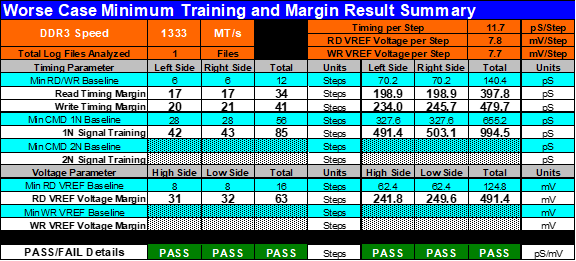

也可以通過Intel 給的關于DDR測試軟體工具RMT(Rank Margin Tool) 。BIOS打開Debug port,測試軟件通過修改內部設置, 讓其開機時自動運行Training程序, 同時通過Debug Port輸出Training的結果,從而得到Memory Margin。如下圖,所得到的結果包含Write/Read Timing Margin,ADD/CMD Timing Margin等信息。也會對其結果做出是否PASS的判斷。關于RMT測試的詳細內容,可以參考Intel參考文檔。

DDR3的測試結果圖,印象中Timing Margin 的最小值是14

至于其他的點測就不一一列舉了。印象中,最痛苦的測試:用兩個7240測VCM。這個測試必須兩個人,一個人抓波形,一個人兩只手各拿一個7240探頭。先抓好波形,還要Count 200以上,這段時間手不能動,必須保持住。一般測下來,手都快廢了。

接口方面的測試就比較粗暴和直接。上了測試夾具就自動跑測試程序。

接口測試:

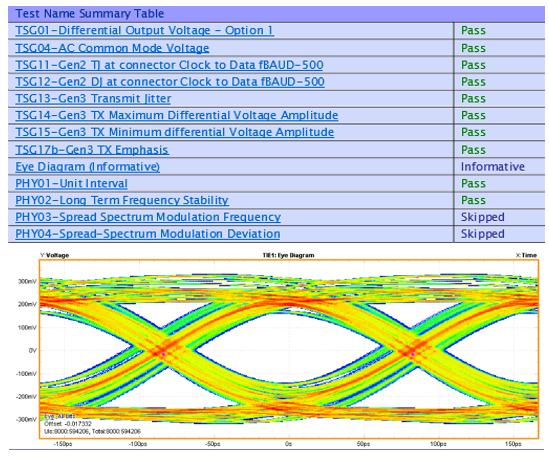

USB3.0,PCIe2.0&3.0等接口一致性測試,一般是對發送信號進行質量測試,一般看眼圖相關指標。

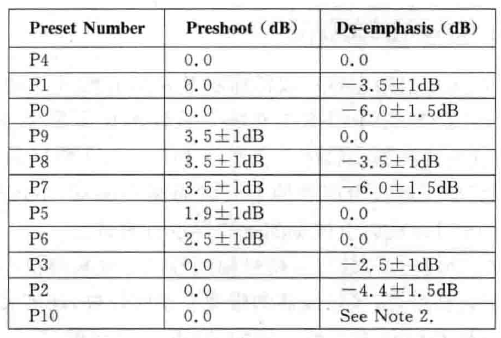

主板的BIOS會設定一個默認值,這個默認值可能是經驗值,也可能是設計規范根據線長范圍給出的一個參考值,如果測試眼圖顯示Fail,會通過修改發送端的預加重或者是接收端EQ(均衡)參數,來改善眼圖質量,讓其滿足相關協議規范測試標準。

根據測試結果,選擇一個設置值,BIOS工程師將其設定,供新的版本使用。

PCIE3.0預加重的組合

HDMI

不同于其他接口,想講一下HDMI接口,也可能是現有的工作對這個接口的關注越來越少了。現有顯示產品都支持HDMI接口,HDMI接口的普及度和重視程度在消費類產品中也越來越高。

記得當初有人還整理了一份HDMI接口各種分辨率及對應各種幀頻。后來有的顯示產品號稱支持4K,一看支持的最大幀頻,就默默走開了。

當時1.4標準比較常見,現在2.0標準應該普及了吧。2.0標準可以支持4K x 2K ,最大幀頻到60 Hz。現在HDMI2.1的標準都出來了,都能支持48 Gbps, 支持4K120Hz的畫面傳輸。

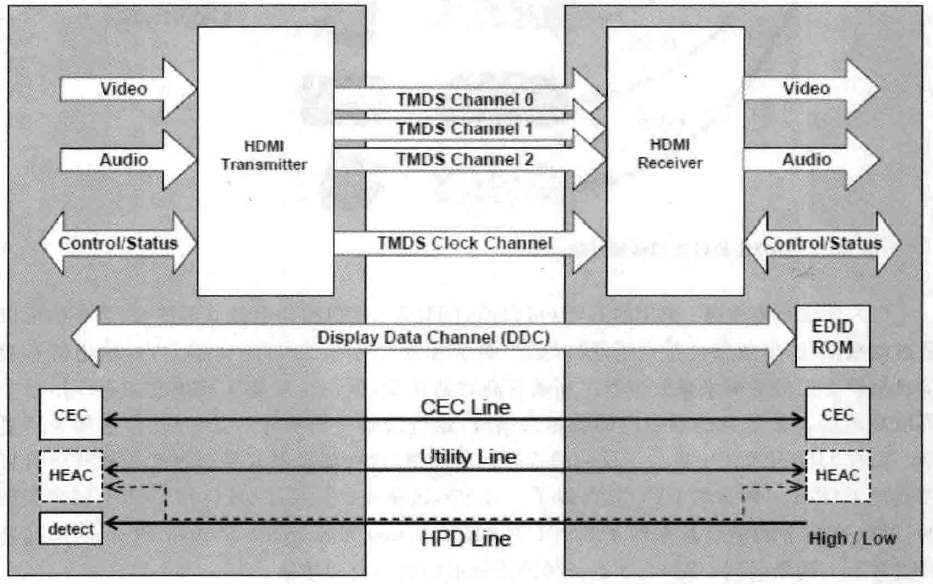

TMDS( Trans it ion Minimized Differential Signa l ing)

最小化傳輸差分信號傳輸技術。TMDS是一種微分信號機制,采用的是差分傳動方式。看到TMDS,就想起LVDS,都有抗干擾能力。至于兩者的區別,這里就不做展開了。

TMDS使用的也是8b/10b編碼技術,但其編碼方式和PCIe&SATA等串行編碼方式不同,通過特殊的編碼來減少視頻信號傳輸時信號線上的跳變邊沿從而控制對外的電磁輻射,同時又可以保證接收端正確的時鐘鎖定。

一個HDMI包括3個TMDS數據通道和1個TMDS時鐘通道

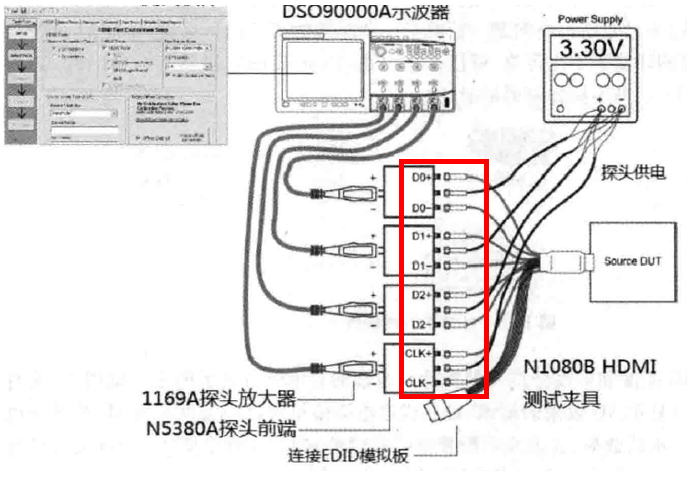

HDMI 的測試需要對高分辨率&低分辨率以及不同分辨率下不同幀頻的測試。下圖紅色標記處需要手動擰下再交叉擰上,來測試不同組合。這玩意戴上手套接口就不好擰緊,影響測試結果。光手擰,如果測得不順利,后果比較嚴重。手疼真記憶猶新。

HDMI的測試需要專門提供一個3.3 V的電源,直流偏置來保證信號的輸出。這也是跟其他接口測試不一樣的地方。

測試階段流程圖:

測試結束后,整合相關測試報告上傳系統。如果測試中有Fail項目,需要給出相關原因,提出解決或者優化方案。

04

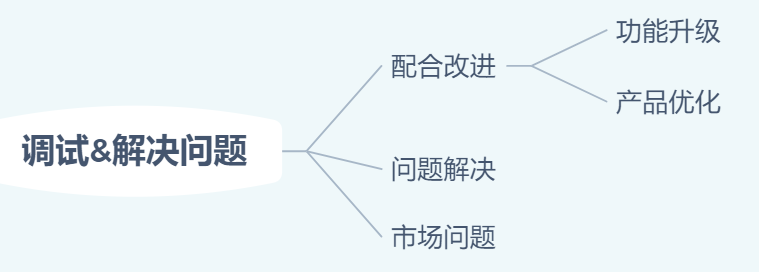

調試和解決問題

一、配合改進

別的工種需要優化和修改,或者導入和支持新的部件,涉及到高速線號部分,我們需要進行相關調試及測試認證,來配合產品優化及功能升級。

二、問題解決

高速信號方面的測試,如果遇到Fail的項目,就需要Debug。如果確認需要修改或者優化版圖來解決,需要盡快將修改建議統一格式,上傳系統。Layout工程師修改優化Layout后,需要我們確認修改是否符合要求,并在系統確認。

回板后,需要再次測試驗證,確認是否解決之前階段的問題。

三、市場問題

產品上市后,會有市場問題。高速信號完整性相關的問題,比如USB3.0接口不識別、HDMI不支持高分辨率等問題,都需要我們來確認、分析與解決。

總結

其實,上面所寫的幾個階段內容,是經過修改整理的。實際的機種劃分階段,肯定跟這個大有不同。只不過信號完整性工程師的工作內容大體就是這些,大同小異。疑難雜癥的問題就另當別算了。如果說硬件工程師是原理圖上功能的實現,信號完整性工程師更多的是PCB板級信號質量的管理。隨著產品速率的高速化及復雜化,信號完整性工程師將越來越……

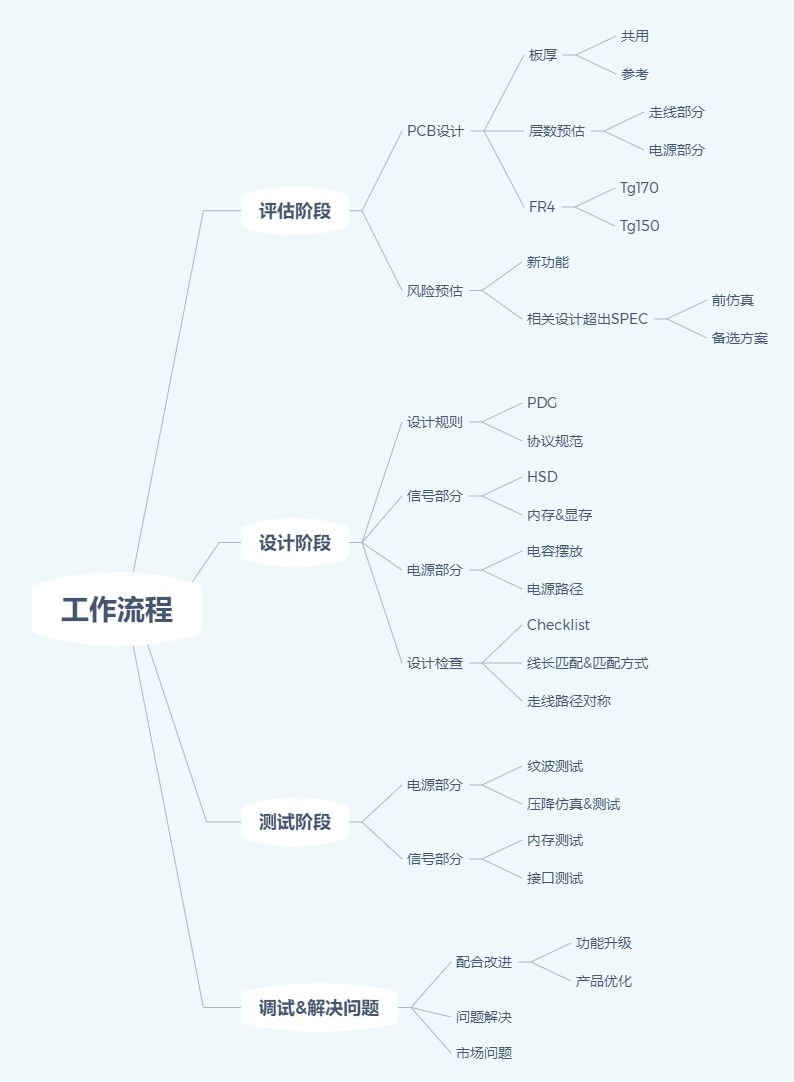

工作流程詳細圖

原文標題:5000字圖文,詳解SI信號完整性工程師工作流程

文章出處:【微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

-

pcb

+關注

關注

4322文章

23124瀏覽量

398510 -

HDMI

+關注

關注

32文章

1718瀏覽量

152062 -

接口

+關注

關注

33文章

8639瀏覽量

151385 -

TMDS

+關注

關注

1文章

22瀏覽量

15520

原文標題:5000字圖文,詳解SI信號完整性工程師工作流程

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB板級信號質量的管理

PCB板級信號質量的管理

評論