開源ISP-xkISP

介紹

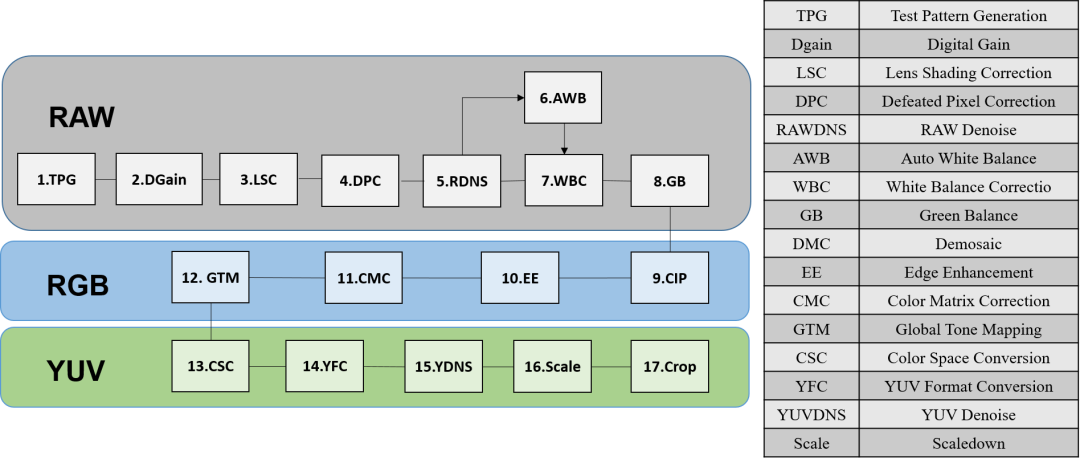

xkISP 是基于 Xilinx HLS 的開源圖像信號處理器 (ISP)。xkISP由復旦大學VIP實驗室和阿里巴巴DAMO CTL實驗室聯合開發。到目前為止,xkISP 支持處理任意分辨率的 12 位原始圖像數據。整個流水線包括17個功能模塊,如下所示:

ISP算法及架構分析介紹

文件結構

xkISP ├─fpga │host.cpp │top.cpp │top.h │xcl2.cpp │xcl2.h │ ├─src │isp_top.h │file_define.h │"*module*".cpp │"*module*".h │... │ ├─tb │tb_"*module*".cpp │... │ ├─tcl │Makefile │"*module*".tcl │"*module*"_directives.tcl │... │ ├─tv │Makefile │hls_param.txt │input.raw │isp │readme_for_tv ├─LICENSE ├─setup_env.sh └─README.md

fpga包含用于集成驗證的代碼文件。

src包含源代碼文件,它們是 xkISP 項目的單個模塊和用于單個模塊測試的頭文件( file_define.h )。

《優秀的 Verilog/FPGA開源項目介紹(二十六)- ISP (圖像信號處理)》

tb包含用于在模塊級別驗證與 Cmodel( tv/isp )的功能一致性的代碼文件。

tcl包含用于執行tb ( " module".tcl ) 中的代碼文件并為src ( "module"_directives.tcl )中的代碼文件添加 pragma 命令的腳本。tcl中的 Makefile用于模塊級驗證。

tv包含用于生成測試向量的文件。可以閱讀readme_for_tv了解更多詳情。setup_env.sh用于指定開發工具。(Vitis HLS 或 Vivado)

原文標題:開源ISP-xkISP

文章出處:【微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

-

圖像數據

+關注

關注

0文章

52瀏覽量

11276 -

信號處理器

+關注

關注

1文章

254瀏覽量

25272 -

ISP算法

+關注

關注

0文章

3瀏覽量

6338

原文標題:開源ISP-xkISP

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+內容簡介

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+介紹基礎硬件算法模塊

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+一本介紹基礎硬件算法模塊實現的好書

AI ISP的技術優勢和市場前景

開源ISP(Infinite-ISP)介紹

RK3588的ISP流程問題

人員軌跡分析算法有哪些?

ISP數據在精確定位中的技術實現

如何防止ISP下載過程被監聽導致程序泄露?

詳解真4K內窺ISP硬件架構的實現方式

GD32 MCU ISP失敗的原因

ISP算法及架構分析介紹

ISP算法及架構分析介紹

評論