【摘要】本文結合某單板(下文中統(tǒng)一稱M單板)FPGA調試過程中發(fā)現地彈噪聲造成某重要時鐘信號劣化從而導致單板業(yè)務丟包的故障,來談下如何最大程度地降低地彈噪聲對單板信號完整性影響。

一、故障現象

M單板在進行業(yè)務調試時發(fā)現:如果只有上行方向有業(yè)務,上行業(yè)務正常無丟包;如果只有下行方向有業(yè)務,下行業(yè)務也正常無丟包;如果雙向都有業(yè)務,下行業(yè)務丟包嚴重,上行業(yè)務正常。同時高溫情況下比常溫下丟包更加嚴重。

二、故障分析

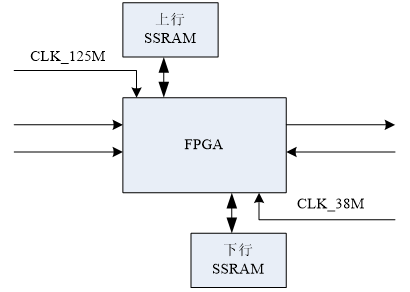

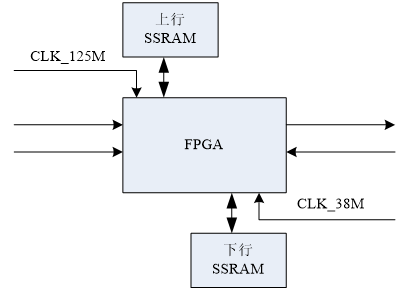

通過邏輯內部定位發(fā)現丟包地點為下行SSRAM讀寫處,即下行業(yè)務包寫入SSRAM,再讀出后包內容出錯導致報文丟棄。FPGA外掛SSRAM結構框圖見圖1,進入FPGA內部的上行業(yè)務和下行業(yè)務都需要通過各自的SSRAM進行緩存來實現一些功能。其中上行SSRAM的讀寫使用的是125M的本地晶振時鐘,而下行SSRAM使用的是38M系統(tǒng)時鐘。

圖1 FPGA外掛SSRAM原理框圖

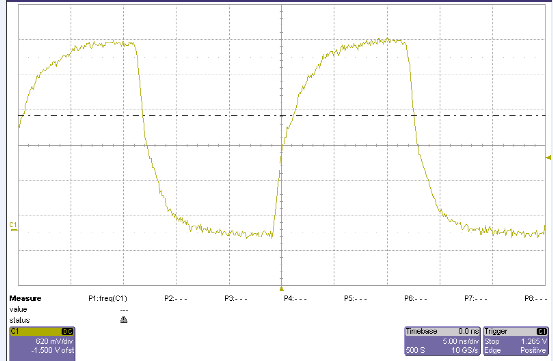

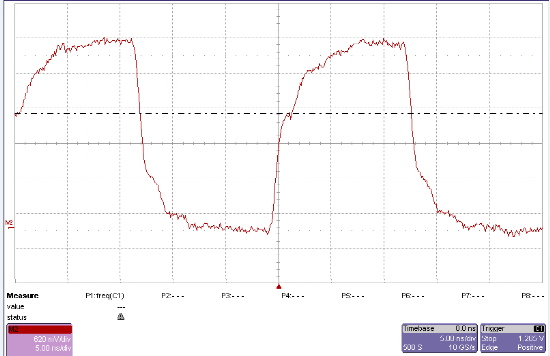

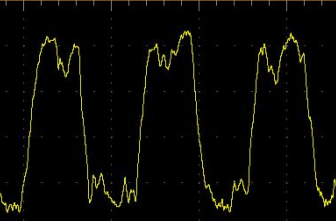

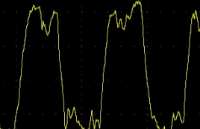

從故障現象來看,不是簡單的時序問題,因為單獨只有上行業(yè)務或下行業(yè)務時,業(yè)務都正常。而上下行同時有業(yè)務處理時,下行業(yè)務就會丟包,因此懷疑是上行的業(yè)務干擾了下行的業(yè)務。而下行業(yè)務受到干擾的最大可能就是下行SSRAM的時鐘信號受到了干擾。為了驗證此猜測,我們做的如下實驗:使用高速示波器測量CLK_38M時鐘,比較只有下行業(yè)務和上下行業(yè)務同時都有時的信號波形,看是否有區(qū)別。測試結果見圖2和圖3。比較可看出,只有下行業(yè)務時,時鐘信號質量很好,而上行業(yè)務也有時,時鐘的上升沿有一個明顯的回溝,而回溝的位置在2.0V左右,而2.0V是VIH的臨界電平,該回溝會導致FPGA誤判,這樣就會出現采樣點錯誤而導致采樣數據出錯。

圖2 只有下行業(yè)務時CLK_38M波形

圖3 上下行業(yè)務都有時CLK_38M波形

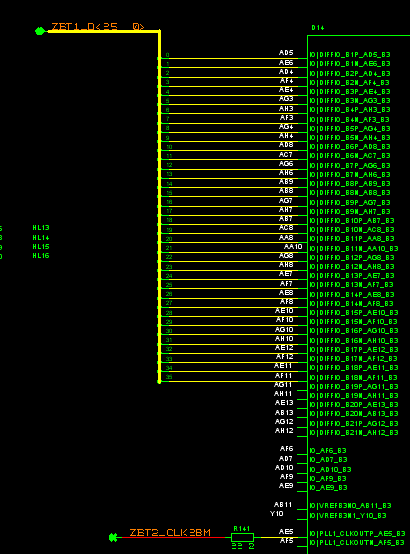

上行業(yè)務是怎樣影響到下行時鐘CLK_38M的呢?查看M單板的原理圖,發(fā)現CLK_38M和上行SSRAM的36根數據線在同一個I/O bank。那么最大可能便是上行SSRAM的數據線對CLK_38M進行了干擾。那么該干擾是FPGA內部的地彈噪聲造成的還是FPGA外部PCB走線造成的呢?為了驗證此問題,又做了2個實驗。實驗1:將圖4中的R141去掉,然后在跟FPGA相連的電阻焊盤上飛一根線直接到SSRAM的時鐘管腳,經示波器測量后發(fā)現仍然存在干擾。實驗2:將圖4中的R141去掉,在FPGA內部將系統(tǒng)來的38M時鐘從另外一個bank的空余I/O口(該I/O本身有串阻引出)輸出,同時將引出的38M時鐘通過飛線連接到R141中與SSRAM相連的焊盤。經過示波器測試,發(fā)現干擾消失,同時進行業(yè)務測試時發(fā)現上下行業(yè)務同時發(fā)包時,下行業(yè)務正常。 通過上面兩個實驗可以確認此故障確定是在FPGA內部上行SSRAM的數據線翻轉時帶來的地彈噪聲,干擾了下行了CLK_38M時鐘,導致該時鐘質量劣化而使得下行SSRAM讀寫出錯,最終導致下行業(yè)務丟包。

圖4 M單板原理圖截圖

三、原因分析

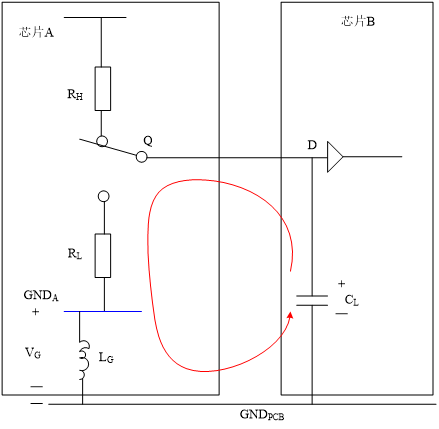

所謂“地彈”(ground bounce),是指芯片內部“地”電平相對于PCB板“地”電平的變化現象。以PCB板“地”為參考,就像是芯片內部的“地”電平不斷的跳動,因此形象的稱之為地彈。地彈是同步開關噪聲(Simultaneous Switching Noise,簡稱SSN)的一種,SSN是指當器件處于開關狀態(tài),產生瞬間變化的電流,在經過回流途徑上存在電感,形成交流壓降,從而引起噪聲。如果是由于封裝電感引起地平面的波動,造成芯片地和系統(tǒng)地不一致便是地彈。對于任何封裝的芯片,其引腳會存在電感電容等寄生參數。而地彈正是由于引腳上的電感引起的。我們可以用圖5來直觀的解釋下。圖中開關Q的不同位置代表了輸出的“0”和“1”兩種狀態(tài)。假定由于電路狀態(tài)轉換,開關Q接通RL的低電平,負載電容對地放電,隨著負載電容電壓下降,它積累的電荷流向地,在接地回路上形成一個大的電流浪涌。隨著放電電路建立然后衰減,這以電流變化作用于接地引腳的電感,這樣在芯片外的PCB板“地”GNDPCB與芯片內的地GNDA之間,會形成一定的電壓差,如圖中的VG。這種由于輸出電平轉換導致芯片內部參考地點位漂移就是地彈。SSN噪聲主要是伴隨著器件的同步開關輸出(SSO,即Simultancous Switch Output)而產生,開關速度越快,瞬間電流變化越顯著,電流回路上的電感越大,則產生的SSN越嚴重。此外考慮得更廣一點,除了信號本身回流路徑的電感之外,離的很近的信號互連線之間的串擾也是加劇SSN的原因之一。

圖5 地彈噪聲產生原理圖

而此故障確定是在FPGA芯片引腳有寄生電感。內部上行SSRAM的數據線翻轉時帶來了地彈噪聲,干擾了下行了CLK_38M時鐘,導致該時鐘質量劣化而使得下行SSRAM讀寫出錯,最終導致下行業(yè)務丟包。

四、解決與預防措施

了解了地彈噪聲的原理,就可以針對地彈產生的機制制定相應的措施。1)降低芯片內部驅動器的開關速率和同時開關的數目。2)為了減輕近距離信號互連線直接串擾,盡量減少被干擾信號周圍信號線的翻轉。3)增大芯片地平面面積。對于1)和2),考慮到SSRAM的讀寫帶寬有一定要求,讀寫的時鐘速率和數據線位寬不能隨意降低或減少。根據計算,做了如下調整:保持時鐘速率125M不變,將SSRAM的36根數據線減少到29根,減少的9根數據線為離CLK_38M最近的幾根。對于3),將CLK_38M所在的I/O bank中沒有使用的I/O管腳在邏輯內部都設置為輸出接地。通過改進,CLK_38M時鐘質量有所改善,回溝電平位置上升到2.3V左右。在常溫下只配置單路的雙向業(yè)務時,業(yè)務正常無丟包。但是當配置4路的雙向業(yè)務時,下行還是有少量丟包,高溫下丟包更加嚴重。配置4路業(yè)務和配置1路業(yè)務的區(qū)別是,配置4路業(yè)務時,由于數據包的增多,SSRAM的數據線翻轉更加頻繁,導致地彈噪聲更加嚴重,因此回溝也越深,如圖6所示。 圖6 配置4路雙向業(yè)務時CLK_38M波形

圖6 配置4路雙向業(yè)務時CLK_38M波形

通過查證,該FPGA芯片的抗噪能力這么差的原因是該芯片公司為了降成本,將芯片的封裝進行了簡化,芯片中原來4層的PCB簡化為2層,去掉了專有的電源層和地層,同時將金線變成了銅線。因此在現有的芯片和PCB硬件設計上已經沒有辦法再降低地彈噪聲了。正在無助的時候,思維轉了個方向。既然沒法降低地彈噪聲,那有沒有辦法降低地彈噪聲對時鐘信號的干擾呢?如圖6所示,芯片之所以會產生誤判是因為正好在時鐘的上升沿上偶爾會出現回溝,如果回溝的位置不在上升沿,而是在高電平或是低電平的位置,不就可以避免誤判了嗎?而回溝偶爾出現在CLK_38M時鐘的上升沿,原因是上行SSRAM的數據線都在CLK_125M時鐘的上升沿翻轉,而CLK_125M與CLK_38M時鐘不是同源的時鐘,會周期性的出現CLK_125M與CLK_38M同時翻轉的情況,也就是上行SSRAM的數據線在CLK_38M的上升沿處同時翻轉而產生翻轉噪聲。為了將翻轉噪聲移到CLK_38M的高電平處,邏輯做了改動。即上行SSRAM不再采用CLK_125M時鐘,而是將下行的38M時鐘進行3倍PLL倍頻后得到116M時鐘,然后將116M時鐘進行移相80°(經過示波器測量后得出的移向方案),由于116M時鐘38M是同源時鐘,因此相位關系是一定的,這樣可以保證116M時鐘和38M時鐘不同時翻轉。修改后CLK_38M時鐘波形如圖7所示,回溝移到了高電平處。

圖7 上行SSRAM時鐘改為116M并移相后的CLK_38M波形

同時為了改善CLK_38M時鐘上升沿變緩的問題,在硬件上將時鐘線的33歐姆串阻改為了0歐姆,且在邏輯內部將時鐘線進行了上拉。經過改進后,時鐘的上升時間明顯變短。

六、總結

經過以上改進后,CLK_38M時鐘質量有明顯改善,上升沿光滑,上升時間短。配置4路雙向業(yè)務,48小時長期常溫和高低溫情況下進行測試,業(yè)務正常,沒有再出現下行丟包的情況。通過M單板調試過程中出現的地彈噪聲干擾38M時鐘信號的故障及解決方法。總結出以下幾點:1)在FPGA硬件設計中,比較重要的信號,例如時鐘和復位線等,盡量不要和多根翻轉頻繁的信號線放置在同一個I/O bank。2)在FPGA硬件設計中,比較重要的信號,例如時鐘和復位線等,在其臨近的周圍I/O中不要安排翻轉比較頻繁的信號線,避免線間干擾。3)在FPGA邏輯設計中,沒有使用的I/O空余管腳最好設置為輸出接地,以增大地平面面積。4)如果地彈噪聲無法避免,可以通過避免其他大量信號線和重要信號線同時翻轉的方式,降低地彈對重要信號線的影響。5)對于地彈造成的重要信號線上升沿變緩的情況,可以通過加大被干擾信號的驅動電流,降低干擾信號的驅動電流的方法。同時將被干擾信號線在邏輯內部上拉。這些方法可以大大減小被干擾信號的上升時間,改善信號質量。

原文標題:地彈噪聲對信號完整性的影響

文章出處:【微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619224 -

示波器

+關注

關注

113文章

6718瀏覽量

189527 -

SSRAM

+關注

關注

0文章

5瀏覽量

8971

原文標題:地彈噪聲對信號完整性的影響

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

如何最大程度地降低地彈噪聲對單板信號完整性影響

【信號完整性】地彈噪聲對信號完整性的影響

如何最大程度地減少電源測量中的噪聲

電源擾動及地彈噪聲的產生機理

PCB互連設計過程中最大程度降低RF效應的基本方法

電源完整性與地彈噪聲的高速PCB仿真原理及設計

人聲效果的調音處理

如何降低地彈噪聲對單板信號完整性影響

如何最大程度地降低地彈噪聲對單板信號完整性影響?

評論