GIC 硬件原理

GIC,Generic Interrupt Controller。是ARM公司提供的一個通用的中斷控制器。主要作用為:接受硬件中斷信號,并經(jīng)過一定處理后,分發(fā)給對應的CPU進行處理。

當前GIC 有四個版本,GIC v1~v4, 本文主要介紹GIC v3控制器。

GIC v3中斷類別

GICv3定義了以下中斷類型:

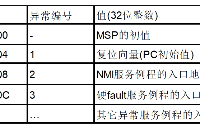

SGI(Software Generated Interrupt):軟件觸發(fā)的中斷。軟件可以通過寫 GICD_SGIR 寄存器來觸發(fā)一個中斷事件,一般用于核間通信,內(nèi)核中的 IPI:inter-processor interrupts 就是基于 SGI。

PPI(Private Peripheral Interrupt):私有外設中斷。這是每個核心私有的中斷。PPI會送達到指定的CPU上,應用場景有CPU本地時鐘。

SPI(Shared Peripheral Interrupt):公用的外部設備中斷,也定義為共享中斷。中斷產(chǎn)生后,可以分發(fā)到某一個CPU上。比如按鍵觸發(fā)一個中斷,手機觸摸屏觸發(fā)的中斷。

LPI(Locality-specific Peripheral Interrupt):LPI 是 GICv3 中的新特性,它們在很多方面與其他類型的中斷不同。LPI 始終是基于消息的中斷,它們的配置保存在表中而不是寄存器。比如 PCIe 的 MSI/MSI-x 中斷。

| 中斷類型 | 硬件中斷號 |

|---|---|

| SGI | 0-15 |

| PPI | 16-31 |

| SPI | 32-1019 |

| reserved | ...... |

| LPI | 8192-MAX |

GIC v3 組成

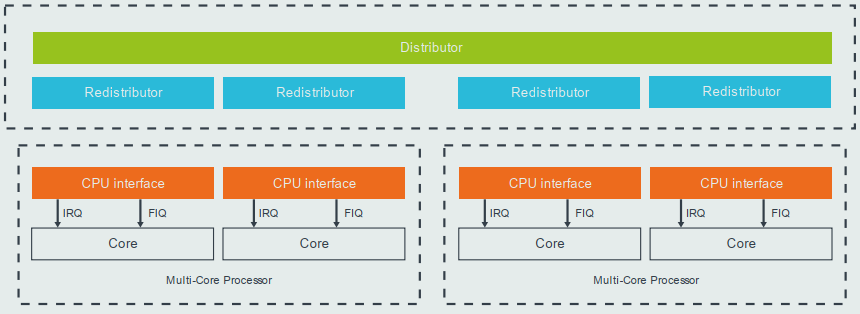

GICv3 控制器由以下三部分組成:

Distributor:SPI 中斷的管理,將中斷發(fā)送給 Redistributor

打開或關閉每個中斷。Distributor對中斷的控制分成兩個級別。一個是全局中斷的控制(GIC_DIST_CTRL)。一旦關閉了全局的中斷,那么任何的中斷源產(chǎn)生的中斷事件都不會被傳遞到 CPU interface。另外一個級別是對針對各個中斷源進行控制(GIC_DIST_ENABLE_CLEAR),關閉某一個中斷源會導致該中斷事件不會分發(fā)到 CPU interface,但不影響其他中斷源產(chǎn)生中斷事件的分發(fā)。

控制將當前優(yōu)先級最高的中斷事件分發(fā)到一個或者一組 CPU interface。當一個中斷事件分發(fā)到多個 CPU interface 的時候,GIC 的內(nèi)部邏輯應該保證只 assert 一個CPU。

優(yōu)先級控制。

interrupt屬性設定。設置每個外設中斷的觸發(fā)方式:電平觸發(fā)、邊緣觸發(fā);

interrupt group的設定。設置每個中斷的 Group,其中 Group0 用于安全中斷,支持 FIQ 和 IRQ,Group1 用于非安全中斷,只支持 IRQ;

Redistributor:SGI,PPI,LPI 中斷的管理,將中斷發(fā)送給 CPU interface

啟用和禁用 SGI 和 PPI。

設置 SGI 和 PPI 的優(yōu)先級。

將每個 PPI 設置為電平觸發(fā)或邊緣觸發(fā)。

將每個 SGI 和 PPI 分配給中斷組。

控制 SGI 和 PPI 的狀態(tài)。

內(nèi)存中數(shù)據(jù)結構的基址控制,支持 LPI 的相關中斷屬性和掛起狀態(tài)。

電源管理支持。

CPU interface:傳輸中斷給 Core

打開或關閉 CPU interface 向連接的 CPU assert 中斷事件。對于 ARM,CPU interface 和 CPU 之間的中斷信號線是 nIRQCPU 和 nFIQCPU。如果關閉了中斷,即便是 Distributor 分發(fā)了一個中斷事件到 CPU interface,也不會 assert 指定的 nIRQ 或者 nFIQ 通知 Core。

中斷的確認。Core 會向 CPU interface 應答中斷(應答當前優(yōu)先級最高的那個中斷),中斷一旦被應答,Distributor 就會把該中斷的狀態(tài)從 pending 修改成 active 或者 pending and active(這是和該中斷源的信號有關,例如如果是電平中斷并且保持了該 asserted 電平,那么就是 pending and active)。ack 了中斷之后,CPU interface 就會 deassert nIRQCPU 和 nFIQCPU 信號線。

中斷處理完畢的通知。當 interrupt handler 處理完了一個中斷的時候,會向?qū)?CPU interface 的寄存器通知 GIC CPU 已經(jīng)處理完該中斷。做這個動作一方面是通知 Distributor 將中斷狀態(tài)修改為 deactive,另外一方面,CPU interface 會 priority drop,從而允許其他的 pending 的中斷向 CPU 提交。

為 CPU 設置中斷優(yōu)先級掩碼。通過 priority mask,可以 mask 掉一些優(yōu)先級比較低的中斷,這些中斷不會通知到 CPU。

設置 CPU 的中斷搶占(preemption)策略。

在多個中斷事件同時到來的時候,選擇一個優(yōu)先級最高的通知 CPU。

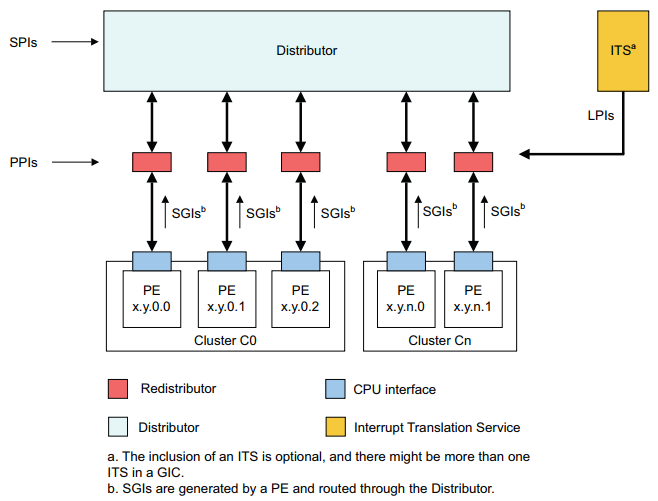

GICv3 控制器內(nèi)部模塊和各中斷類型的關系如下圖所示:

中斷路由

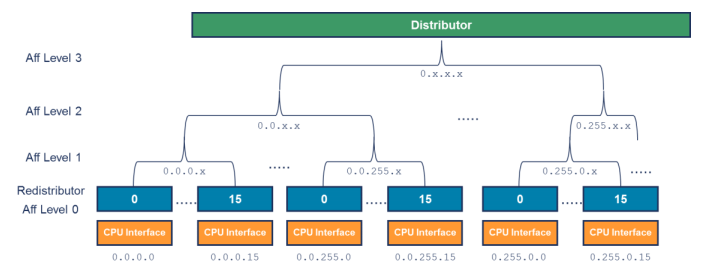

GICv3 使用 hierarchy 來標識一個具體的 core, 如下圖是一個四層的結構(aarch64):

用

各個 affinity 的定義是根據(jù) SOC 自己的定義,比如:

中斷親和性的設置的通用函數(shù)為 irq_set_affinity,后面會做詳細介紹。

中斷狀態(tài)機

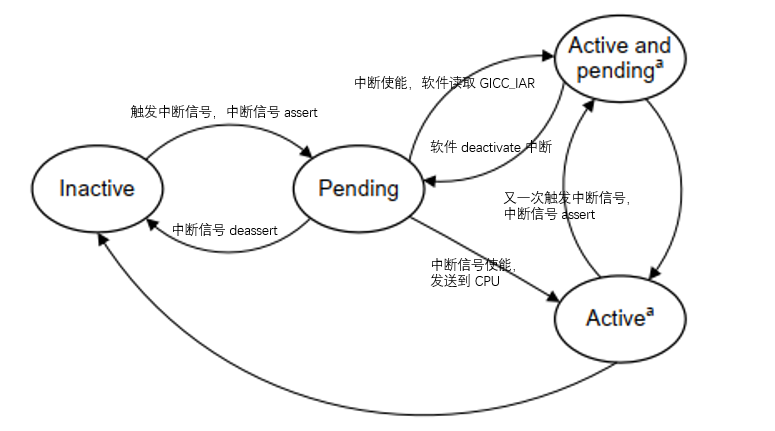

中斷處理的狀態(tài)機如下圖:

Inactive:無中斷狀態(tài),即沒有 Pending 也沒有 Active。

Pending:硬件或軟件觸發(fā)了中斷,該中斷事件已經(jīng)通過硬件信號通知到 GIC,等待 GIC 分配的那個 CPU 進行處理,在電平觸發(fā)模式下,產(chǎn)生中斷的同時保持 Pending 狀態(tài)。

Active:CPU 已經(jīng)應答(acknowledge)了該中斷請求,并且正在處理中。

Active and pending:當一個中斷源處于 Active 狀態(tài)的時候,同一中斷源又觸發(fā)了中斷,進入 pending 狀態(tài)。

中斷處理流程

https://dragonki先暫時略過.blog.這里的詳細net/article/de相關內(nèi)容在/1058后面詳細分

外設發(fā)起中斷,發(fā)送給 Distributor

Distributor 將該中斷,分發(fā)給合適的 Redistributor

Redistributor 將中斷信息,發(fā)送給 CPU interface

CPU interface 產(chǎn)生合適的中斷異常給處理器

處理器接收該異常,并且軟件處理該中斷

審核編輯:何安

-

ARM

+關注

關注

134文章

9340瀏覽量

376134 -

控制器

+關注

關注

114文章

17049瀏覽量

183539

原文標題:扒開 ARM 中斷控制器的底褲

文章出處:【微信號:LinuxDev,微信公眾號:Linux閱碼場】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

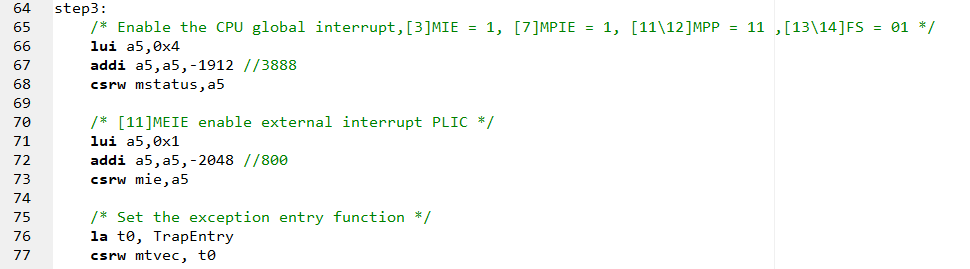

AS32X601驅(qū)動系列教程 PLIC_中斷應用詳解

串口中斷是內(nèi)部中斷還是外部中斷,串口中斷是怎么觸發(fā)的

電機控制器原理是什么?類型有哪些?

Arm Cortex-R82AE賦能高性能區(qū)域控制器設計

stm32怎樣觸發(fā)軟件中斷

【「ARM MCU嵌入式開發(fā) | 基于國產(chǎn)GD32F10x芯片」閱讀體驗】+閱讀中斷篇

【「ARM MCU嵌入式開發(fā) | 基于國產(chǎn)GD32F10x芯片」閱讀體驗】+書籍整體概況

ARMxy ARM工業(yè)控制器支持深度學習應用于物體檢測

電機控制器硬件的功能介紹

【GD32 MCU 入門教程】GD32 MCU 常見外設介紹(3)NVIC 介紹

評論