之前的理解

最近在做設(shè)計的時候,發(fā)現(xiàn)之前對DFF的理解有些模糊,直到有次在實踐中遇到了一些問題,含糊其詞的也不能解決問題,于是乎就把DFF理解透徹透徹,畢竟這可是時序電路的基本概念。

對于DFF,之前理解的,DFF在時鐘的上升沿進(jìn)行對D端的數(shù)據(jù)采集,再下一個時鐘的上升沿來臨,Q端輸出D端采集的數(shù)據(jù)。能這么理解,是離開書本時間太長了,又觀察到了ModelSim仿真波形的影響,這么理解只是在描述仿真波形的表征現(xiàn)象,并非根本的原理。比如,在Modelsim仿真中,若通過DFF將數(shù)據(jù)組進(jìn)行延時,用時鐘將寄存器進(jìn)行多個時鐘周期的同步,并帶有異步復(fù)位,對應(yīng)Verilog描述如下:

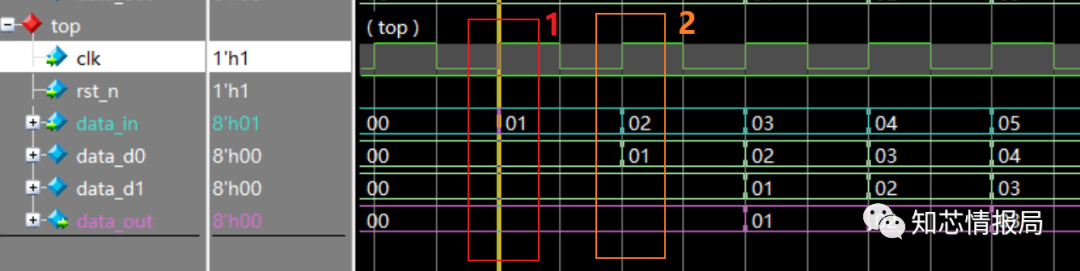

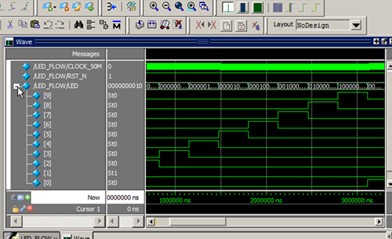

對應(yīng)仿真波形如下:reg [7:0] data_d0, data_d1, data_d2;always @ ( posedge clk or negedge rst_n ) beginif ( !rst_n ) begindata_d0 <= 8'b0;data_d1 <= 8'b0;end else begindata_d0 <= data_in;data_d1 <= data_d0;endend

此時,時鐘上升沿和數(shù)據(jù)的變化沿都是對齊的,就產(chǎn)生了不正確的理解:通過Modelsim的wave窗口查看仿真波形的時候,如果將光標(biāo)打到時鐘的上升沿時候(比如心在光標(biāo)在Event 1時刻),對應(yīng)的數(shù)據(jù)data_in應(yīng)該是從8‘h00->8‘h0’1,可是光標(biāo)處data_in的數(shù)值顯示為8’h01。這樣,我就理解成了在Even1時刻,時鐘的上升沿對data_in(值為8’h01)進(jìn)行捕獲(接入到寄存器data_d0的D端),在下一個時鐘的上升沿到來的時刻(Event2時刻),寄存器data_d0的Q端數(shù)據(jù)發(fā)生改變(值為8’h01)。上述理解完全是根據(jù)波形描述出來的,是不全面的,是非本源的,是錯誤的。

此時,時鐘上升沿和數(shù)據(jù)的變化沿都是對齊的,就產(chǎn)生了不正確的理解:通過Modelsim的wave窗口查看仿真波形的時候,如果將光標(biāo)打到時鐘的上升沿時候(比如心在光標(biāo)在Event 1時刻),對應(yīng)的數(shù)據(jù)data_in應(yīng)該是從8‘h00->8‘h0’1,可是光標(biāo)處data_in的數(shù)值顯示為8’h01。這樣,我就理解成了在Even1時刻,時鐘的上升沿對data_in(值為8’h01)進(jìn)行捕獲(接入到寄存器data_d0的D端),在下一個時鐘的上升沿到來的時刻(Event2時刻),寄存器data_d0的Q端數(shù)據(jù)發(fā)生改變(值為8’h01)。上述理解完全是根據(jù)波形描述出來的,是不全面的,是非本源的,是錯誤的。正確的理解

正確的理解應(yīng)該從DFF本身出發(fā),通過DFF的電路原理圖分析DFF的電路工作原理,了解時鐘上升沿之前和之內(nèi)部邏輯的如何變化,如何影響了從D端到Q端的數(shù)據(jù)輸出。

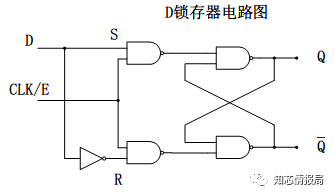

D鎖存器

在網(wǎng)上找到的很多電路圖講的都是D鎖存器,D鎖存器的電路為消除邏輯門控SR鎖存器不確定狀態(tài),在電路的S和R輸入端連接一個非門(Inverter),從而保證了S和R同時為0的條件,參考下圖由與非門構(gòu)成的D鎖存器電路圖:

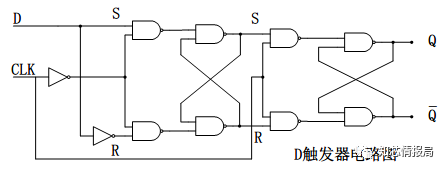

D觸發(fā)器

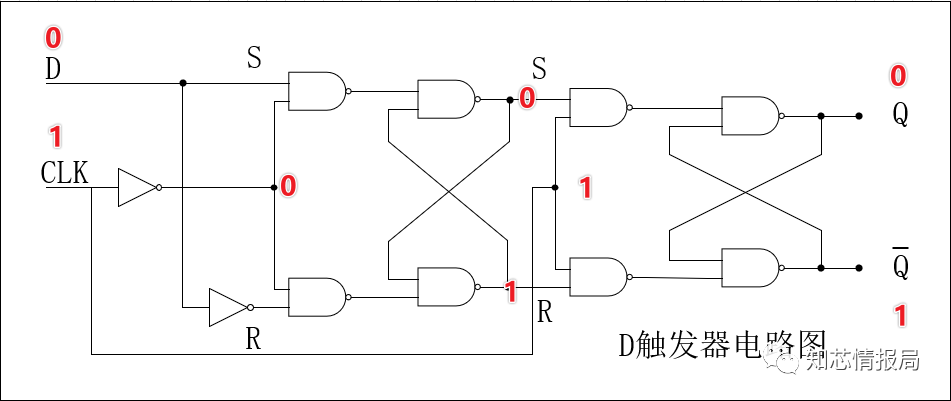

觸發(fā)和觸發(fā)器——時鐘脈沖邊沿作用下的狀態(tài)刷新稱為觸發(fā),具有這種特性的存儲單元電路稱為觸發(fā)器。D觸發(fā)器的電路圖如下(圖中的SR為了標(biāo)注有兩級SR鎖存器,方便邏輯推理):

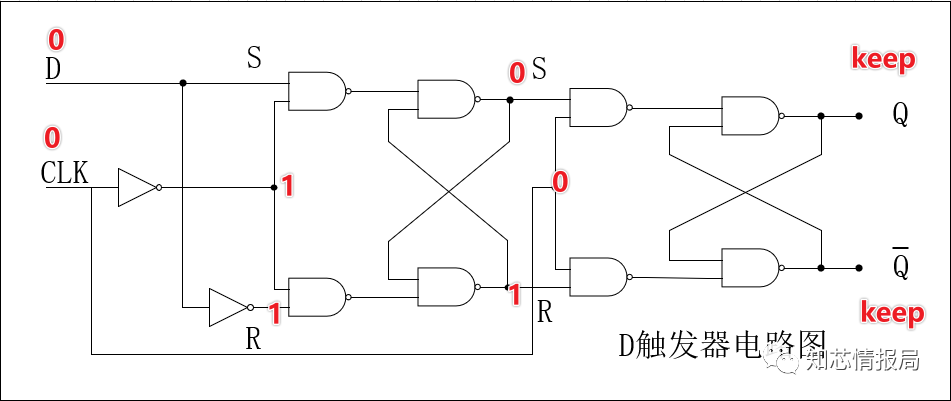

若繼續(xù)保持D端為0,CLK變?yōu)?時,第一級D鎖存器處于保持狀態(tài),第二級的SR鎖存器將上一次的D值傳遞到Q端輸出,詳情參考下圖:

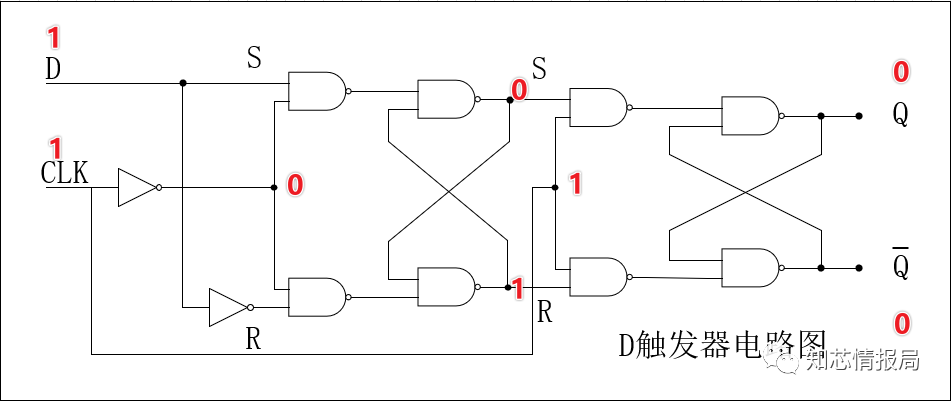

若在D端數(shù)值發(fā)生改變?yōu)?,且CLK仍然為1,第一級的D鎖存器仍處于保持狀態(tài),不會由于D端的變化而改變,更不會影響最后Q端的輸出。

若D端繼續(xù)保持為1,CLK轉(zhuǎn)換為0,此時第一級D鎖存器的輸出為D端的數(shù)據(jù),Q端輸出仍為保持狀態(tài)。

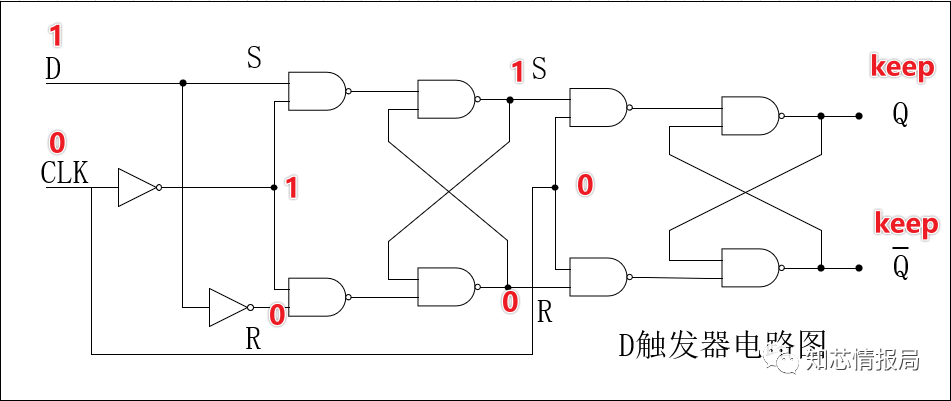

若D端數(shù)據(jù)繼續(xù)保持為1,CLK轉(zhuǎn)換為高,第一級D鎖存器的結(jié)果就會輸出到Q端,Q端的值也就隨著CLK的上升沿,捕獲到了1,并進(jìn)行輸出到Q端;

從邏輯圖中,也可以看出DFF的數(shù)據(jù)捕獲和輸出都需要滿足一定的時間約束。比如:

-

-

時鐘上升沿之前前后的數(shù)據(jù)要做夠穩(wěn)定,否則在時鐘跳變時刻,可能無法將其傳遞到Q端進(jìn)行輸出;

-

時鐘上升沿捕獲數(shù)據(jù)之后,到Q端輸出也需要一定的時間,穩(wěn)定之后才能用于下一級工作;

-

DFF捕獲時鐘上升沿的D端數(shù)據(jù),并在Q端輸出,一直維持到下一時鐘上升沿到來之前。在此期間,D端的數(shù)據(jù)變化不會直接影響到Q端的輸出。

ModelSim仿真

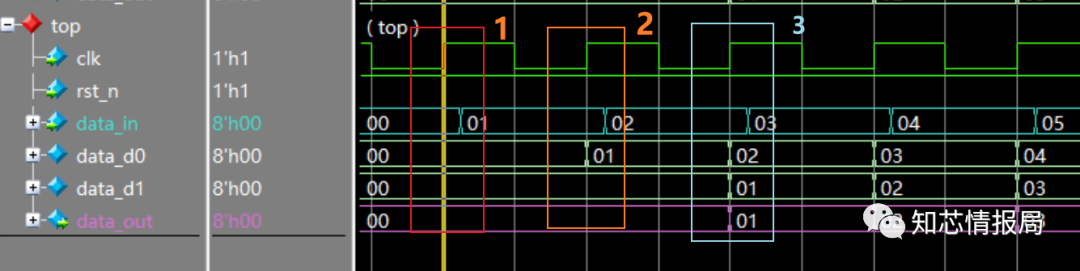

將tb文件中的data_in輸入做5個單位的傳輸延時,仿真結(jié)果見下圖:

????????可以看出,在時鐘的上升沿前后數(shù)據(jù)是不發(fā)生變化的,對于寄存器做延時的時序理解為:

????????可以看出,在時鐘的上升沿前后數(shù)據(jù)是不發(fā)生變化的,對于寄存器做延時的時序理解為:Event 1時刻:

-

-

在Event 1時刻,時鐘上升沿之前data_in(值為8’h00),data_d0的D端為data_in(值為8’h00);

-

在Event 1時刻,時鐘上升沿之后data_in(值為8’h00),data_d0的Q端為data_in(值為8’h00);所以在Event 1時刻,data_d0的Q端保持為8’h00不變;

-

-

- 在Event 2時刻,時鐘上升沿之后data_in(值為8’h01),data_d0的D端為data_in(值為8’h01);

- 在Event 2時刻,時鐘上升沿之后data_in(值為8’h01),data_d0的D端為data_in(值為8’h01);所以在Event 2時刻,data_d0的Q端從8’h00變?yōu)?’h01;

-

- 在Event 3時刻,時鐘上升沿之后data_in(值為8’h02),data_d0的D端為data_in(值為8’h02);

- 在Event 3時刻,時鐘上升沿之后data_in(值為8’h02),data_d0的D端為data_in(值為8’h02);所以在Even 3時刻,data_d0的Q端從8’h01變?yōu)?’h02;

總結(jié)

DFF捕獲時鐘上升沿的D端數(shù)據(jù),并在Q端輸出,一直維持到下一時鐘上升沿到來之前。在此期間,D端的數(shù)據(jù)變化不會直接影響到Q端的輸出。

審核編輯:湯梓紅-

時序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21696 -

ModelSim

+關(guān)注

關(guān)注

5文章

174瀏覽量

47164 -

D鎖存器

+關(guān)注

關(guān)注

0文章

13瀏覽量

3704 -

dff

+關(guān)注

關(guān)注

0文章

26瀏覽量

3417

原文標(biāo)題:時序電路之DFF再理解

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Altera ModelSim 6.5仿真入門教程

Modelsim的功能仿真和時序仿真

使用 ModelSim 進(jìn)行設(shè)計仿真詳解

modelsim仿真詳細(xì)過程(功能仿真與時序仿真)

仿真軟件ModelSim及其應(yīng)用,ModelSim的仿真流程

Modelsim仿真教程Modelsim的基礎(chǔ)入門基礎(chǔ)教程免費下載

基于ModelSim使用二聯(lián)合Quarus自動仿真教程

基于ModelSim使用四ModelSim手動仿真教程

如何夾帶modelsim的仿真波形白底黑線

ModelSim手動仿真教程

芯片設(shè)計之Modelsim仿真工具

modelsim自動化仿真實驗 利用腳本實現(xiàn)modelsim自動化仿真

Vivado調(diào)用Modelsim仿真

DFF的電路工作原理與ModelSim仿真

DFF的電路工作原理與ModelSim仿真

評論