摘 要: 作為5G大規模多輸入/多輸出( MIMO) 的技術支持,毫米波天線集成技術是實現高分辨數據流、移動分布式計算等應用場景的關鍵技術。討論了封裝天線( AiP) 、片上天線( AoC) 、混合集成等毫米波天線集成技術發展狀況、關鍵技術及其解決方案,剖析了幾種典型集成天線技術,分析了技術發展脈絡,總結了5G毫米波集成天線一體化技術的發展趨勢。

比如:針對生命體征監測和姿勢識別,IMEC開發了一款帶有片上天線的140GHz FMCW雷達收發器。雷達的工作范圍為0.15米至10米,分辨率為11毫米,射頻帶寬為13GHz,中心頻率為145GHz,收發器IC采用28nm模塊CMOS技術制造,可實現低成本的解決方案。

引 言

毫米波半導體是第五代移動通信技術( 5G ) 的基礎器件,采用毫米波頻率進行定向通信的技術是5G預期配置的關鍵技術之一。毫米波的頻率范圍為 30~300 GHz。目前研究的波段范圍有 28 GHz頻段、 38 GHz 頻段、 60 GHz 頻段和 E 頻段( 71 ~ 76 GHz、 81~86 GHz) 。5G 技術將通信頻段移向比第四代移動通信技術(4G) 高得多的毫米波頻率。5G 的頻譜帶寬較 4G 會有 10 倍至 20 倍的提升,最高數據傳輸速率可以提高 20 倍,且天線陣列和基站設備的尺寸更小、成本更低。在毫米波頻段中, 28 GHz 頻段、 60 GHz 頻段是最有希望應用于 5G 的兩個頻段。

作為收發 RF 信號的無源器件,天線決定了通信質量、信號功率、信號帶寬、連接速度等通信指標,是通信系統的核心。如何增加頻譜數據吞吐量是從 4G 到 5G 的重大挑戰。5G 的關鍵技術為大規模多輸入、多輸出( MIMO )的集成毫米波天線技術。每一個 MIMO 信道有著自身的從接收天線、發射天線到微處理器的信號通路。接收信道的作用是實現從天線接收RF 信號到輸入采樣基帶頻率的下變頻, 以及模數信號轉換等功能。發射信道的功能是將上變頻后的數字信號轉換為模擬 RF 信號。縮小尺寸是 5G 天線的一個重要挑戰。最小的基站天線尺寸將縮小到信用卡大小,這會增大毫米波天線及電路在集成度、低功耗和連接方面的要求。提升功率密度是 5G 天線的另一個重要挑戰。

多天線系統集成是應對 5G 系統 MIMO 、縮小尺寸、提升功率密度等挑戰的重點技術之一。由于 SiGe 和 CMOS RF 集成電路已經達到高的 fT、 fmax和高的集成密度,能采用 CMOS、 SOI 和 SiGe 工藝來設計大規模全集成硅毫米波相控陣電路。基于全 RF 結構、 8~32 元的發射( Tx ) 、接收( Rx ) 或收/發( T/ R) 模式已成功用于45~110 GHz頻段。硅集成方案可以在同一芯片上集成多個元件。與 GaAs 和 InP 等 Ⅲ-Ⅴ族半導體技術相比較,硅基技術具有更高的集成度和更低的成本。硅相控陣芯片在毫米波領域中應用廣泛。該項技術所面臨的挑戰是,在信號鏈單元上的RF 功率放大器、低噪聲接收機放大器、 A/D 轉換器或 D/A 轉換器都需要很大的效率提升。

無線通信和傳感器系統均可以通過 RF 系統提高集成度和采用新封裝技術的方法來提高性能。目前實現前端電路和集成天線的方案有三種。第一種為天線封裝( AiP ) 技術,天線采用 IC 封裝工藝制作。第二種為芯片上天線( AoC) 技術,天線直接在 硅襯底上制作。第三種為 AiP 和 AoC 的混合技術,天線饋電點制作在芯片上,輻射元件在片外實現。AiP 技術中,芯片和天線的互連在某個頻率范圍內應該達到信號傳輸的有效效率,其主要的封裝工藝有引線鍵合工藝和倒裝芯片工藝。但是,器件在高頻時的損耗較大,成本將升高。

1 相控陣接收機的結構

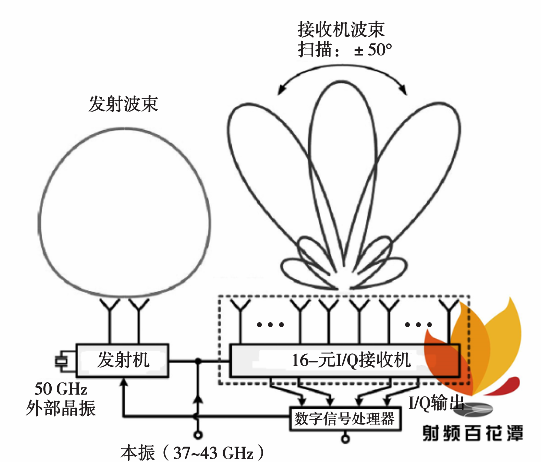

硅毫米波相控陣技術在 5G 通信中的應用范圍不斷擴大。多家公司采用 SiGe 和 CMOS 工藝來制作 IC,其工作頻率已達 60~100 GHz。例如,北美豐田研究所研制了一種具有 RF 波束形成能力的 SiGe 單芯片汽車相控陣接收機[1],如圖1 所示。

汽車相控陣接收機采用低成本的鍵合線技術進行封裝,并與 16 元線性微帶陣列連接。該天線在 77~ 81 GHz 頻率的指向性為 29. 3 dB,增益為 28 dB,每步( 1°) 在方位角平面中能掃描到±50°。該芯片中,平面相控陣天線陣列間距只有0.5λ( λ=3. 75 mm,頻率 80 GHz 以下) ,這個參數對于可用面積很小的毫米波電路尤其重要。這種相陣列需要盡可能多地在 SiGe 或者 CMOS 芯片上集成更多電路,不僅包括移相器和 VGA,而且包括全部的發射/接收電路、功率合成網絡、數字與 SPI 控制、偏置電路,某些情況下還包括完整的上/下轉換器。

圖 1 毫米波汽車相控陣接收機

2 天線集成技術

目前, 60 GHz 封裝的天線和片上天線均使用商用電磁仿真軟件進行設計。對于混合解決方案,已開發出補充標準 IC 設計工具的建模方法,以實現引線鍵合與 IC 的協調集成。AiP 技術需要確保整體性能的IC與天線間的寬帶低損耗互連設計。AoC 技術需要先進的后處理步驟或封裝工藝,以減少嚴重的介電損耗。混合天線集成技術則融合了 AiP 和 AoC 的優勢,可實現高輻射效率,無需芯片與封裝的低損耗互連設計。但是,該方案的設計靈活性不高,且在寬側方向上呈現輻射零點,阻止了其在某些場合的應用。

2. 1 AiP 技術2. 1. 1 結構

AiP 技術是將一元或多元天線集成到 RF 封裝內的關鍵技術,其典型方案是采用集成電路封裝工藝。在硅毫米波收發器中,封裝內集成了天線陣列,有助于提供足夠的信號增益,實現尺寸最小化。這種工藝是毫米波 RF 集成方案規模應用的關鍵技 術。例如,30 GHz 天線元的尺寸為毫米量級,在單個封裝內需要采用新類型的天線陣列集成技術。具有光束轉向功能的微小相控陣天線是毫米波無線電的關鍵器件[2]。為了在收發器封裝內集成天線陣列,需要考慮芯片組裝方案、陣列元和饋電網絡、芯片與封裝互連、封裝材料等。如果收發器采用多層封裝,需要在芯片與天線之間采用先進的互連技術,滿足天線饋電插入損耗最小的要求。芯片可以放置 在封裝正面,也可以放置在封裝底部。

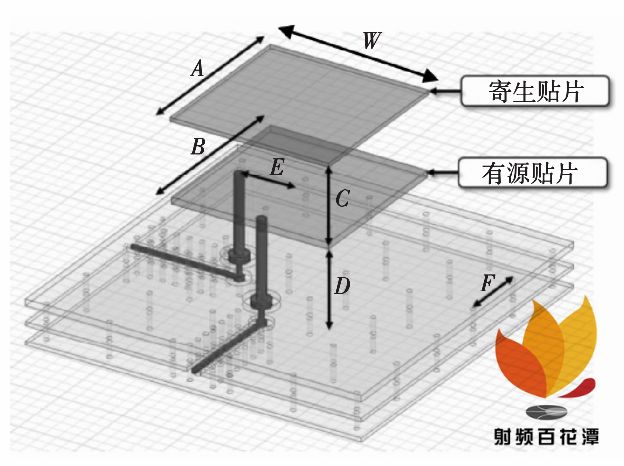

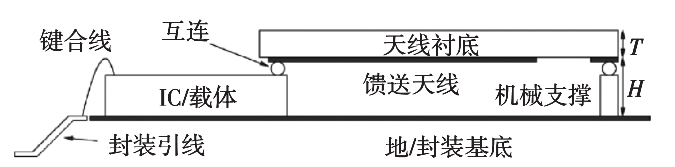

將芯片放置在封裝底部的方案對芯片接收和發射的影響最小。一種可用于 5G 無線通信的有機芯片封裝中的相控陣毫米波天線如 圖2 所示。為了提高天線帶寬、增益和輻射效率,在一個厚的覆板上放置了一個寄生平面結構,構成一個雙貼片天線疊層。為了達到優化 RF 設計和制造的目標,對封裝層疊片和低介電常數材料的參數作了優化選擇,如表 1 所示。

圖 2 有機芯片封裝中的相控陣毫米波天線

表 1 天線陣列設計要求

2. 1. 2 設計與制造

在 AiP 設計中,除了波束形成、信號放大和具有頻率轉換功能的相控陣 IC 外,具有極化特性的天線也是天線陣列的關鍵器件。在最早的硅基毫米波 IC 設計發展階段,天線設計采用襯底、形狀和成本與硅基毫米波 IC 兼容的技術[3]。目前,已有多種頻率的硅襯底片上毫米波天線,但由于面積較大、發射效率有限,在 100 GHz 以上的天線才有研究價值。在 60 GHz 頻率內,在液晶聚合物( LCP) 、有機高密度互連襯底、玻璃襯底、高/低溫共燒陶瓷襯底、硅襯底和模制物料基晶圓級襯底等材料上制作的硅相控陣天線陣列已被報道。通常需要對 AiP 陣列的增益、帶寬和輻射圖形進行優化。同時,需要考慮襯底材料、陣列尺寸(即元件和貼片的數量) 、互連靈活性(如連接電源和控制信號) 、熱性能與機械性能的相容性、 IC 組裝和板集成等因素。

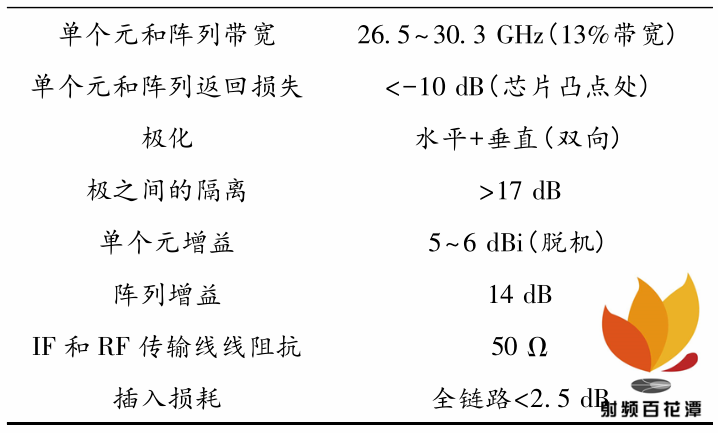

一種新的天線與 IC/載體結構如圖 3 所示[4]。天線結構通過 PCB 板制作于厚度為 T 的介質襯底上,并懸空倒置,翻轉在 IC/載體之上。IC 封裝基的地也作為天線的鏡像地,天線與地的間距為H。該結構中,天線與地板之間具有非常低的介電常數,天線結構之上有一層具有較高介電常數的覆板材料。在保持高天線效率的前提下,相比于標準 PCB 天線結構,這種堆疊結構具有更高的帶寬。一個帶有焊球的墊片可以放置在天線覆板的另一端,作為支撐。

圖 3 天線與 IC/載體結構

AiP 設計中通常采用集成電路封裝工藝進行封裝,需要將天線與片上電路進行物理連接。低溫共燒陶瓷( LTCC) 工藝可實現任意數量層的安裝結構, 具有跨層過孔、層間形成開放腔或密閉腔(IC 可集成于此) 等靈活性。采用該工藝封裝的毫米波天線越來越受到關注[5]。有些方案采用傳統的鍵合線、 倒裝芯片和 C4 焊接等工藝。例如, 60 GHz 硅相控陣芯片封裝需要有芯片與天線間低損耗分布網絡的多層毫米波襯底,必須是多層低損耗的 Teflon 基或 LTCC 基,成本昂貴。因此,典型的硅相控陣 AiP 可以達到 30 ~ 60 GHz 頻率[6],達到 80 GHz 的難度更大。

較之 LTCC 封裝方案,印刷電路板( PCB) 封裝方案可以降低成本。有采用 PCB 等較低成本高頻電路材料制成多層安裝結構的封裝方案,如RO3000系列和RO4000系列[7-8]的封裝。還有采用液晶聚合物作為基板的低成本方案。但由于使用盲孔或埋孔,層的數量增多,會導致 PCB 技術的機械制造成本升高。另外, PCB 工藝在極高頻段實現高密度化的難度增加,這將嚴重影響系統性能,導致效率降低。因此, LTCC 工藝是大多數多層結構陣列的選擇,采用該工藝方案的天線性能有改善。

2. 2 AoC 技術2. 2. 1 片上天線

片上天線是采用片上金屬化連線工藝集成制作的天線。在芯片上直接集成和組合天線的制作方法是太赫茲通信器件研究最少的領域之一。在當前技術條件下,由于襯底吸收和傳導電流等原因,消除 RF 電路與天線間所有的連接會使得設計成本大幅 降低,設計更加靈活。傳統觀念認為,由于沒有介電鏡( Dielectric Lenses) 補償結構,片上天線對于消費類的小功率器件并不是最佳結構。雖然典型片上天線的效率只能達到 10%,但如果能在片上設計并制造出亞毫米天線( 采用選頻性質的表面[9]或者 Yagi 高方向性的天線[10]) ,則會帶來成本大幅降低和設計靈活性大幅增加的優勢,這會超過使用效率更高、但昂貴且復雜的片下天線的優勢,從而增加了應用的可能性。

隨著載波頻率和帶寬移向亞太赫茲,高寬帶和高載波頻率使得金屬引線變得不穩定,片上天線被認為是替代印刷板上芯片金屬互連的方法之一。除了片上天線,片上波導和硅穿孔( TSV) 波導也是亞太赫茲頻段大帶寬應用中替代金屬連線的有前景的技術。片上天線的成功實現將會使得高集成度收發器、 60 GHz 空間電源組合和更高頻率毫米波系統等眾多應用受益。頻率從 0. 9 GHz[11]到 77 GHz[12]的多種頻率片上天線已有不少報道。德國高性能微電子研究所( IHP) 采用標準 SiGe BiCMOS 工藝,設計并制作了一種 130 GHz 的片上天線,峰值增益達到 8. 4 dBi。

2. 2. 2 CMOS 片上天線

CMOS 工藝是 RF IC 的一條重要發展途徑。隨著 CMOS 管特征頻率( fT) 接近 400 GHz[14], CMOS 工藝在毫米波 IC 中得到進一步應用。文獻[ 15]提 出了一種在 CMOS 芯片上集成人工磁導體和寬帶窄槽天線的新方法,采用標準 CMOS 工藝實現了 60 GHz 下 2 dBi 的增益和大于126%的阻抗帶寬。文獻[ 16]采用 0. 18 μm CMOS 工藝,制作了一種 60 GHz 的圓極化環形天線,具有覆蓋 57~67 GHz 的模擬和測量的軸向比( axial ratio, AR<3) 帶寬,增益達 4. 4 dBi。文獻[ 17]采用能制作阻抗帶寬為25 GHz ( 45~70 GHz) 的器件的 Si CMOS 工藝,制作了一種 60 GHz 寬帶的單極子天線,在 60 GHz 下實現了- 4. 96 dB 的增益。文獻[18]提出了一種高增益( 8 dBi 最大增益) 和高效率( 96. 7%峰值天線效率) 的片上天線,采用 CMOS 0. 18 μm 工藝制作,天線的- 10 dB 帶寬為 4 GHz。文獻[19]采用 0. 18 μm CMOS 工藝,制作了一種 60 GHz 帶寬的 CPW 饋電環形單極子天線。

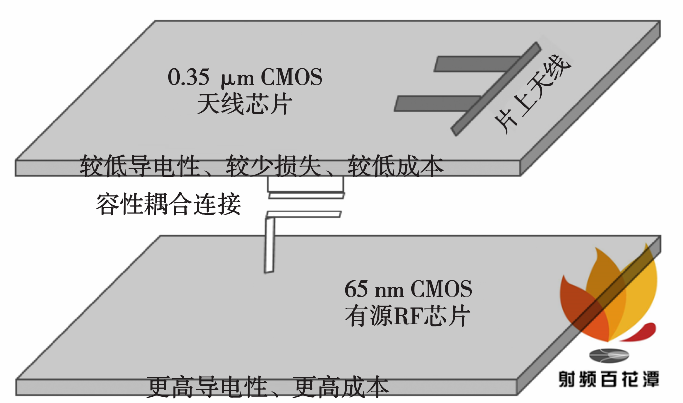

通常,制作在摻雜硅襯底上的片上天線只有約10%的低效率。但若采用成本較高的封裝天線,可實現比片上天線更高的效率。可采用容性耦合等先進連接技術,將成熟、低成本、較少摻雜的襯底上制作的天線芯片與有源 60 GHz 毫米波 RF 芯片連接起來,以實現比采用標準鍵合工藝的器件高得多的工作頻率范圍。天線可以用低成本的工藝( 如 0. 18 或 0. 35 μm) 和較低摻雜的襯底來制作,再通過容性耦合,連接到含60 GHz 功率放大器等有源元件上,而不采用更先進工藝[20]。一種通過容性耦合將天線芯片與有源 60 GHz RF 芯片連接的毫米波集成天線如圖 4 所示。該天線不僅具有舊工藝的低摻雜濃度、高電阻率所致的低電導性、低損失襯底,而且具有更高效率。制作天線陣列時,低速有源開關( 如二極管) 可以集成到芯片上,采用分相位無源饋線來執行元件調諧、移相和波速控制。

圖 4 通過容性耦合將天線芯片與有源 60 GHz RF 芯片 連接的毫米波集成天線

2. 3 混合集成毫米波天線

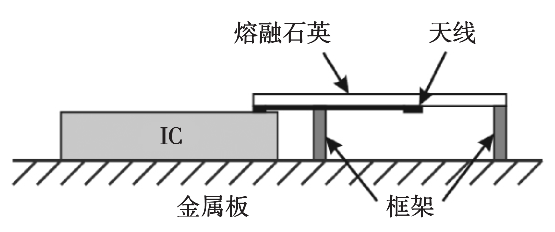

混合集成毫米波天線就是采用專用工藝,將天線與前端 IC 集成在同一封裝中。這種制作技術是純 AiP 和 AoC 的替代技術。混合集成天線的示意圖如圖 5所示[21]。熔融石英襯底上的偶極天線的 一半安裝在片上,另一半安裝在片下。這種結構的天線可以直接連接到片上電子器件。在 60 GHz 全頻段內,當增益為 6~8 dBi 時,芯片最大輻射效率可達 90%。

圖 5 混合集成天線概念示意圖

3 毫米波天線集成技術進展3. 1 學術界發展情況

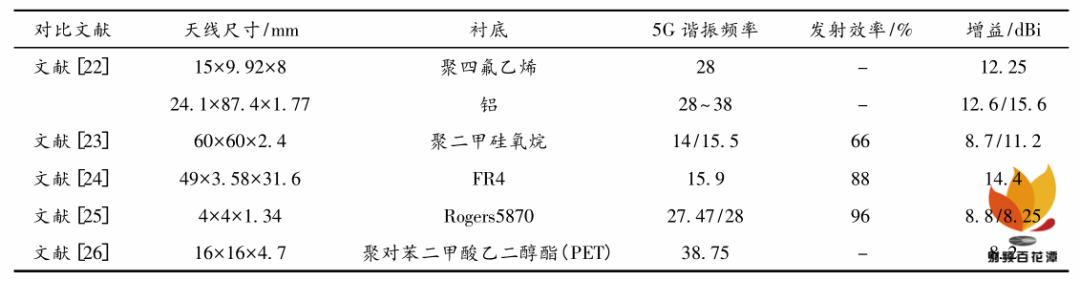

物聯網( IoT) 和 5G 要實現全面互聯的目標,就需要開發不同毫米波頻段的天線,并實現商業化量產。表2 總結了用于廣域 IoT 和 5G 無線通信的近期文獻中毫米波天線及其性能比較。可以看出,實用的解決方案仍然較少,多數方案仍然需要解決結構復雜、增益減少、效率低和功耗高等問題。

60 GHz 毫米波段器件將應用于5G 并量產化。片上系統或片上前端小型化系統集成的發展趨勢要求在不犧牲輻射效率、帶寬、增益的前提下,AoC器件、 AiP 器件的成本、尺寸和功耗必須向更小化方向發展。使用硅 IC 工藝提供了最大的集成度、低成本和低功耗,表明 GaAs 等Ⅲ-Ⅴ族化合物工藝并不一定是最佳選擇,尤其是考慮封裝、集成和互連問題時。

表 2 近期文獻中 5G 毫米波天線及其性能比較

天線元件通常制作于片下,也可以被完整地集成在單個芯片上。硅襯底由于介電常數高、電阻率低,片上集成天線的增益很小、輻射效率很低,可以通過提高襯底的電阻率來改善性能。例如制作高性能低成本的 SoC 時,將天線和 IC 集成到高電阻率絕緣層上硅( HR SOI) 上。在 AiP 方案中,為解決毫米波頻率下硅襯底上天線陣列的平面饋電器件插入損耗過大的問題,可采用將天線集成在附加基板上的混合集成創新技術,充分利用封裝和在這種有限空間內的耦合可能性。該方案顯現出較高的設計靈活性。

IBM 公司在過去的 14 年中發展了 RFIC 和 AiP 系列: 成像和通信應用的具有波束形成和波束掃描能力的性能驅動相控陣( 如 60 GHz、 94 GHz 和 28 GHz 相控陣) ,支持便攜裝置的 V-波段、W 波段和 Ka 波段毫米波模塊( 如 60 GHz 單元件、開關波束模 塊)[27]。

文獻[ 28]提出一種多層 LTCC 基板上構建的線性極化6 GHz 天線陣列。這些陣列使用4×4 微帶貼片輻射元件,分別由四分之一波長匹配的 T 型接頭網絡和 Wilkinson 功率分配器網絡饋電。測量結果表明,由前者饋電的陣列比由后者饋電的陣列表現更好。對于帶有和不帶有嵌入式腔的陣列,測量的阻抗帶寬分別為 9. 5%和 5. 8%,最大增益分別為 18. 2 dBi 和 15. 7 dBi。

文獻[ 29]報道了一種在熔融石英基板上構建的線性極化 60 GHz 天線陣列。該陣列使用由饋電網絡饋電的 2×4 微帶貼片輻射元件,饋電網絡使用了共面條帶和共面條波導。通過金屬腔增強的陣列實現了大于 9 GHz 的測量阻抗帶寬和約15 dBi 的最大增益。

文獻[ 30]提出一種采用 LTCC 工藝、具有 2×2 微帶貼片輻射元件的天線陣列,制作出具有線性極化的 60 GHz 發射器模塊。

文獻[ 31]分別使用 1×8 和 2×5 微帶貼片輻射元件,制作出兩個有源線性極化60 GHz 天線陣列。

文獻[ 32]提出了一種具有由波后波導網絡饋電的槽輻射元件、線性極化 60 GHz 的天線陣列。

文獻[ 33]提出了一種圓極化 60 GHz 的天線陣列,該陣列通過對原始天線元件、疊層波導、調整圓極化軸比進行精細設計,實現了寬帶寬。

文獻[ 34]提出了一種在 LCP 基板上制作的圓極化 60 GHz 天線陣列。該陣列采用了新的槽輻射元件和新穎的開腔反射器。測量結果表明, 2×4 輻射元件陣列的峰值增益為15. 6 dBic。

3. 2 商業化發展態勢

據 Gartner 預測,到 2021 年,市場將有 9% 的智能手機支持 5G 網絡。5G 采用波束成形技術,必須采用多天線陣列系統( Massive MIMO) 。這將導致天線呈量級增長,并推動天線向高度集成化、復雜化的方向發展,工藝技術不斷升級,新材料不斷應用。例如,新型材料液晶高分子聚合物( LCP) 材料具有低損耗、高靈活性、高密封性等優點,非常適用于制作微波、毫米波器件。蘋果公司推出的毫米波天線解決方案中包含采用 LCP 材料制作的天線,這是 5G 天線大規模商用化的一個重要方向[35]。高通公司 QTM052 毫米波天線模組系列支持緊湊封裝尺 寸,適合于移動終端集成。配置 QTM052 的毫米波天線模組的終端將于2019 年上半年推向市場,顯示出在 5G 中集成天線和 RF 前端等元器件的發展趨勢。意法半導體公司、 STATS ChipPAC 和英飛凌科技公司在英飛凌第一代嵌入式晶圓級球柵陣列 ( eWLB) 技術的基礎上,合作開發了下一代的 eWLB 半導體產品封裝技術。目前已開發出具有8 mm×8 mm 封裝的集成天線制作的四通道收發器。該天線采用 RDL 層中的金屬結構,并集成于封裝中,為在 5G 等毫米波領域應用的雷達系統封裝提供了解決方案[36]。近期,中芯長電公司發布了 SmartAiPTM 工藝平臺制作的世界首個超寬頻雙極化的 5G 毫米波天線芯片的晶圓級集成封裝,具有集成度高、散熱性好、工藝簡練的特點,能夠實現 24~43 GHz 的超寬頻信號收發,達到 12. 5 dB 的超高天線增益。

4 結束語

在未來的較長時間里, 5G 架構將繼續在網絡、 無線訪問和物理層不斷發展,需要在 RF/ 毫米波集成電路、毫米波天線陣列技術等方面擁有多種創新型產品組合,從而推動 5G 無線電和產業化發展。例如, 5G 中功率放大器、天線、濾波器和匹配電路的數量可以高達 64 個或更多。這些組件在效率和集成度方面的提升對無線電的總體能效和性能十分重要。具有大量天線、頻率為27 GHz 及以上的高集成度 MIMO 無線電是 5G 系統的關鍵技術。上述三種集成方案可用于毫米波天線設計。以 60 GHz 頻段為例, AoC 器件的輻射效率和增益指標落后于 AiP 器件和混合方案。AiP 器件和混合器件實現了最佳輻射效率,因此可以認為選用 AiP 技術比選用 AoC 技術更合適。AiP 技術具有設計靈活性和印刷天線結構的優勢,但對于復雜的多層封裝結構,可能不具備與 AoC 技術和混合方案同等成本競爭的條件。此外, AiP 方案芯片到芯片的互連會導致熱損失、延遲和設計量增加。混合方案似乎是最好的方案。但是,當頻率超過 60 GHz 時,典型的混合技術、 AiP 都是不夠成熟的方案。而 AoC 方案會更加完善,且已在 THz 波段進行了測試。據預期,AoC 方案在高頻具有更大發展空間。

天線集成的一個根本解決方案是將一個相控陣所需的所有東西集成到一個芯片上,這是硅基毫米波天線系統的優勢所在。不僅集成電子器件,而且集成通向晶圓級實現的高效率天線。晶圓級相控陣就可放置在輸入/輸出數據信號高達 Gbit/s、布置有控制器件和電源器件的低成本印刷電路板上。整個毫米波功能均集成于同一芯片上,這種晶圓規模的實現是一個完全自包含的解決方案。

原文標題:毫米波天線集成技術研究進展

文章出處:【微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

-

收發器

+關注

關注

10文章

3435瀏覽量

106048 -

封裝

+關注

關注

126文章

7934瀏覽量

143056 -

軟件

+關注

關注

69文章

4958瀏覽量

87626 -

5G毫米波

+關注

關注

3文章

110瀏覽量

23042

原文標題:毫米波天線集成技術研究進展

文章出處:【微信號:ZGDZGCS,微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

樂華工業電腦一體機的發展趨勢是什么?

乘用車一體化電池的發展現狀和未來趨勢

5G毫米波集成天線一體化技術的發展趨勢

5G毫米波集成天線一體化技術的發展趨勢

評論