日前,知名機構Techinsighs發(fā)布了一個關于存儲器未來路線圖的白皮書。他們在其中指出,三星、美光和 SK Hynix等主要 DRAM 廠商已經(jīng)將 DRAM 單元縮小到低于 15nm 的設計規(guī)則 (D/R) 生產(chǎn)。而現(xiàn)在他們一直在開發(fā)n+1 和 n+2 代,即所謂的 D1b(或 1β)和 D1c(或1γ)。

這意味著,無論是否采用 EUV光刻機用于 DRAM 單元圖案化,DRAM 單元 D/R 可能能夠進一步縮小到 12 納米以下或更高。

眾所周知,由于工藝完整性、成本、單元泄漏、電容、刷新管理和傳感裕度方面的挑戰(zhàn),單元縮放正在放緩。從先進的DRAM單元設計中可以看到一些創(chuàng)新技術,例如高k介電材料、柱狀(或準柱狀或單面)電容器工藝、凹槽通道S/A晶體管和HKMG采用。

此外,3D DRAM、高帶寬內(nèi)存 (HBM3)、圖形 DRAM (GDDR6X/7) 和嵌入式 DRAM(10nm、7nm 及以上)技術將延長 DRAM 的使用壽命和應用。

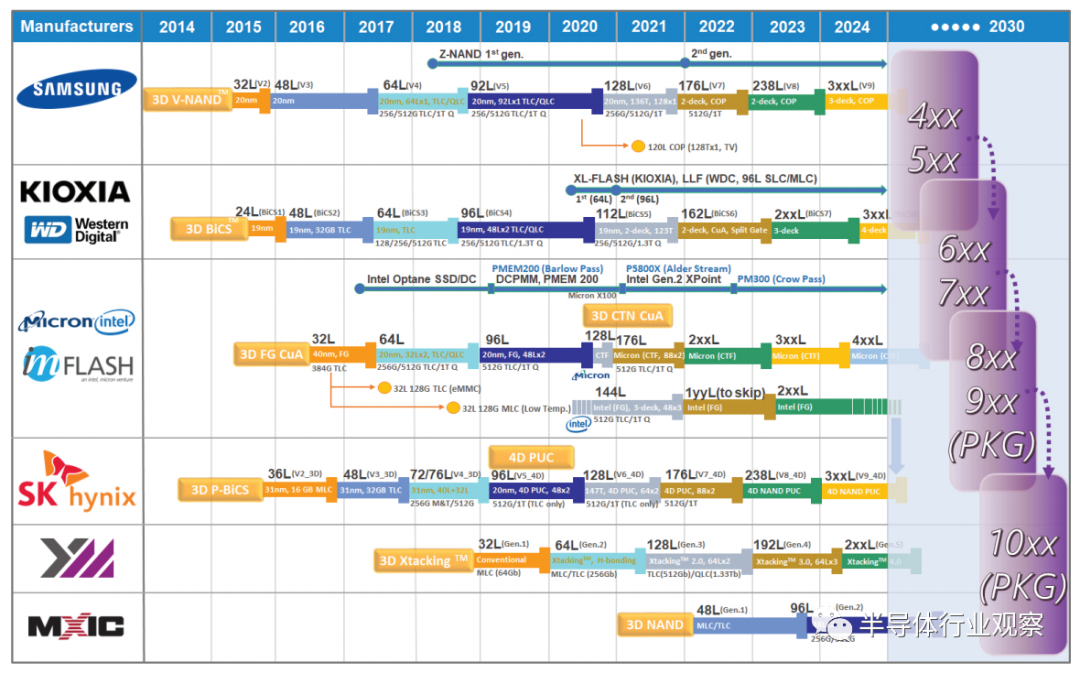

而主要的 NAND 制造商正在競相增加垂直 3D NAND 門的數(shù)量,并推出了 1yyL 3D NAND 設備。例如,三星 V7 V-NAND、鎧俠和西部數(shù)據(jù)公司 (WDC) BiCS6、美光第 2 代 CTF CuA 和 SK 海力士第 2 和第 3 代 4D PUC NAND 。

除了存儲密度之外,3D NAND 原型還用于超低延遲的三星Z-SSD、鎧俠XL-FLASH等NAND應用(歸類為存儲類內(nèi)存)。3D NAND 位密度已達到 10.8Gb/mm2(SK Hynix 176L 512Gb TLC)和 12.8Gb/mm2(Intel 144L 3-deck QLC)。同時,YMTC 128L Xtacking TLC和QLC產(chǎn)品已經(jīng)發(fā)布。

英特爾則擴展了 XPoint 內(nèi)存應用,不僅適用于傳統(tǒng) SSD,還適用于 DCPMM 持久內(nèi)存。Intel OptaneTM P5800X SSD 產(chǎn)品采用第二代 XPoint 內(nèi)存技術,具有四棧 PCM/OTS 單元結構。Everspin 第 3 代獨立 256 Mb STT-MRAM (pMTJ) 和 1Gb STT-MRAM,三星和索尼的新 28nm eSTT MRAM (pMTJ),具有 40nm 節(jié)點的 Avalanche eSTT MRAM (pMTJ),Dialog Semiconductor(舊 Adesto Technologies)第 2 代 CBRAM,而富士通 45nm ReRAM 130nm FeRAM 產(chǎn)品已于 2020 年和 2021 年上市 。

下面,我們來看一下Techinsights對存儲器未來的發(fā)展分析。

DRAM 技術,趨勢和挑戰(zhàn)

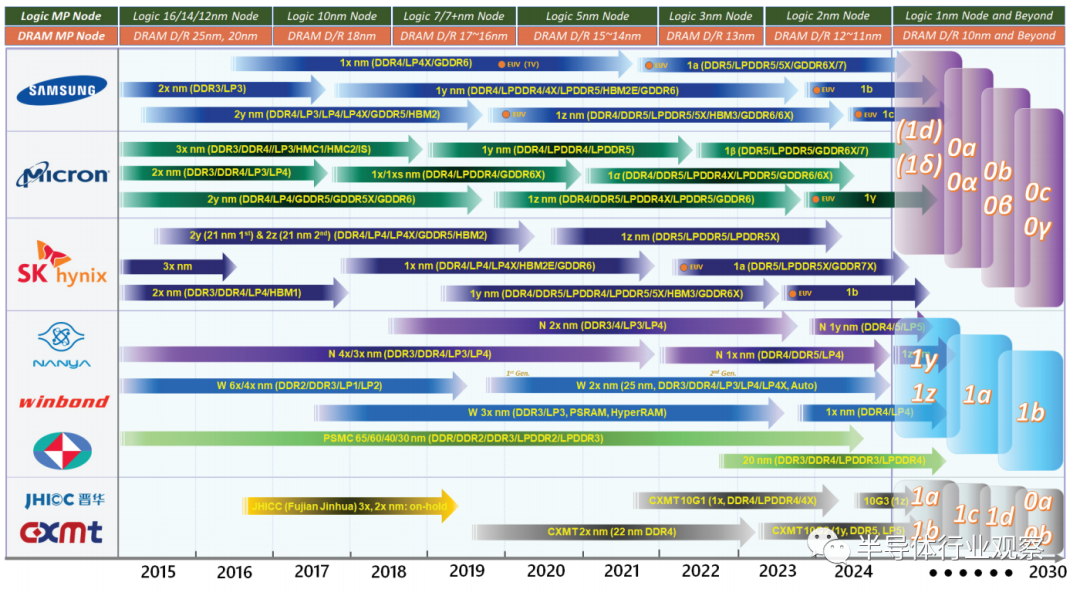

圖 1 顯示了來自三星, 美光, SK海力士,Nanya, PSMC, and CXMT廠商的 DRAM 路線圖。三星、美光和 SK海力士三大廠商已經(jīng)展示了適用于 DDR4、DDR5 和 LPDDR5 應用的具有 15nm 和 14nm 級單元設計規(guī)則 (D/R) 的 D1z 和 D1a 產(chǎn)品。三星已在 D1x DDR4 試用車(TV) 產(chǎn)品和 D1z LPDDR量產(chǎn)產(chǎn)品中采用 EUV 光刻技術,而美光和 SK 海力士則為 D1z 代保留了基于 ArF-i 的雙圖案化技術 (DPT) 工藝。到 2030 年,將生產(chǎn)出D1d(或 1δ)、D0a(或 0α)和 D0b(或 0β)等設計進一步縮小的幾代 DRAM。另一家來自中國的 DRAM 制造商長鑫存儲也加入了競爭,今年正在開發(fā)D1y 代。

圖 1.由TechInsights 提供的 DRAM 路線圖,顯示 2020 年至 2022 年市場上商業(yè)化的 D1z 和 D1a DRAM 產(chǎn)品。到 2030 年,將生產(chǎn)出D1d(或 1δ)、D0a(或 0α)和 D0b(或 0β)等幾代產(chǎn)品。

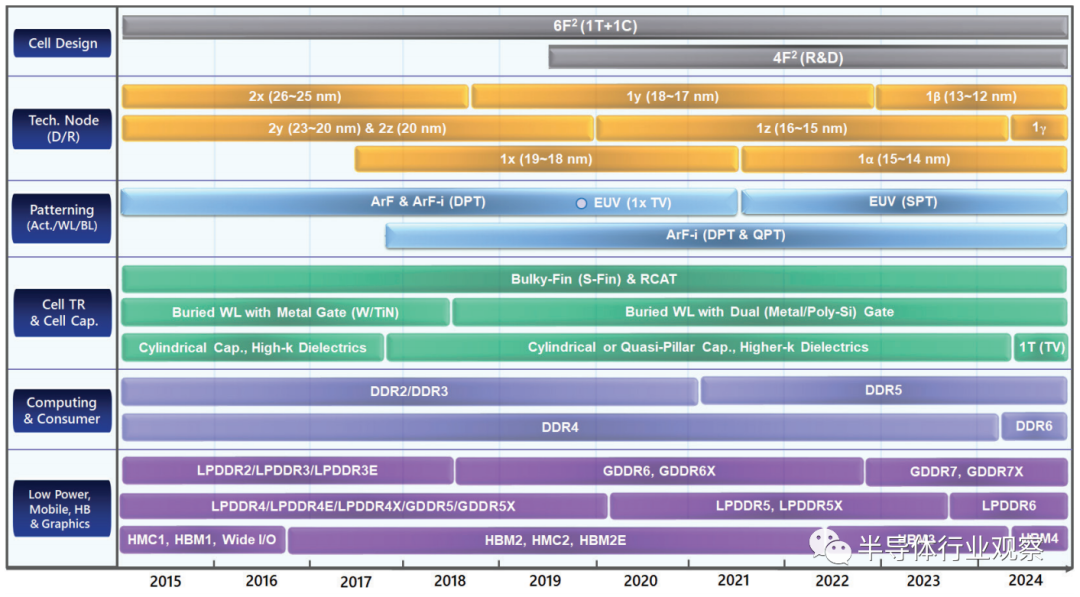

圖 2. DRAM 設備的技術/應用路線圖顯示 6F2 1T+1C 單元設計擴展到更多下一代 DRAM,盡管 DRAM 廠商一直在開發(fā) 4F2 單元結構,例如 1T DRAM 或無電容器 DRAM 原型。

到目前為止,已經(jīng)有了 8F2 和 6F2 DRAM 單元設計,其中單元包括 1T(晶體管)和 1C(電容器)。這種 1T+1C 單元設計將用于未來幾代 DRAM 的 DRAM 單元設計。然而,由于工藝和布局的限制,DRAM 廠商一直在開發(fā) 4F2 單元結構,例如 1T DRAM 或無電容器 DRAM 原型,作為擴展 DRAM 技術的下一個候選者之一(圖 2)。具有 B-RCAT 結構的大塊鰭(或鞍鰭)用于單元存取晶體管,然而,掩埋字線柵極材料已經(jīng)從單鎢層變?yōu)槎嗑Ч?鎢雙功函數(shù)層,以有效控制柵極泄漏。在這種情況下,具有較低功函數(shù)的多晶硅上柵極提高了 GIDL 電場 (30%) ,增大了擴散電阻。此外,美光使用純 TiN 柵極進行 D1z 和 D1α 代單元集成。雖然圓柱型結構是DRAM單元電容器集成的主流,但SK海力士(D1y和D1z)和三星(D1z)采用了準柱狀電容器(或單面柱狀電容器)結構,其中單元電容器僅外表面呈圓柱狀,這導致單元電容比上一代更小。幾年后,DDR5、GDDR7、LPDDR6 和 HBM3 產(chǎn)品將在市場上普及。

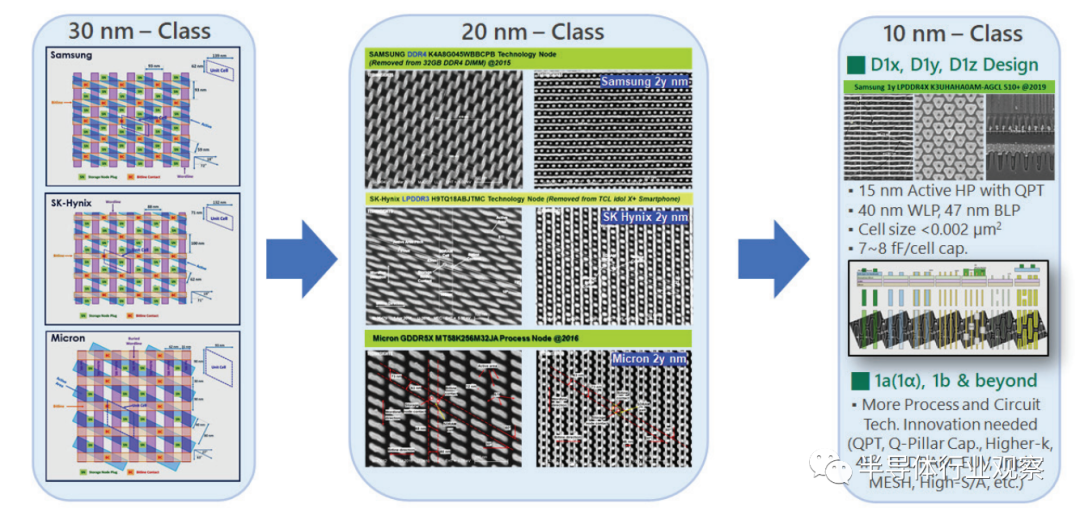

對于 10nm 級及以上的 DRAM 單元設計,應在其中加入更多創(chuàng)新的工藝、材料和電路技術,包括更高 NA EUV、4F2、1T DRAM、柱狀電容器、超薄 high-k 電容器介質和低 -k ILD/IMD 材料(圖 3)。

圖 3. 從 30nm 級到 10nm 級的 DRAM 單元設計和技術趨勢。需要更多創(chuàng)新技術來滿足單元電容、尺寸縮小和提升速度的要求。

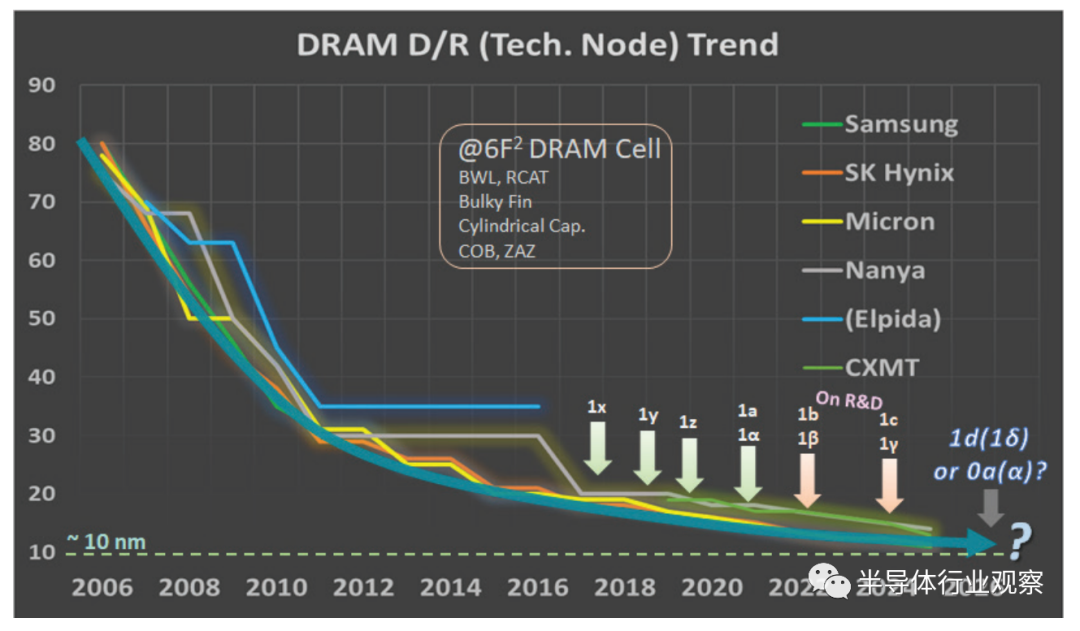

圖 4 顯示了主要廠商的 DRAM 設計規(guī)則 (D/R) 趨勢。如果他們保持 6F2 DRAM 單元設計以及1T+1C 結構,2027 年或 2028 年 10nm D/R 將是DRAM 的最后一個節(jié)點。DRAM 單元微縮將面臨若干挑戰(zhàn),例如 3D DRAM、減少row hammer(電路)、低功耗設計、刷新降低和管理刷新時間、低延遲、新功函數(shù)材料、HKMG 晶體管和片上 ECC。最受歡迎的功能將是“速度”和“感應裕量(sensing margin)”。三星用于 DDR5 和 GDDR6 的 HKMG 外圍晶體管技術就是增加 BL 感應裕量和速度的一個例子。

圖 4. DRAM D/R 趨勢顯示 6F2 單元設計的局限性。2027 年或 2028 年,10nm D/R 將是 6F2 DRAM 的最后一個節(jié)點。

3D NAND 技術、趨勢和挑戰(zhàn)

主要的 NAND 芯片制造商正在競相增加垂直 3D NAND 門的數(shù)量。他們已經(jīng)推出了最新的 1yyL 3D NAND 設備。三星176L(V7)、鎧俠/西部數(shù)據(jù) 162L(BiCS6)、美光176L(2nd CTF)、SK海力士176L(V7)用于1yyL產(chǎn)品,2021年和2022年長江存儲128L Xtacking TLC和QLC產(chǎn)品已經(jīng)上市(圖 5)。MXIC 還宣布了他們的第一個 48L 3D NAND 原型,將于 2022 年底或 2023 年初量產(chǎn)。

圖 5. TechInsights 的 3D NAND 路線圖顯示了 2021 年和 2022 年上市的 112L/128L 和 162L/176L 產(chǎn)品。用于 SCM 或fast-NAND 應用的Z-NAND、XL-FLASH 和 XPoint 已添加到路線圖中。

目前已經(jīng)采用了一些創(chuàng)新的技術和設計,例如三層結構、CuA/COP/PUC技術和具有H-bonding的Xtacking裸片。此外,具有3D NAND單元架構和多平面芯片設計的三星Z-NAND和鎧俠XL-FLASH等低延遲(高速)NAND產(chǎn)品已成功商業(yè)化。對于 500 層以上的 NAND 產(chǎn)品,我們不僅要考慮多堆棧或裸片堆棧集成,還要考慮 3D 封裝解決方案。

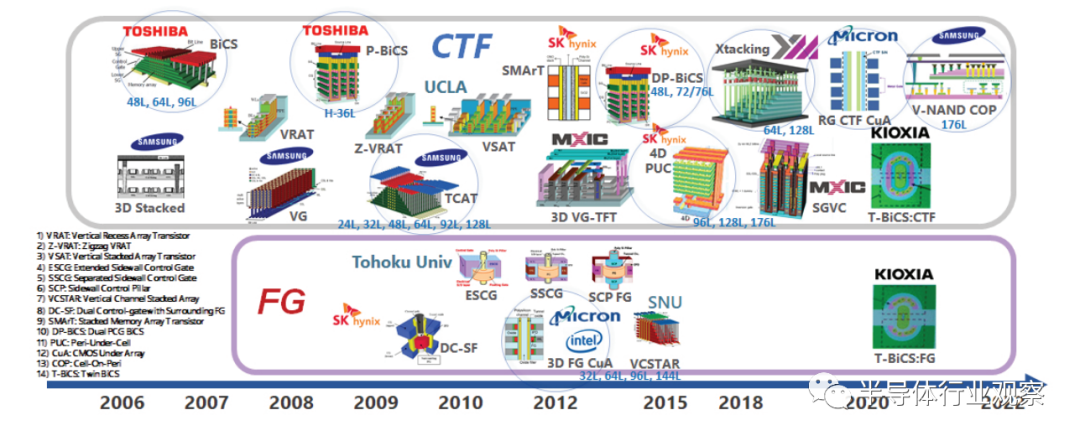

自 2018 年以來,全球大多數(shù)智能手機都使用 3D NAND 存儲組件而非 2D NAND 芯片。迄今為止,已經(jīng)提出并生產(chǎn)了七種不同的 3D NAND 原型:三星的 V-NAND、鎧俠(舊東芝存儲器)和西部數(shù)據(jù)的 BiCS、英特爾/美光的 FG CuA、美光的 CTF CuA(128L~)、P – SK海力士 的 BiCS (~72/76L)、SK海力士的 4D PUC (96L~) 和 長江存儲的 Xtacking(圖 6 和圖 7)。

圖 6. 七種不同的 3D NAND 原型已被提出并成功生產(chǎn):V-NAND、BiCS、FG CuA、CTF CuA、P-BiCS、4D PUC 和 Xtacking。

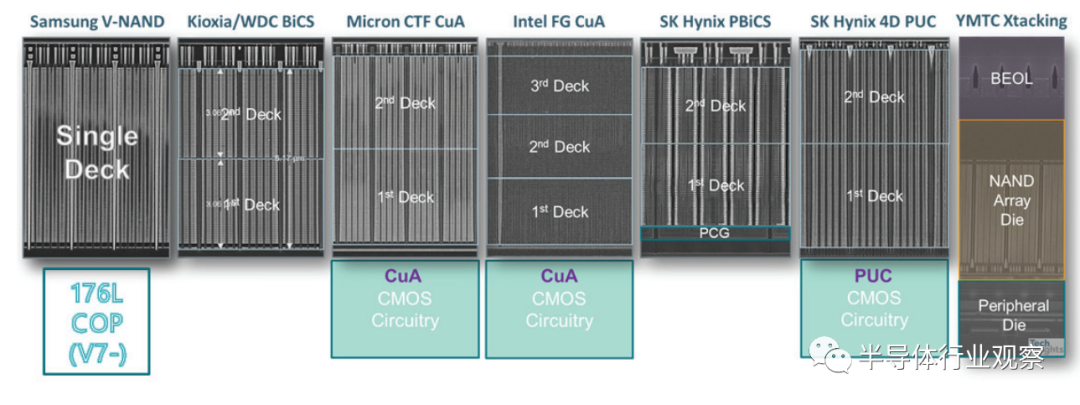

圖 7. 五個具有代表性的 SEM 圖像,顯示了每個 3D NAND 單元陣列架構的概念。CuA、PUC 和 Xtacking 原型在 NAND 單元陣列下具有 CMOS 外圍電路。

三星 V-NAND (TCAT) 3D NAND 產(chǎn)品專門應用了高達 128L (V6) 的單 VC 蝕刻工藝,而所有其他 3D NAND 產(chǎn)品均采用多層(例如 Intel 144L 為三層)串集成(string integration)。它們都使用 20nm 或 19nm BL 半間距,這意味著基于 ArF-i 和 DPT 的光刻是 3D NAND 的主要圖案化技術。

具有更高可靠性和低溫/高溫操作的特定應用仍然需要 2D NAND 晶圓和 SLC/MLC 操作,而不是 TLC 或 QLC 芯片。例如:MCU、醫(yī)療、機器人、電視/玩具、游戲控制器、可穿戴設備、安全攝像頭、智能音箱、IoT、AI、ML、打印機、機頂盒和航空航天都需要2D NAND產(chǎn)品。現(xiàn)在,3D NAND 產(chǎn)品在數(shù)據(jù)中心、云、服務器、SSD、PC、移動和智能手機中非常流行。

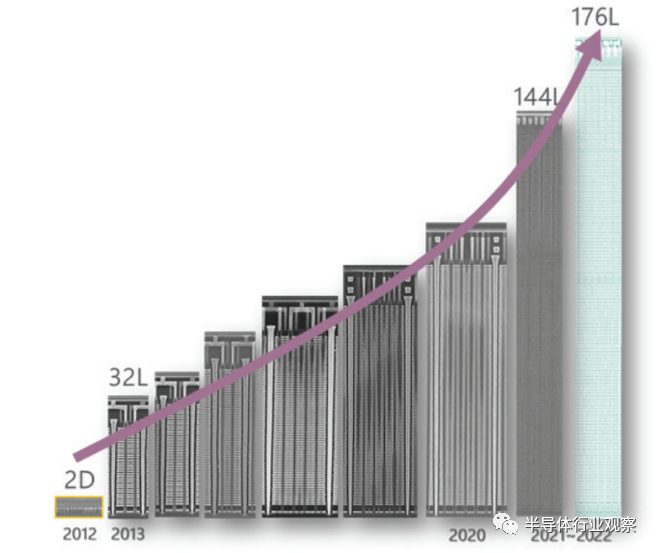

隨著堆疊柵極數(shù)量的增加,垂直 NAND 串的高度也會增加。例如,新發(fā)明的 176L 產(chǎn)品顯示距source plate 12μm 的高度(圖 8)。QLC 芯片的位成本持續(xù)下降,位密度增加到 15Gb/mm2。每個 NAND 串的門總數(shù)也增加到 200 個或更多。

圖 8. 3D 垂直 NAND 串高度的比較。新發(fā)明的 176L 產(chǎn)品距source plate的高度為 12μm。

英特爾 144 層 NAND 串第一次在源和位線之間由三層(上層、中層、下層,每層48L)組成,并為 TLC 和 QLC 器件保留了 FG CuA 結構。每個deck都可以分配給 QLC 或 SLC 塊的任意組合,以充分受益于英特爾在存儲系統(tǒng)中的新的block-by-deck概念。

我們還不能預測未來 3D NAND 技術的所有詳細挑戰(zhàn),但其中一些挑戰(zhàn)是 HAR、層應力控制、晶圓翹曲、工藝均勻性、嚴格控制 ALD/ALE、吞吐量、板對板錯位、良率控制、 缺陷、NAND 串電流、解碼器 TR 可靠性、PGM/ERS 速度、保留、電子遷移、泄漏和干擾、3D 封裝解決方案等。PLC 3D NAND 產(chǎn)品可能會在幾年內(nèi)推出。

新興內(nèi)存技術、趨勢和挑戰(zhàn)

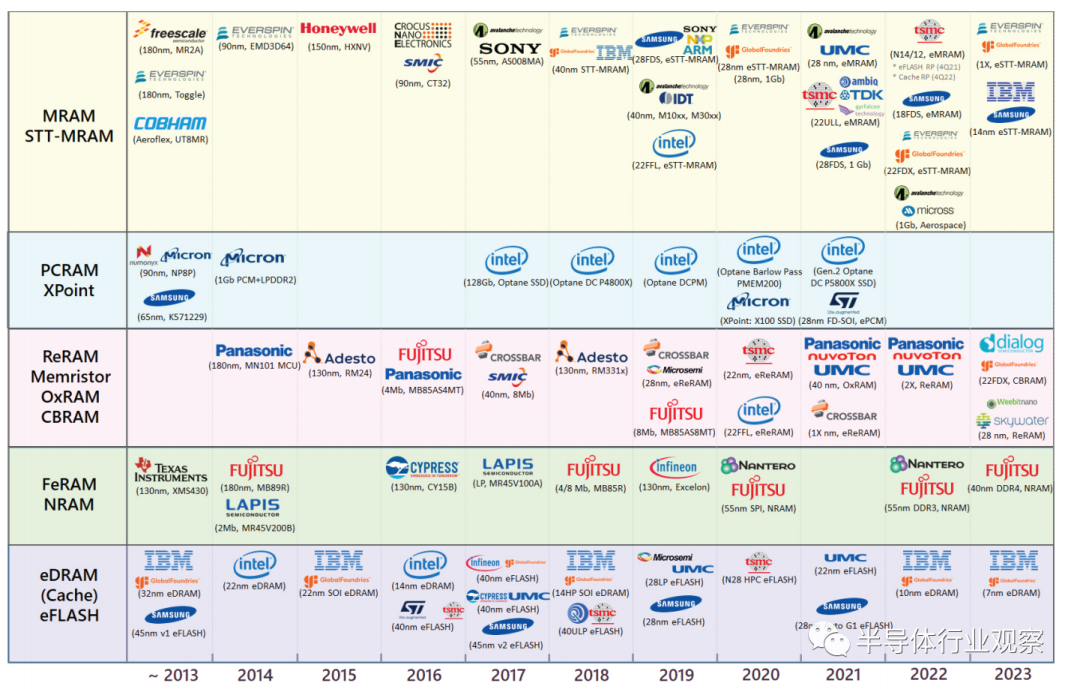

圖 9. TechInsights 的新興內(nèi)存路線圖,包括 STT-MRAM、PCRAM/XPoint、ReRAM/CBRAM、FeRAM 和嵌入式 DRAM/FLASH 內(nèi)存。

幾十年來,我們一直將 MRAM(或 STT-MRAM)、PCRAM、ReRAM 和 FeRAM 設備和技術視為新興內(nèi)存原型。但是,它們將是一種用于嵌入式應用的非易失性存儲設備,而不是分立的新興存儲設備。未來的新興存儲器設備,如 SOT MRAM、FTJ、單極或雙極絲狀 OxRAM、CBRAM、大分子存儲器、莫特存儲器或 DNA 存儲可能被稱為新興存儲器。在這里,我們?nèi)匀粚?MRAM、XPoint、ReRAM (CBRAM) 和 FeRAM視為新興存儲設備。他們正在擴展應用領域,例如 CPU/APU 高速緩存 (STT-MRAM)、AI 和內(nèi)存計算 (PCRAM)、模擬 IC (ReRAM、憶阻器)、外部開關 (FeRAM) 和高密度 SCM (XPoint Memory)。

在新興存儲器件中,STT-MRAM 技術已被主要廠商/開發(fā)商積極研究和開發(fā),例如 Everspin Technologies、GlobalFoundries、Avalanche Technologies、索尼、美光、IMEC、CEA-LETI、應用材料、三星、富士通、IBM、臺積電和自旋轉移技術 (STT)。英特爾、美光和 SK 海力士正專注于具有 PCM/OTS 單元結構的 XPoint 內(nèi)存。美光于 2021 年退出 XPoint 內(nèi)存(圖 9)。

迄今為止,我們已經(jīng)從市場上找到了Everspin 第三代獨立 256Mb STT-MRAM (pMTJ) 和 1Gb STT-MRAM、三星和索尼的 28nm eSTT MRAM (pMTJ)、具有 40nm 節(jié)點的 Avalanche eSTT MRAM (pMTJ) 和 Dialog Semiconductor(舊 Adesto Technologies)第二代 ReRAM (CBRAM )產(chǎn)品。臺積電宣布了 2nm eMRAM-F 產(chǎn)品路線圖,以取代用于數(shù)據(jù)/代碼存儲和配置存儲器應用的eFLASH。

迄今為止,Ambiq Apollo Blue MCU的所有代均使用臺積電制造的芯片。所有 Apollo Blue MCU 系列均獲臺積電支持,提供eFLASH 或 eMRAM 芯片。Apollo 1 至 Apollo 3 具有 2D NOR eFLASH ESF3 單元,分柵嵌入式 SuperFlash。它們由EG(擦除門)、CG(控制門)、FG(浮動門)和WL SG(選擇門)四個門組成。另一方面,Apollo4 在 M3 和 M4 之間有一個簡單的 eSTT-MRAM 單元結構。與 Apollo3 相比,外圍柵極和 eMemory 柵間距有所減小;外圍柵極由 170nm 降至 120nm,eMRAM 陣列由 230nm 降至 110nm。Ambiq 由臺積電制造的 22ULL 工藝的低功耗 Apollo4 MCU 可與 GreenWave 的 AI 處理器采用的 GlobalFoundries 的 eMRAM 22nm FDSOI 相媲美。臺積電 eMRAM 技術正在應用于 16nm FinFET 平臺。Everspin、三星和臺積電使用 HKMG 柵極工藝,僅Avalanche 除外。三星在采用 SOI 晶圓的 FDS 工藝方面是獨一無二的。Avalanche MRAM 柵極具有帶有 L 形隔離物的舊多晶硅柵極,而所有其他公司都使用高 k 柵極氧化物,例如 SiON 上的 HfO。特別是 Everspin 在 NMOS 高 k 柵極電介質中采用了 La。Everspin 和三星為 MRAM 柵極結構應用了先柵極 HKMG 工藝,而臺積電采用了后柵極 HKMG 工藝。

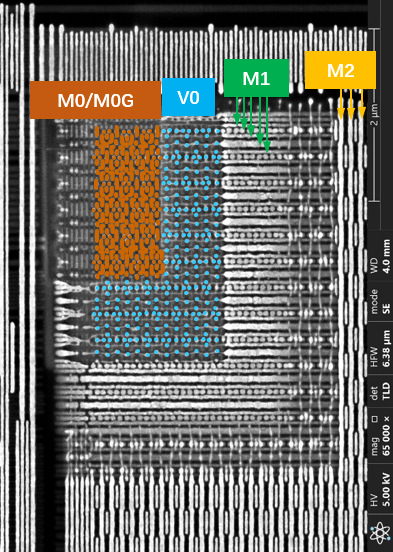

Everspin 在市場上發(fā)布了四種不同的 MRAM 產(chǎn)品,包括 Toggle-mode MRAM(第 1 代,Chandler fab.)和 STTMRAM(第 2~4 代,GF fab.)。在 STT-MRAM 產(chǎn)品中,第 2 代 STT-MRAM 器件采用基于 MgO 的面內(nèi) MTJ 結構,而第 3 代和第 4 代 STT-MRAM 器件采用垂直 MTJ (pMTJ) 技術。Avalanche pMTJ STT-MRAM 單元設計和結構顯示 40nm p-MTJ 層,單元尺寸為 0.032 μm2,MRAM 層位于 M1 源極線下方,位于 Contact-1 和 Contact-2 之間。例如,三星與索尼共同展示了用于華為 GT2 智能手表 GPS 控制器的 28nm pMTJ 8Mb 嵌入式 STT-MRAM 結構。它們是基于 MgO MTJ 的器件。

富士通 8Mb ReRAM 器件是迄今為止世界上密度最大的獨立量產(chǎn) ReRAM 產(chǎn)品。富士通采用了新的 45nm CMOS 工藝,與之前的 180nm 4Mb ReRAM 產(chǎn)品相比,芯片尺寸更小,存儲密度更高。

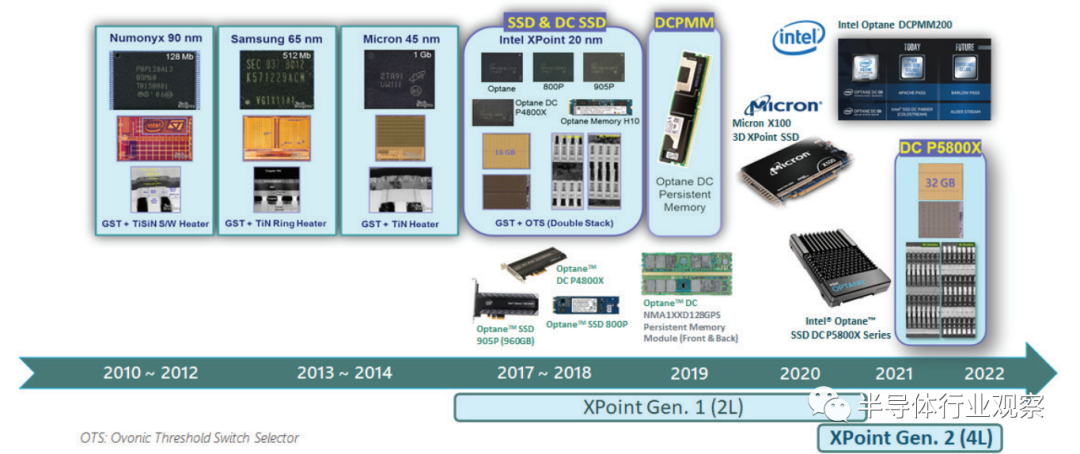

英特爾和美光的第一代 XPoint 內(nèi)存芯片具有 128Gb (16GB) 芯片密度和兩層的 PCM/OTS 結構。它已用于許多英特爾 SSD 產(chǎn)品,例如 Optane、800P、900P、DC P4800X、H10/H20 和 DCPMM。對于存儲元件,已經(jīng)提出和開發(fā)了許多候選者,例如相變材料、電阻氧化物單元、導電橋單元和MRAM單元。其中,第一代XPoint存儲器采用了硫屬相變材料,GST(Ge-Sb-Te)合金層。

一種用于 BL 和 WL 光刻/蝕刻工藝的 20nm 雙圖案技術 (DPT),實際上是2F2 單元被設計出。近日,英特爾發(fā)布了第二代 XPoint 內(nèi)存,例如市面上的傲騰 DC P5800X SSD 產(chǎn)品。

4 層 PCM/OTS 層結構,實際上是 1F2,集成在 M4 層上,形成 WL/BL/WL/BL/WL 多層。器件中雙向閾值開關選擇器 (OTS) 與PCM 層共同集成,該器件具有與之前的一代 XPoint 相同的元素(圖 10)。

圖 10. PCM/XPoint 歷史顯示 2L第一代和4L第二代英特爾的 XPoint 內(nèi)存產(chǎn)品。

新興的內(nèi)存設備可以取代 eFLASH 或 SCM,因為它們具有高性能(高速、耐用和記憶力)和能源效率。然而,最重要的挑戰(zhàn)之一將是降低比特成本,或者換句話說,如何增加陣列單元密度。到目前為止,沒有一個獨立的 STT-MRAM 裸片(256Mb 或 1Gb)和 XPoint 裸片(128Gb 或 256Gb)可與 3D NAND 裸片(QLC NAND 裸片為 1Tb 或 1.33Tb)相媲美。此外,大多數(shù)新興存儲器件使用一種或多種新材料,例如 HfO、HZO、GST 基硫族化合物和 Ir/Ta 基金屬電極,這在包括圖案形成/蝕刻、沉積和退火優(yōu)化在內(nèi)的工藝集成中造成了一些困難。

審核編輯 :李倩

-

存儲器

+關注

關注

38文章

7484瀏覽量

163778 -

晶體管

+關注

關注

77文章

9684瀏覽量

138106 -

光刻機

+關注

關注

31文章

1150瀏覽量

47384

原文標題:存儲器最新發(fā)展路線圖

文章出處:【微信號:半導體科技評論,微信公眾號:半導體科技評論】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

什么是ROM存儲器的定義

內(nèi)存儲器分為隨機存儲器和什么

PLC主要使用的存儲器類型

內(nèi)部存儲器有哪些

ram存儲器和rom存儲器的區(qū)別是什么

EEPROM存儲器如何加密

PLC存儲器故障的原因分析

虛擬存儲器的概念和特征

EEPROM與Flash存儲器的區(qū)別

內(nèi)存儲器與外存儲器的主要區(qū)別

存儲器的工作原理及基本結構

存儲器和寄存器的區(qū)別

淺談存儲器層次結構

Techinsights對存儲器未來的發(fā)展分析

Techinsights對存儲器未來的發(fā)展分析

評論