進行工程的功能調試時,對AD9144,AD9516進行參數配置是非常重要且必不可少的,這過程中遇到了以下問題。

一、問題1

在我們使用上位機軟件進行配置時發現上位機的log記錄中有寫入參數而無讀出參數,這個問題有兩種可能性,一是參數沒有寫入進去所以讀出來的參數都是0,二是寫進去了但是在讀參數時出錯了。

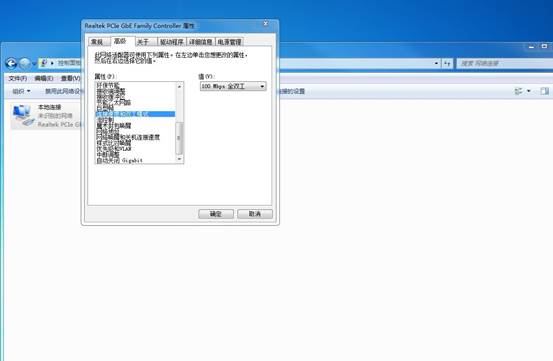

如圖所示:

對此我們懷疑是否是網路通信有問題,檢查發現PC與FPGA連接的網口千兆網指燈

沒有亮百兆網卻亮了。

檢查網絡配置發現網絡的連接速度只有百兆網選項,無法使用千兆網傳輸,也就是電腦不支持千兆網絡。

解決方法有兩種,一是重新更換電腦主機,二是重新更改程序將其設置為百兆網傳輸。

此次我們選擇方法一,更換PC主機后重新測試發現AD9144,AD9516配置可以正常讀寫,

故此次問題原因是PC與FPGA網絡接口不匹配所致。

二、問題2

在進行AD9144,AD9516寄存器配置后,下載bit流文件到FPGA后,用示波器觀察AD9144輸出信號,發現無波形輸出,用Vivado抓取信號觀察,發現sync和tx_tready信號始終為低沒有拉高,也就是說明AD9144與jesd204b沒有同步上。

同步不上的原因有多種,大致可分為硬件問題、時鐘關系問題、寄存器配置問題,先暫將硬件問題排除。

對時鐘關系進行分析,發現時鐘理論數值計算結果沒有錯誤,詳細的分析步驟請自行查看《時鐘關系說明》。

依據時鐘關系理論值檢查JESD204B的IP核設置,未發現錯誤。

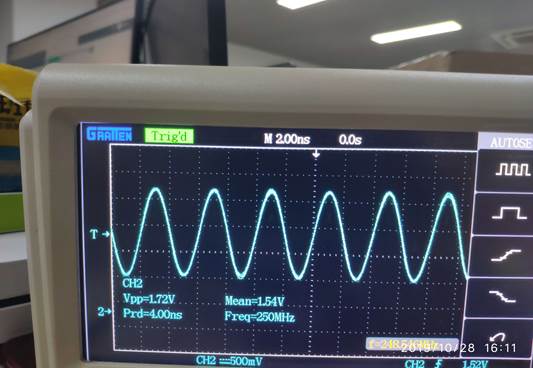

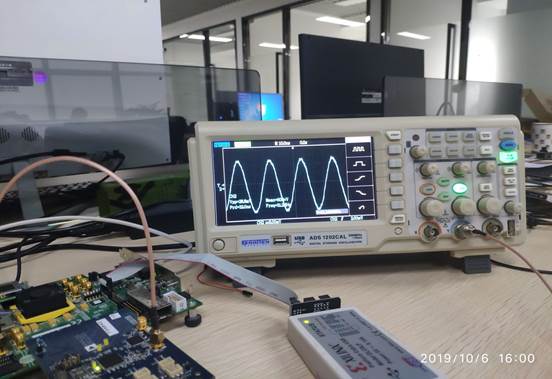

用示波器檢查FPGA輸送給AD9516的分頻時鐘發現無法偵測到,檢查原理圖后定位到對應的引腳,發現FPGA輸送過來的時鐘過大超頻了,使得示波器也無法偵測到信號,通過查找AD9516的操作手順發現其用來分頻的源時鐘最大值為250MHZ,后將AD9516源時鐘設置為250MHZ,用示波器也能正常測試到。

250MHZ時鐘源:

對程序內的時鐘進行分析發現數據產生模塊的使用的時鐘為62.5MHZ,而用來驅動JESD204B模塊的時鐘為device_clock=125MHZ,因為數據產生和數據傳遞是同步,所以時鐘不匹配,將62.5MHZ改為125MHZ。

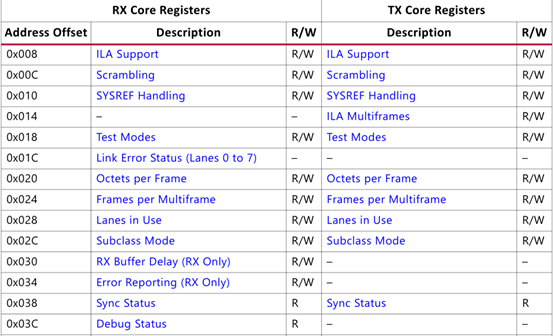

對照JESD204B的IP核手順提供的寄存器配置數據,未發現有錯誤。

JESD204B的IP核參數:

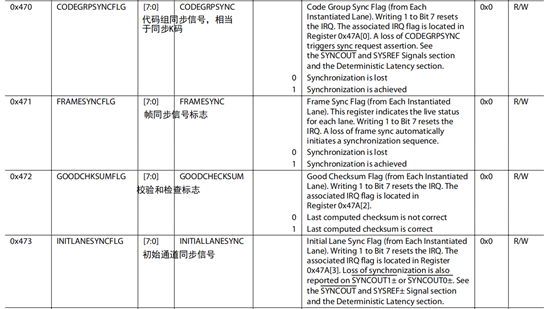

查看AD9144寄存器配置手冊,找到AD9144同步信號指示0X470,0X471,0X472,0X473

其分別代表代碼組同步信號既同步K碼,幀同步信號校驗核檢查標志,初始通道同步信號。

然后再次通過上位機配置觀察配置過程發現其他寄存器值都可以正常讀寫,而這4個寄存器讀出值為0,也就是說明硬件無問題,極有可能是寄存器配置方面出錯了。

同步指示寄存器:

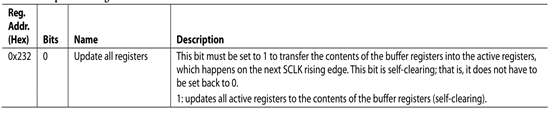

查閱AD9144,AD9516手冊發現AD9516的寄存器0X232的寫入值應該為1,但是AD9516的配置軟件給出的參考值為0,因而更改寄存器值后能夠成功配置。

寄存器配置:

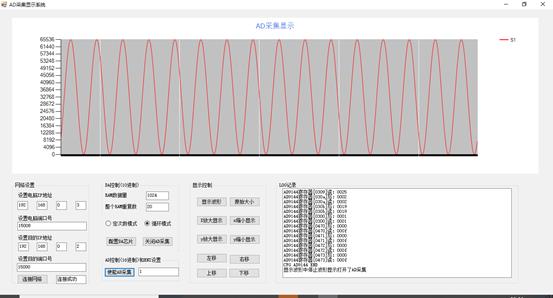

成功配置后如下圖所示:

三、問題3

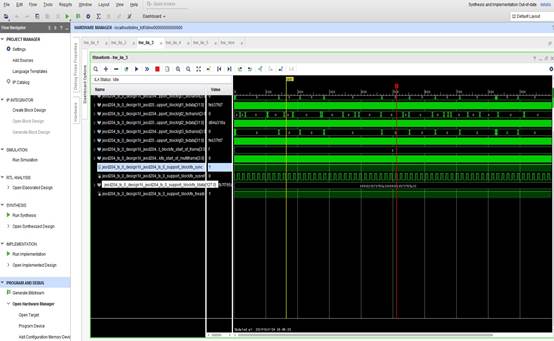

解決配置問題后,進行測試用vivado的觀測sync,tx_tready信號發現信號已經拉高,并且tx_data有數值,說明AD9144與JESD204B已經完成同步了。

同步完成后的信號:

但是在用示波器觀察AD9144的模擬波形時發現波形與預期的有偏差,查閱AD9144和JESD204B的手順并結合vivado的vio功能來在線調試數據,發現其數模轉換的方式是以16進制的補碼相對應,后重新調整數據后,輸出波形與預期一致,完成調試。

異常波形(125MHZ):

正常波形(31.25MHZ):

以上就是調試過程中遇到的問題,這里總結出來與大家分享,歡迎在評論中互相討論。

-

調試

+關注

關注

7文章

578瀏覽量

33924 -

AD9516

+關注

關注

0文章

6瀏覽量

7835 -

JESD204B

+關注

關注

5文章

76瀏覽量

19125 -

ad9144

+關注

關注

0文章

8瀏覽量

1907

發布評論請先 登錄

相關推薦

調試ADS52J90板卡JESD204B接口遇到的問題求解

JESD204B的系統級優勢

JESD204B串行接口時鐘的優勢

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協議介紹

JESD204B的優勢

JESD204B SystemC module 設計簡介(一)

JESD204B標準及演進歷程

JESD204B使用說明

JESD204B調試筆記(實用版)

JESD204B調試筆記(實用版)

評論