許多數據采集 (DAQ) 應用需要隔離式 DAQ 信號鏈路徑,以實現穩健性、安全性、高共模電壓,或消除可能在測量中引入誤差的接地回路。ADI 的精密、高速技術使系統設計人員能夠以相同的設計實現高 AC 和 DC 精度,而無需犧牲 DC 精度以獲得更高的采樣率。然而,為了實現高 AC 性能,例如信噪比 (SNR),系統設計人員需要考慮采樣時鐘信號或控制采樣和轉換的轉換啟動信號上的抖動引入的誤差。在 ADC 中保持 (S&H) 開關。隨著感興趣的信號和采樣率的增加,控制 S&H 開關的信號上的抖動成為更主要的誤差。

當 DAQ 信號鏈被隔離時,用于控制 S&H 開關的信號通常來自用于多通道同步采樣的背板。系統設計人員必須選擇具有低抖動的數字隔離器,以使進入 ADC 的 S&H 開關的最終控制信號具有低抖動。由于高數據速率要求,LVDS 是精密高速 ADC 的首選接口格式。它還對 DAQ 電源和接地層產生最小的干擾。本文將解釋如何解讀 ADI 公司 LVDS 數字隔離器的抖動規范,以及在連接精密高速產品(如ADAQ23875 )時哪些規范很重要DAQ μModule? 解決方案。本文中概述的指南適用于使用具有 LVDS 接口的其他精密、高速 ADC。當與ADN4654千兆位 LVDS 隔離器結合使用時,還將在 ADAQ23875 的上下文中解釋計算對 SNR 的預期影響的方法。

抖動如何影響采樣過程

通常,時鐘源在時域中有抖動。在設計 DAQ 系統時,了解時鐘源的抖動量很重要。

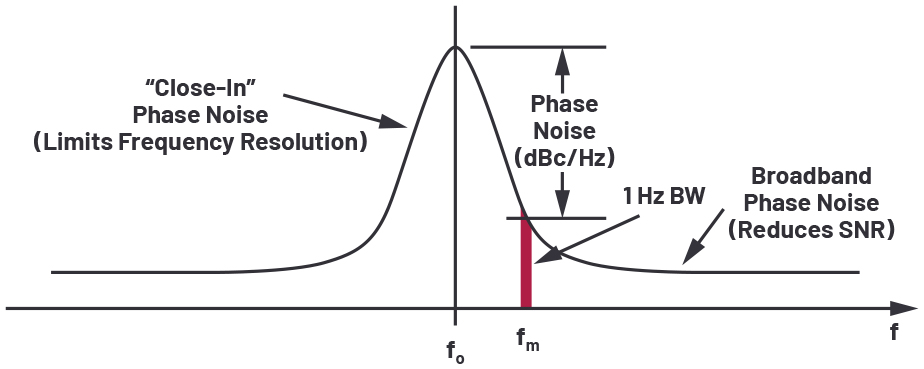

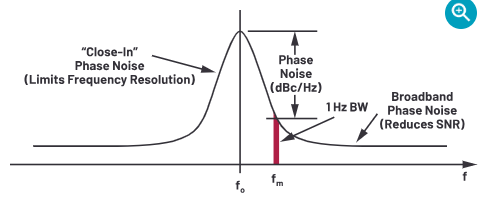

圖 1 顯示了非理想振蕩器的典型輸出頻譜,其中 1 Hz 帶寬內的噪聲功率是頻率的函數。相位噪聲定義為指定頻率偏移 f m處 1 Hz 帶寬內的噪聲與基頻 f o處的振蕩器信號幅度之比。

點擊查看完整大小的圖片

圖 1. 相位噪聲引起的振蕩器功率譜。

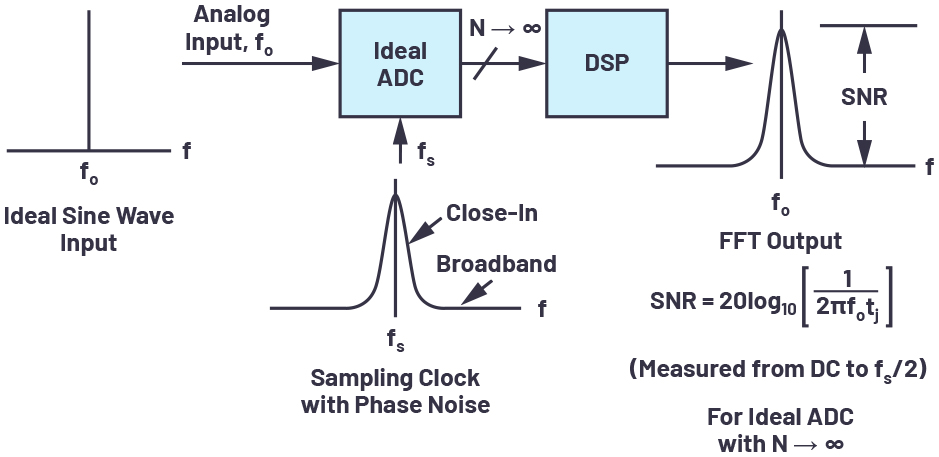

采樣過程是采樣時鐘與模擬輸入信號的乘積。這種時域中的乘法相當于頻域中的卷積。因此,在 ADC 轉換過程中,ADC 采樣時鐘的頻譜與純正弦波輸入信號進行了卷積,因此在 ADC 輸出數據的 FFT 頻譜中會出現采樣時鐘上的抖動或相位噪聲,如圖圖 2。

點擊查看完整大小的圖片

圖 2. 使用相位噪聲采樣時鐘對理想正弦波進行采樣的效果。

隔離精密高速數據采集應用

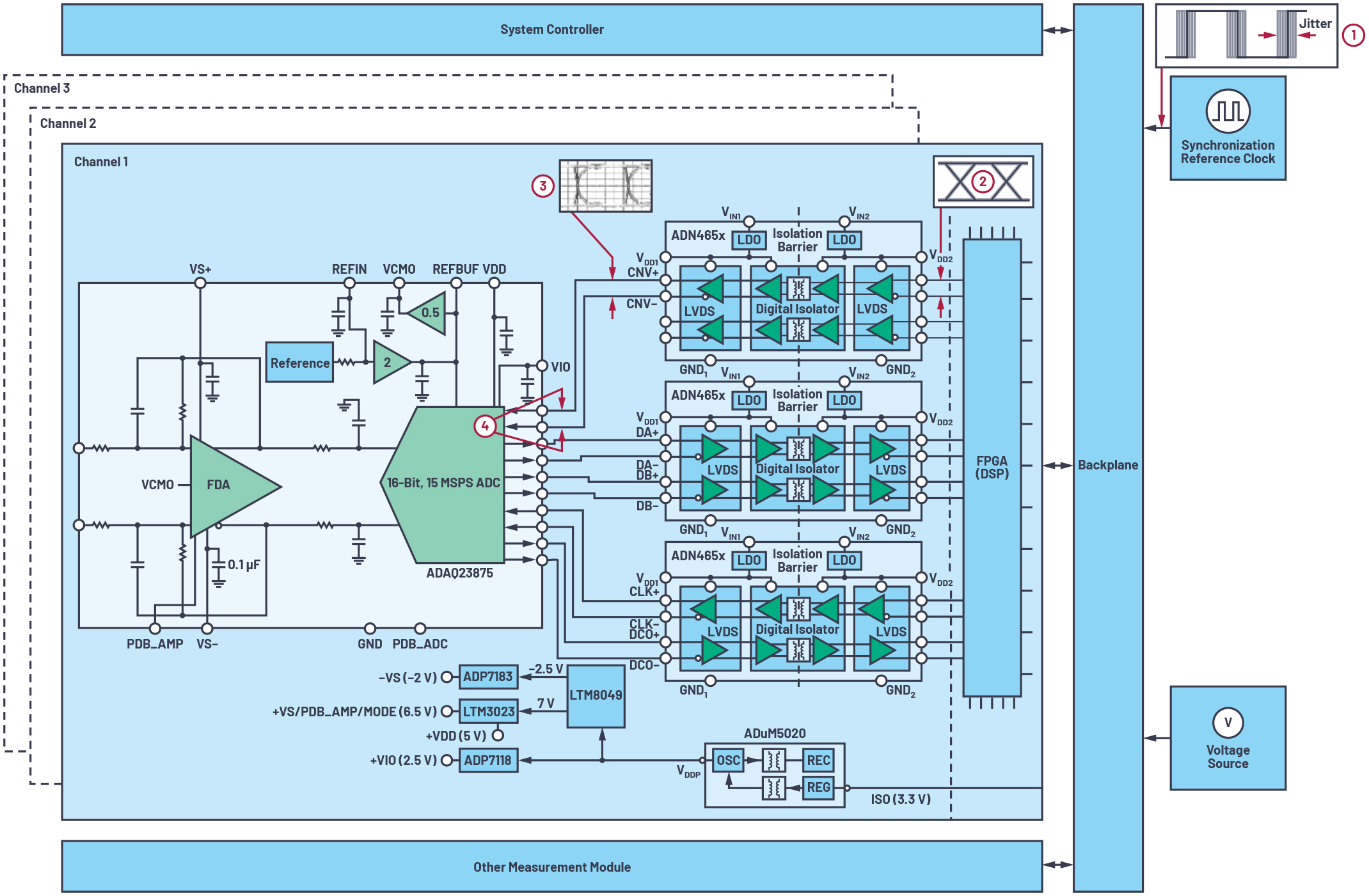

多相功率分析儀是隔離式精密高速 DAQ 應用的一個示例。圖 3 說明了具有通道間隔離的典型系統架構,以及用于與系統計算或控制器模塊通信的通用背板。在本例中,我們選擇了 ADAQ23875 精密、高速 DAQ 解決方案,因為它的解決方案占位面積小——可以輕松地將多個隔離式 DAQ 通道安裝在一個小外形尺寸中,從而減輕用于現場測試用例的移動儀器的重量。DAQ 通道通過 LVDS 千兆位隔離器 (ADN4654) 與主機箱背板隔離。

隔離每個 DAQ 通道使每個通道能夠直接連接到具有顯著不同共模電壓的傳感器,而不會損壞輸入電路。每個隔離 DAQ 通道的接地跟蹤具有一定電壓偏移的共模電壓。使 DAQ 信號鏈能夠跟蹤與傳感器相關的共模電壓,無需輸入信號調理電路來適應大輸入共模電壓并為下游電路消除高共模電壓。隔離還為用戶提供了安全性,并消除了可能影響測量精度的接地回路。

同步所有 DAQ 通道的采樣事件在功率分析儀應用中至關重要,因為與采樣電壓相關的時域信息不匹配會影響后續計算和分析。為了跨通道同步采樣事件,ADC 采樣時鐘通過 LVDS 隔離器來自背板。

在圖 3 所示的隔離式 DAQ 架構中,以下抖動誤差源會影響控制 ADC 中 S&H 開關的采樣時鐘的總抖動。

1. 參考時鐘抖動

采樣時鐘抖動的第一個來源是參考時鐘。該參考時鐘通過背板連接到每個隔離的精密高速 DAQ 模塊和插入背板的其他測量模塊。它作為 FPGA 的時序參考;因此,FPGA 內部的所有事件、數字模塊、PLL 等的時序精度都取決于參考時鐘的精度。在一些沒有背板的應用中,板載時鐘振蕩器用作參考時鐘。

2. FPGA 抖動

采樣時鐘抖動的第二個來源是 FPGA 添加的抖動。重要的是要記住 FPGA 內部有一條觸發到執行的路徑,并且 FPGA 內部的 PLL 和其他數字模塊的抖動規范有助于系統的整體抖動性能。

3. LVDS 隔離器抖動

采樣時鐘抖動的第三個來源是 LVDS 隔離器。LVDS 隔離器具有附加的相位抖動,有助于提高系統的整體抖動性能。

4. ADC的孔徑抖動

采樣時鐘抖動的第四個來源是 ADC 的孔徑抖動。這是 ADC 固有的,并在數據表中定義。

點擊查看完整大小的圖片

圖 3. 通道間、隔離式 DAQ 架構。

在相位噪聲方面給出了參考時鐘和 FPGA 抖動規范。要計算對采樣時鐘的抖動貢獻,需要將頻域中的相位噪聲規范轉換為時域中的抖動規范。

從相位噪聲計算抖動

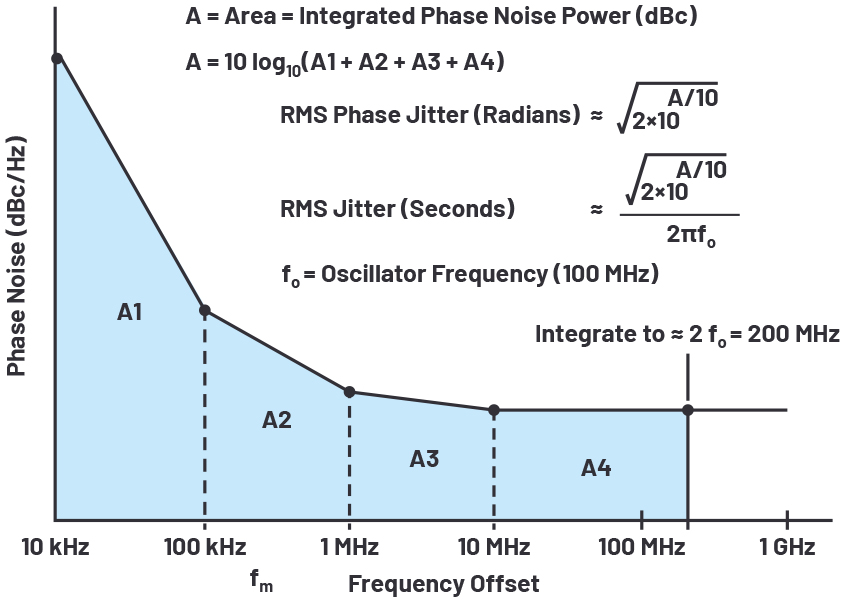

相位噪聲曲線有點類似于放大器的輸入電壓噪聲譜密度。與放大器電壓噪聲一樣,振蕩器非常需要低 1/f 轉角頻率。振蕩器通常根據相位噪聲來指定,但要將相位噪聲與 ADC 性能聯系起來,必須將相位噪聲轉換為抖動。為了使圖 4 中的圖表與現代 ADC 應用相關,出于討論目的選擇振蕩器頻率(采樣頻率)為 100 MHz,典型圖表如圖 4 所示。請注意,相位噪聲曲線近似于幾個單獨的線段,每個線段的端點由數據點定義。

點擊查看完整大小的圖片

圖 4. 從相位噪聲計算抖動。

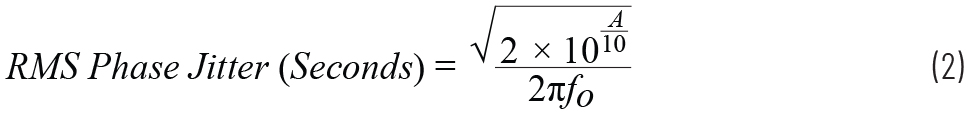

計算等效均方根抖動的第一步是在感興趣的頻率范圍內獲得積分相位噪聲功率,即曲線的面積 A。曲線分為幾個單獨的區域(A1、A2、A3、和 A4),每個由兩個數據點定義。假設振蕩器和 ADC 輸入之間沒有濾波,積分的上限頻率范圍應該是采樣頻率的兩倍。這近似于 ADC 采樣時鐘輸入的帶寬。為積分選擇較低的頻率也需要一些判斷。理論上,它應該盡可能低才能獲得真正的 rms 抖動。然而,在實踐中,通常不會針對低于 10 Hz 左右的偏移頻率給出振蕩器規格——但是,這肯定會在計算中給出足夠準確的結果。如果該規范可用,則在大多數情況下,100 Hz 的較低積分頻率是合理的。否則,使用 1 kHz 或 10 kHz 數據點。還應考慮到近端相位噪聲會影響系統的頻譜分辨率,而寬帶噪聲會影響整個系統的 SNR。可能最明智的方法是分別整合每個區域并檢查每個區域的抖動貢獻幅度。如果使用晶體振蕩器,與寬帶貢獻相比,低頻貢獻可以忽略不計。其他類型的振蕩器可能在低頻區域具有顯著的抖動貢獻,因此必須確定它們對整個系統頻率分辨率的重要性。每個單獨區域的集成產生單獨的功率比。然后將各個功率比相加并轉換回 dBc。一旦已知積分相位噪聲功率,則以弧度為單位的 rms 相位抖動由下式給出:

除以 2πf 0后,將以弧度為單位的抖動轉換為以秒為單位的抖動:

有關詳細信息,請參閱“ MT-008 教程:將振蕩器相位噪聲轉換為時間抖動”。

在這個由兩部分組成的系列的第二篇文章中,我們通過探索如何量化參考時鐘、FPGA、數字隔離和 ADC 孔徑中的抖動,以及如何計算整體抖動性能來完成對抖動引入的誤差的討論。

[本文所有圖的圖片來源均為 Analog Devices。]

審核編輯:湯梓紅

-

數據采集

+關注

關注

38文章

6060瀏覽量

113630 -

時鐘抖動

+關注

關注

1文章

62瀏覽量

15924 -

lvds

+關注

關注

2文章

1043瀏覽量

65798 -

DAQ

+關注

關注

6文章

91瀏覽量

32173

發布評論請先 登錄

相關推薦

labview DAQ數據采集時鐘的采樣率選擇

時鐘抖動和相位噪聲對采樣系統的影響

開源硬件-TIDA-01035-為最大程度提升 SNR 和采樣速率而優化抖動的 20 位隔離式數據采集 PCB layout 設計

考慮數據采集應用中的采樣時鐘抖動

考慮數據采集應用中的采樣時鐘抖動

評論