瑞薩電子開發了一種新的內存處理器 (PIM) 技術,用于在低功耗邊緣設備中加速 AI 推理。用于基于 SRAM 技術的測試芯片實現了 8.8 TOPS/W 的運行卷積神經網絡 (CNN) 工作負載,這是最常用于圖像識別的算法類型。

瑞薩電子現有一代 AI 推理加速器基于其動態可重構處理器 (DRP) 架構,達到 1 TOPS/W 量級,足以在終端節點實現實時圖像識別。該公司表示,新的 PIM 技術在 TOPS/W 方面幾乎提高了一個數量級,并且可能成為在端點實施增量學習的基礎。

內存處理器是一種越來越流行的人工智能推理工作負載技術,其中涉及將大量輸入數據與權重因子相乘。在 PIM 設備中,當讀取數據時,在存儲器本身中執行乘法累加 (MAC) 操作。

在瑞薩電子設備中,存儲權重的存儲單元可以通過控制單元的輸出開關與輸入數據相乘,從而控制輸出電流。測量位線中的電流然后有效地將所有輸出加在一起。以這種方式在內存中執行 MAC 操作,通過避免不必要的數據傳輸,消除了內存和處理器之間的瓶頸。

三元SRAM

在接受 EETimes 的獨家采訪時,瑞薩電子高級首席工程師 Koichi Nose 解釋了用于提高精度和降低功耗的新技術。

“傳統的內存處理器技術無法為大規模計算提供足夠的精度,”Nose 說,并強調了傳統上需要解決的變通辦法,以規避由工藝變化引起的低可靠性。“二進制數據也不足以表達一些復雜的神經網絡……它會導致準確性下降。”

新的 PIM 技術是三元的,這意味著每個單元都具有三種狀態:-1、0 或 1。Nose 解釋說,這允許表示比二進制單元更復雜的數據。

如果三進制存儲單元保持+1或-1,則電流可以流入位線,但如果存儲單元存儲0,則沒有電流流動,這有助于保持低功耗。

“此外,重量數據可以很容易地擴展到任意位數,”Nose 說。“神經網絡中的權重數據是多位信息,一個零或一個大的正負值。在二進制單元中表達多位符號信息很困難。所提出的存儲器電路可以通過利用三元單元和簡單的數字計算塊的組合來輕松表達任意符號位操作......因為這可以支持每個用戶所需的不同計算精度,用戶可以優化精度和精度之間的平衡能量消耗。”

能量消耗

Nose 表示,傳統的 PIM 拓撲使用 ADC 將位線電流轉換為輸出數據值,但盡管 ADC 很有效,但它們耗電大且占用寶貴的芯片面積。

瑞薩電子的 PIM 技術使用標準 SRAM 宏中的 1 位讀出放大器作為比較器,與可靈活控制電流的復制單元(相當于存儲單元的當前生成部分)結合使用。將復制單元電流與三元單元電流進行比較有效地檢測三元單元的電流輸出。

零檢測器還有助于降低功耗。如果 MAC 運算結果等于 0,則停止比較器的操作以節省能量。

“在 [典型] 神經網絡電路中,幾乎所有節點都分配為零;只有少量的神經元被激活,大約 1%。所以幾乎所有的計算結果都歸零,”Nose 說。“激活零檢測器電路會關閉比較器并有助于降低功耗。通過將比較器 AD 轉換器技術和零檢測器技術相結合,可以將功耗降低一個數量級。”

工藝變化

在 SRAM 陣列中,制造工藝的變化經常導致故障。由于這些工藝變化,當將數據寫入具有顯著不同電氣特性的單個單元時,就會出現錯誤。

“為了避免這個問題,我們使用了神經網絡的相同特征——幾乎所有節點都分配為零,”他說。“我們可以通過改組數據來避免計算錯誤,以便將零存儲在 [不利] 受影響的單元格中。”

在三進制存儲單元中,如果存儲零,則位線中沒有電流流動,因此求和結果不依賴于單元電流。

如何識別受到不利影響的細胞?

“我們正在開發其他一些錯誤單元檢測方法,但在這個芯片中,我們使用了一種簡單的方法,”他說。“我們測量神經網絡的輸出并檢查結果是否正確,以識別[不存儲]正確輸出值的錯誤單元。”

測試芯片

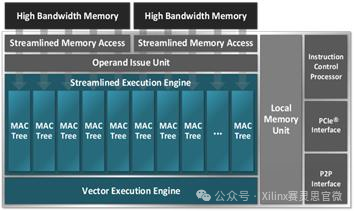

Renesas 的 3×3 mm 測試芯片基于 12nm 工藝技術構建,由四個集群組成,每個集群可以同時運行不同的 AI 工藝。在每個集群中,神經網絡權重數據存儲在 PIM 塊中,MAC 運算結果存儲在標準 SRAM 塊中。

測試芯片包含 4 Mb 的 PIM 計算內存和 1.5 MB 的 SRAM,足以在不使用外部存儲器的情況下評估緊湊型 CNN。該芯片實現了8.8 TOPS/W的功率效率。

原型 AI 模塊中的測試芯片的簡單演示還結合了小型電池、微控制器、相機和其他外圍設備,表明只需 5 mW 即可實現用于實時人員檢測的推理。

審核編輯 黃昊宇

-

芯片

+關注

關注

456文章

50950瀏覽量

424720 -

sram

+關注

關注

6文章

768瀏覽量

114731 -

AI

+關注

關注

87文章

31133瀏覽量

269449

發布評論請先 登錄

相關推薦

Neuchips展示大模型推理ASIC芯片

FPGA和ASIC在大模型推理加速中的應用

NVIDIA助力麗蟾科技打造AI訓練與推理加速解決方案

李開復:中國擅長打造經濟實惠的AI推理引擎

AMD助力HyperAccel開發全新AI推理服務器

用基于SRAM的測試芯片實現加速AI推理

用基于SRAM的測試芯片實現加速AI推理

評論