快速傅里葉變換 (Fast Fourier Transform,FFT), 即利用計算機計算離散傅里葉變換(DFT)的高效、快速計算方法的統稱,簡稱FFT。DFT是實現了從頻域(頻域分析往往比時域分析更優越)對信號與系統進行分析。然而,隨著序列長度的增加,計算量也顯著增加,對于計算機而言,處理時間就越長,消耗的資源也就越多。

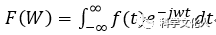

忘了什么是傅里葉變換的同學,趕緊拿出《信號與系統》翻一下。實在沒書,找度娘。對于連續時間信號f(t),定義式如下:

傅里葉變換:

傅里葉逆變換:

信號處理領域大名鼎鼎的傅里葉變換,正式由傅里葉提出的,不得不說,實在太偉大了,頂禮膜拜。

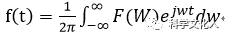

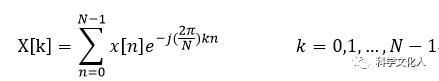

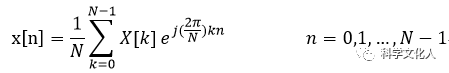

在信號處理中,由于計算機通常只能處理數字信號,因此通過對連續信號進行采樣離散化,進而有了離散傅里葉變換。

話不多說,直入主題,首先把DFT公式搬出來:

原信號x(t)的采樣信號x[n]也可以用X[K]來表示:

1965年,庫利和圖基提出了快速傅里葉變換(FFT)算法,采用這種算法能使計算機計算DFT所需要的乘法次數大為減少,特別是被變換的抽樣點數N越多,FFT算法計算量的節省就越顯著。

常用計算方法:

時間抽取算法:令序列的長度為N(2的冪),可以將時域序列x(n)分解為兩部分,一是偶數部分x(2n),另一部分是計數部分x(2n+1),于是信號序列x(n)的離散傅里葉變換可以用兩個N/2抽樣點的離散傅里葉變換來辨識核計算。

頻率抽取算法:按照頻率吧抽取的FFT算法是將頻域信號序列X(k)分解為奇偶兩部分,但算法仍然是由時域信號序列開始逐級計算,同樣把N點分成N/2點計算FFT。

02

FFT原理

FFT是DFT的快速算法,可以將一個信號從時域變換到頻域。很多時候信號在時域很難進行信號特征分析,變換到頻域后,就很容易看出信號的頻率、功率、相位等特征信息。更多詳細的解釋,可移步看這里深入淺出的講解傅里葉變換(真正的通俗易懂)或者在CSDN中閱讀深入淺出解釋FFT系列(非公眾號文章,超鏈接失敗,抱歉,可去CSDN看原文博客),講得比較清楚透徹,不愧是10年碼齡的巨佬。在這里我就不再贅述了。

03

FFT IP Core使用

概述

以Xilinx Vivado設計套件中提供的FFT IP為例,簡要說明如何進行FFT IP配置和設計。

FFT Core用于計算N點的DFT或IDFT,N=2m,m=3~16。對于計算FFT,有三種算術選項用于計算FFT:

全精度無縮放算法

定點縮放,提供縮放表

塊浮點(運行時調整縮放)

對于N點大小,可對正向/逆向變換、縮放表循環前綴進行配置。

提供四種可選架構:

Pipelined Streaming I/O

Radix-4 Burst I/O

Radix-2 Burst I/O

Radix-2 Lite Burst I/O

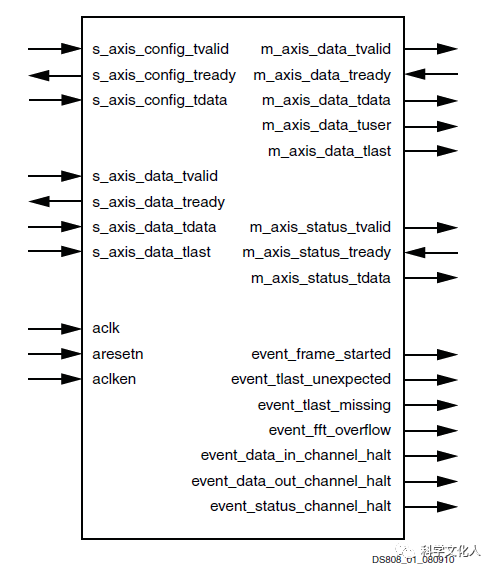

端口描述

FFT IP Core的端口如圖1所示,對端口的描述,參考產品指南PG-109-XFFT.pdf。

圖1 FFT端口

FFT IP配置

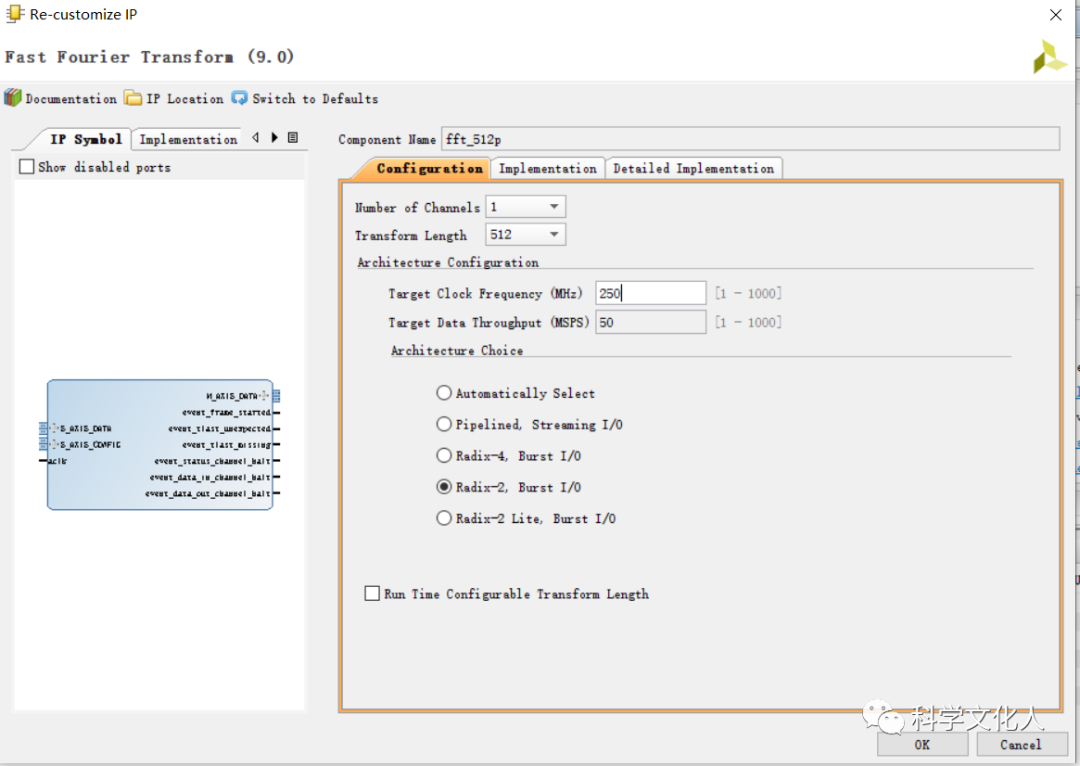

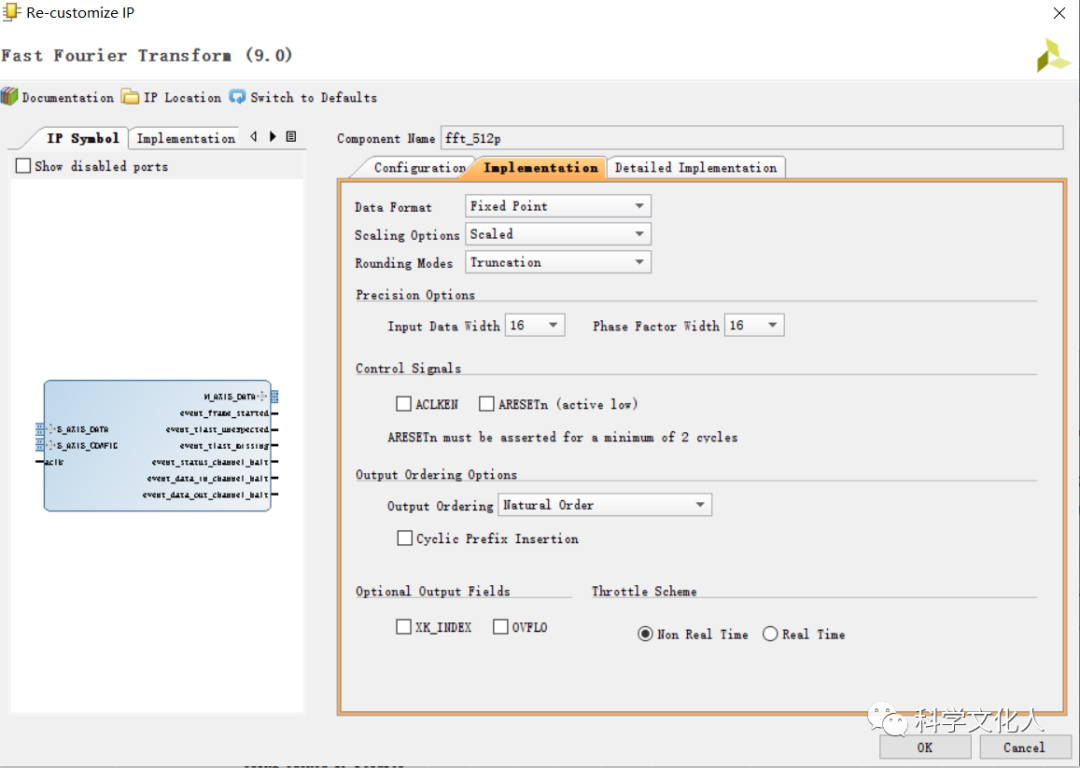

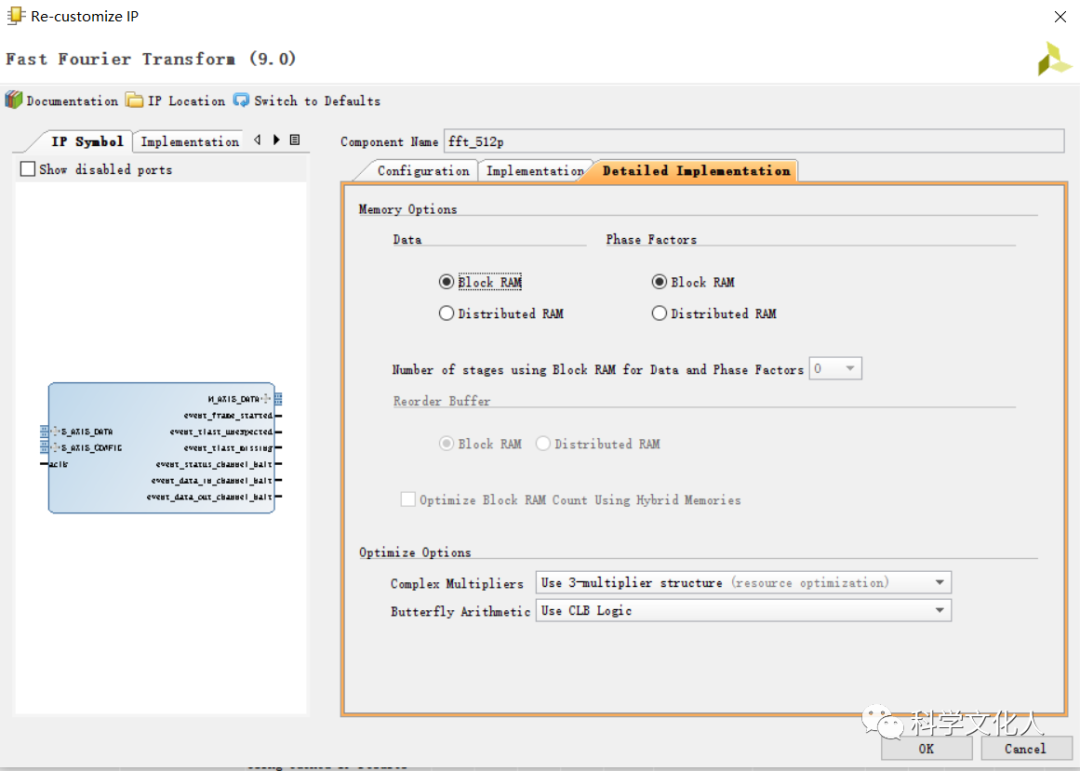

舉個栗子:單通道,512點,Radix-2,Burst I/O,定點數,縮放,取整模式Truncation,輸入數據位寬16bit,相位因子位寬16,自然序輸出,無循環前綴。

在Vivado中創建工程后,在工程管理器下的IP Catalog中選擇并配置FFT IP,在IP配置向導的指引下,依次進行相關參數的配置,如圖2所示。配置通道數,變換長度,實現架構,數據格式,縮放,取整模式,數據呼出順序,是否插入循環前綴(CP)等。

圖2 FFT IP配置

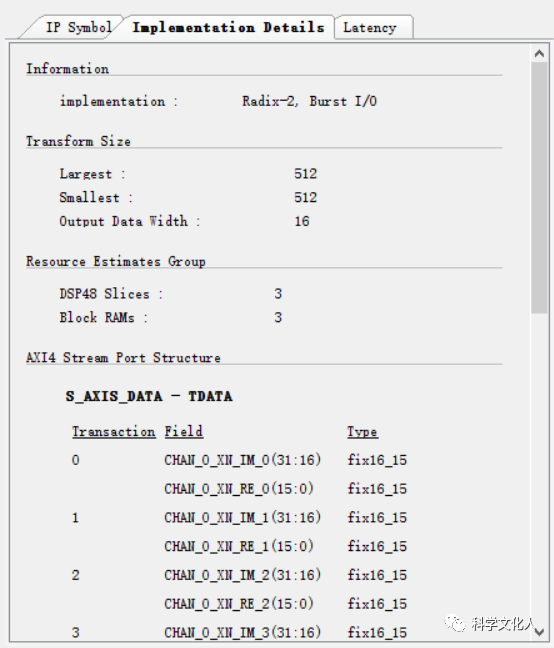

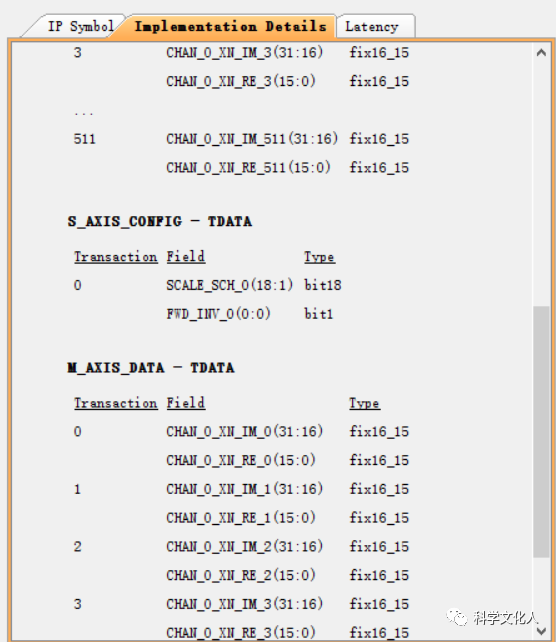

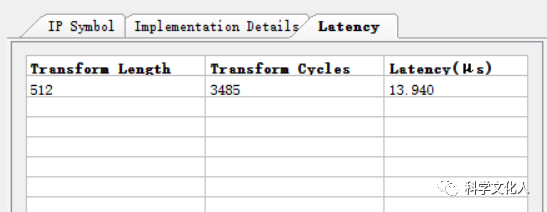

在向導視圖左側,可查看IP端口框圖,實現詳情以及時延信息,如圖3所示。這里需要注意輸入輸出數據的格式以及配置通道數據的格式。

圖3 查看IP實現信息

配置完成后,輸出生成定制FFT IP,最后再將其實例化到工程模塊中。

AXI-Stream注意事項

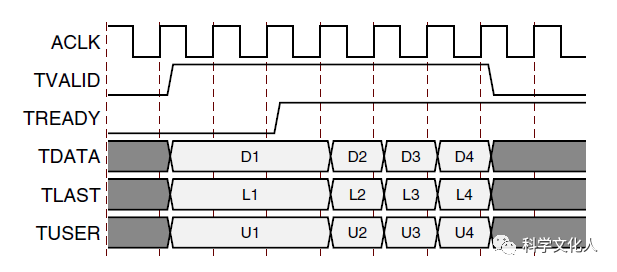

該IP的端口采用了標準的AXI-Stream協議,數據傳輸基本握手,如圖4所示。

圖4 AXI-Stream信道數據傳輸

AXI信道規則

所有的TDATA和TUSER字段被打包成小端格式,也就是一個子字段的第0位與TDATA或TUSER的第0位對齊。

字段不包括在TDATA或TUSER中,除非以這種方式配置了核它需要字段出現。例如,如果核心配置為有一個固定的點大小,沒有位分配給指定點大小的NFFT字段。

所有的TDATA和TUSER矢量都是8bit的整數倍。

配置通道

配置通道端口信號如表1所示。

表1 配置通道端口信號

| 名稱 | 寬度 | 方向 | 描述 |

| s_axis_config_tdata | 可變 | I | 承載配置信息:CP_LEN,FWD/INV,NFFT和SCALE_SCH |

| s_axis_config_tvalid | 1 | I | 由外部主機輸入,指示當前數據可用 |

| s_axis_config_tready | 1 | I | 由從機輸入,指示從機可接收數據 |

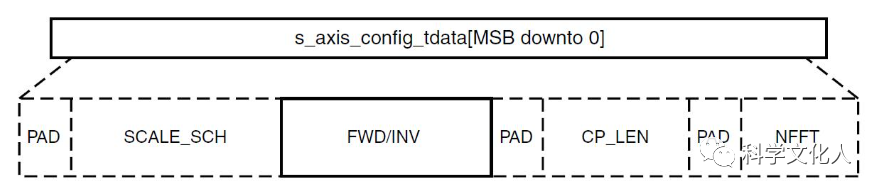

配置通道(s_axis_config)接口是AXI通道,TDATA字段接口定義如下表2所示,所有需要paded的字段如果未達到8bit邊界,則需要擴展到8bit邊界。擴展的bit可以未任意值,設計為常量值可節省器件資源。

表2TDATA字段接口定義

| 字段名稱 | 寬度 | Padded | 描述 |

| NFFT | 5 | yes | 轉換點數:NFFT為最大轉換點數或者更小點數。例如,一個1024點FFT可以計算1024點,512點,256點等。該值為log2(point_size) |

| CP_LEN | Log2(最大point_size) | no | 循環前綴長度:CP_LEN可以是0到(point_size-1)的任意值,該值僅在循環前綴插入有效 |

| FWD_INV | 1 | no |

FWD_INV=1,表示FFT運算; FWD_INV=0,表示IFFT運算。在多通道中,bit0(LSB)表示通道0配置,bit1表示通道1配置,以此類推。 |

| SCALE_SCH |

流水線I/O和Radix-4 I/O架構:2×ceil(NFFT/2) Radix-2突發 I/O和Radix-2Lite I/O架構:2×NFFT |

no |

縮放方案: (1)對于突發I/O架構,每級縮放因子由2bit定義,縮放因子可以為3,2,1,0,代表右移bit數。例如,對于N=1024點,Radix-4突發I/O的縮放因子為[1 0 2 3 2],對于N=128點,Radix-2突發I/O或者Radix-2 Lite突發I/O架構,可能的縮放方案[1 1 1 1 0 1 2] (2)對于流水I/O架構,縮放因子由每對Radix-2運算級定義,也是采樣2bit位寬。例如,NFFT=256,可能的縮放因子為[2 2 2 3],當N不是4的冪次時,最后一級最大bit為1bit。例如,N-512,可能的縮放方案[0 2 2 2 ]或者[1 2 2 2],但是[2 2 2 2 ]是非法的,因為此時縮放因子的MSB位只能是00或01. |

TDATA數據格式如圖5所示。

圖5 config_tdata數據據格式

其中,NFFT設置情況,如表3所示。需要注意的是,如果選項runtime configurable transform length被選后,變換點大小才可以在配置通道的NFFT字段進行設置。

表3NFFT設置

| NFFT[4:0] | Transform size(N) |

| 00011 | 8 |

| 00100 | 16 |

| 00101 | 32 |

| 00110 | 64 |

| 00111 | 128 |

| 01000 | 256 |

| 01001 | 512 |

| 01010 | 1024 |

| 01011 | 2048 |

| 01100 | 4096 |

| 01101 | 8192 |

| 01110 | 16384 |

| 01111 | 32768 |

| 10000 | 65536 |

正反變換及縮放

FWD_INV=1時,正向變換;FWD_INV=0時,逆向變換。

對于FFT/IFFT各級縮放,在不同的實現架構中,縮放因子的設置有所不同。可參考表2 或者產品指南:PG109-xfft.pdf文檔ch.4操作理論的Run Time Transform Configuration部分。

循環前綴(CP)

將輸出結果的尾部復制到頭部,輸出順序要選擇自然序。插入循環前綴,可逐幀設置,不用打斷幀處理進程。

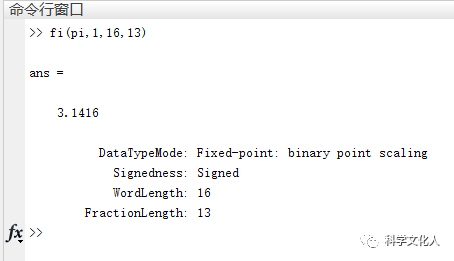

補充:定點數

在FPGA處理過程中,常常要對浮點數進行定點化處理。Matlab中提供了一個非常方便的定點化函數fi。

fi(data,s,w,f) 各參數的定義:

s:signed or unsigned 標志;

signed: 包含符號位;

f:定點小數精度。

例如:在命令行輸入fi(pi,1,16,13),回車,如圖6所示。

圖6 浮點數定點

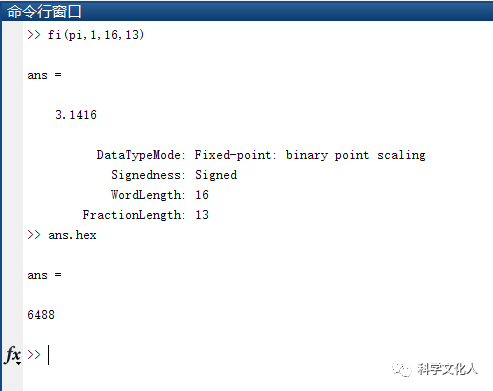

查看定點后的數據, 命令行輸入ans.hex,顯示十六進制數6488,如圖7所示。

圖7 定點16進制數據

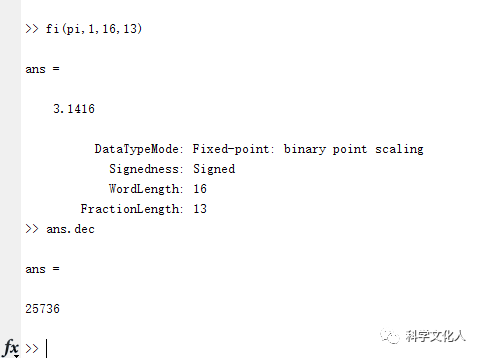

命令行輸入ans.dec,顯示十進制數,如圖8所示。

圖8 定點10進制數據

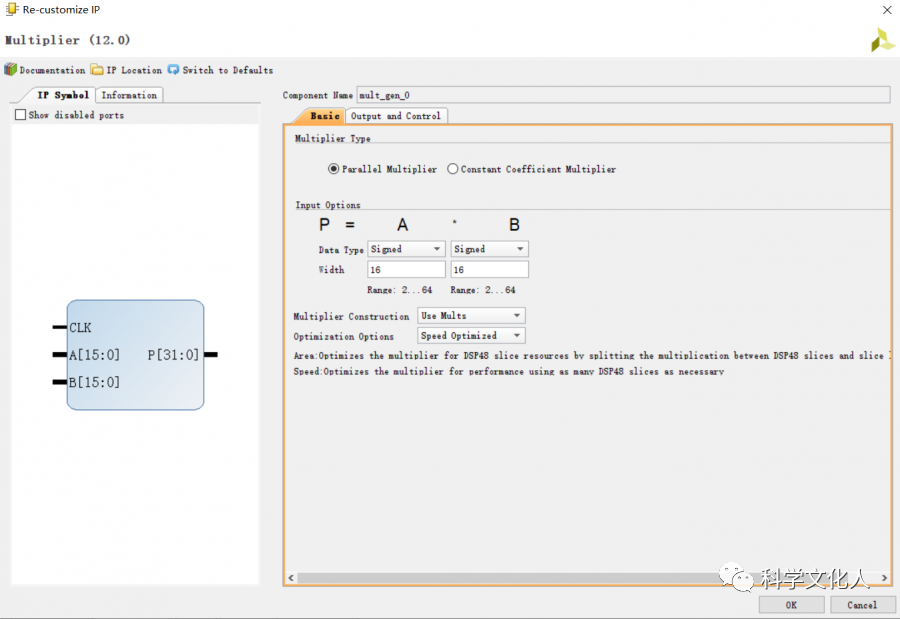

在FPGA處理定點乘法,可用乘法器IP—Multiplier,如圖9所示。

圖9 乘法器IP

04

FFT模塊設計demo

以調用FFT,并通過ROM預存所需數據進行一個簡單的demo設計。

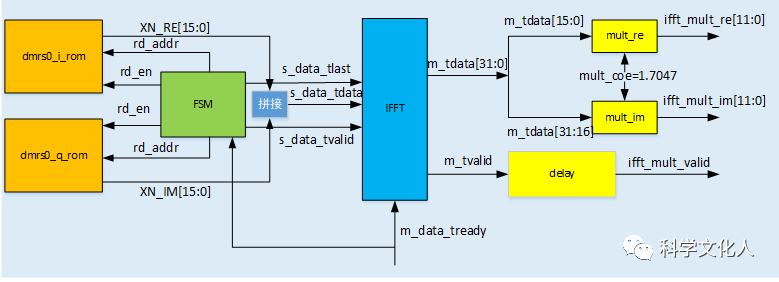

利用FFT IP,搭建工程。分別使用兩個ROM存儲DMRS0的I、Q兩路數據,外部主機斷言m_data_tready拉高時,準備開始從ROM讀取數據,同時配置FFT。IFFT計算輸出通過乘以一個系數,使其幅度值接近于1。設計框圖如圖10所示。

圖10 設計框圖

以DMRS0信號5M帶寬300點(中間補零,至512點)作IFFT為例,創建工程,編寫RTL代碼。針對配置通道的數據配置(如SCALE_SCH、FWD/INV、CP_LEN、NFFT),假設基于Radix-2架構作IFFT,不加循環前綴,不更改NFFT點數,配置情況如下。

s_axis_config_tdata = 23'b0000_0000_0000_0000_0000_0000;

注意,高MSB五位做了填充,使得TDATA的位寬是8的整數倍。

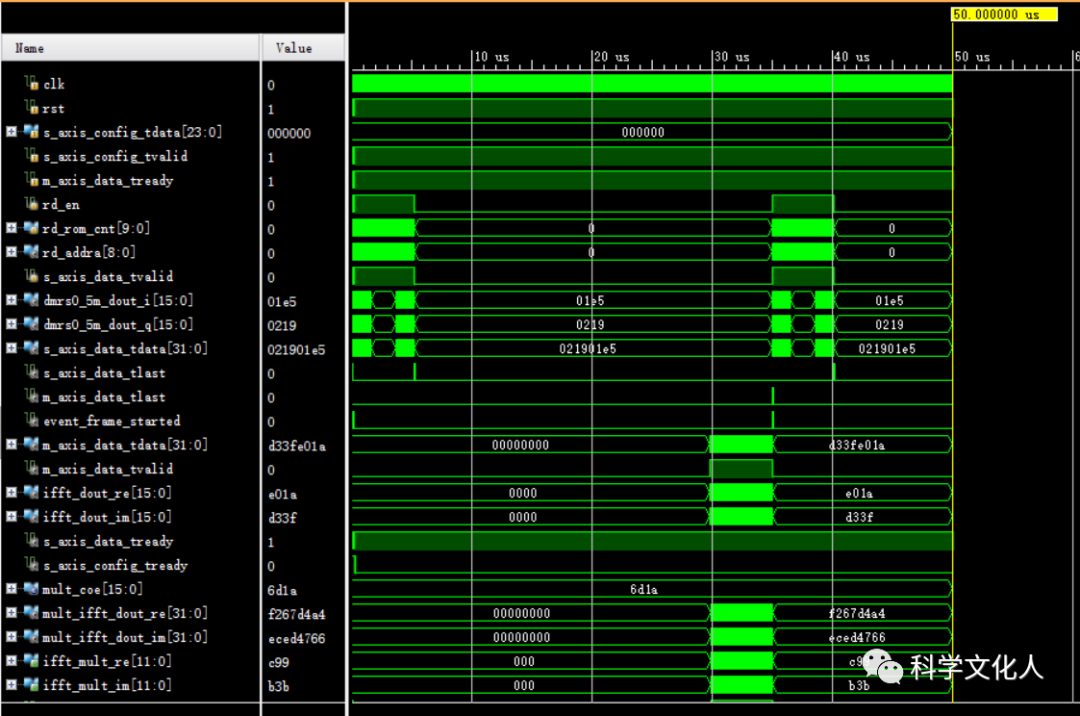

FPGA仿真結果如圖11所示。

圖11 FPGA工程仿真

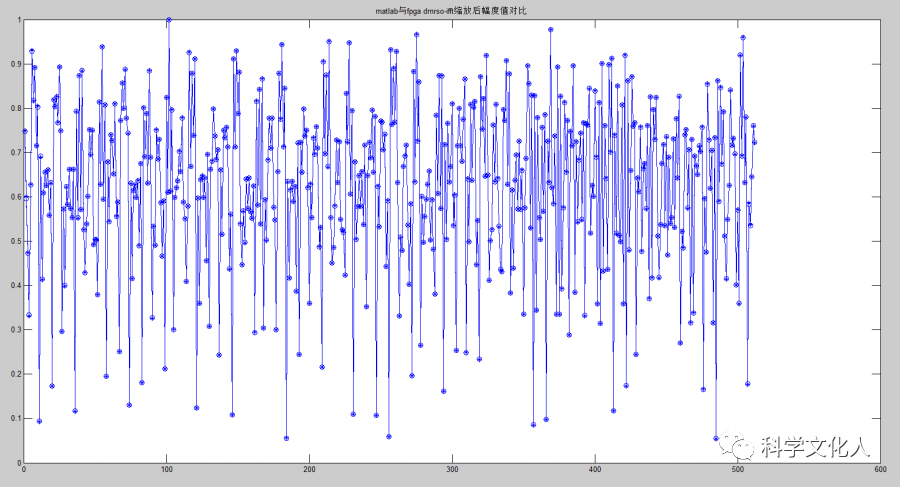

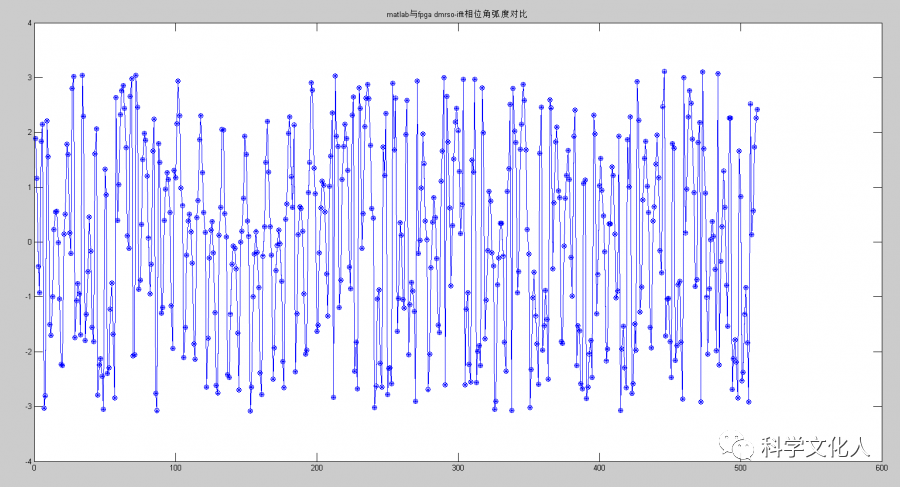

MATLAB進行IFFT變換,并進行適當的縮放,同時將FPGA仿真的結果導入,計算各自的幅度,并繪于同一圖中,如圖12所示。

圖12 幅度值對比

計算各自的相位角弧度,如圖13所示。

圖13 相位弧度對比

通過對比分析可知,MATLAB仿真與FPGA實現結果基本一致。

在LTE、5G等無線通信中,IFFT和FFT變換是一個繞不過的話題。即便5G在探索非正交多址接入技術(NOMA),因主動引入干擾,接收機設計復雜度急劇上升,能否被采用不得而知。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

matlab

+關注

關注

185文章

2974瀏覽量

230384 -

數據

+關注

關注

8文章

7002瀏覽量

88942 -

FFT

+關注

關注

15文章

434瀏覽量

59366

原文標題:Vivado中FFT IP配置及應用

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種基于FPGA的可配置FFT IP核實現設計

基于FPGA的FFT和IFFT IP核應用實例

IP設計原理是什么?如何進行IP模塊設計?

利用面向對象技術進行可配置的FFT IP設計與實現

Quartus中fft ip core的使用

可配置FFT IP核的實現及基礎教程

如何進行OPCDCOM配置

Gowin FFT IP用戶指南

如何進行IP檢測

公共 IP 地址前綴如何進行網絡資源配置?

如何進行FFT IP配置和設計

如何進行FFT IP配置和設計

評論