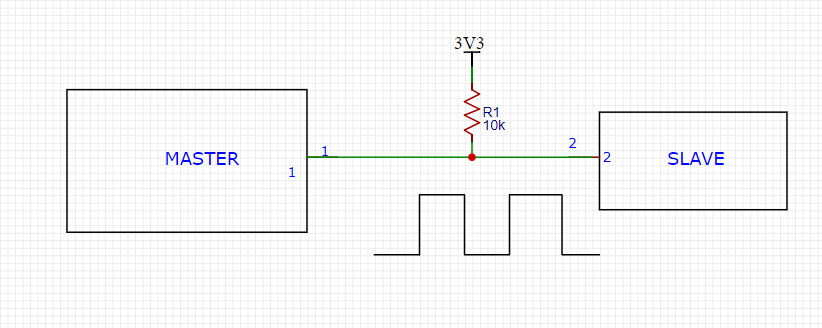

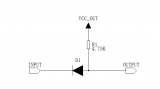

一般在芯片的GPIO口內(nèi)部是開漏的狀態(tài)下,外部需要連接上拉電阻,一般連接方式如下圖,而且理想的高低電平應(yīng)該是低電平電壓值接近0V,高電平狀態(tài)值在3.3V左右。

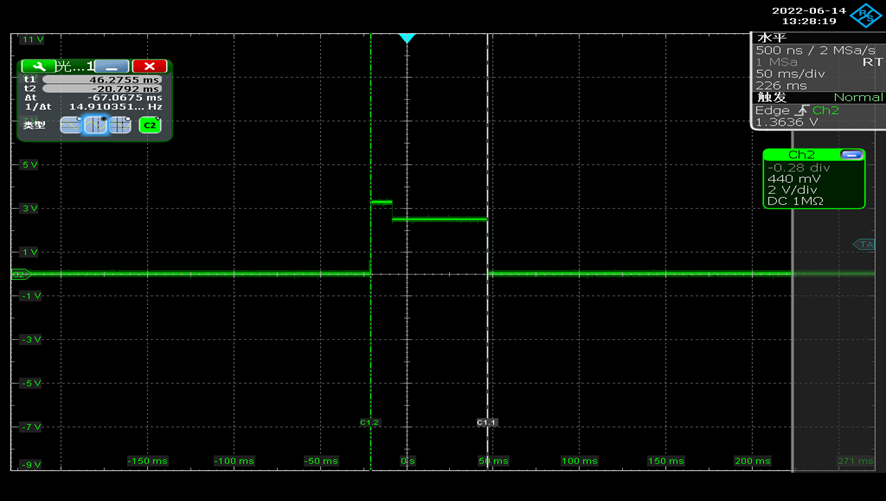

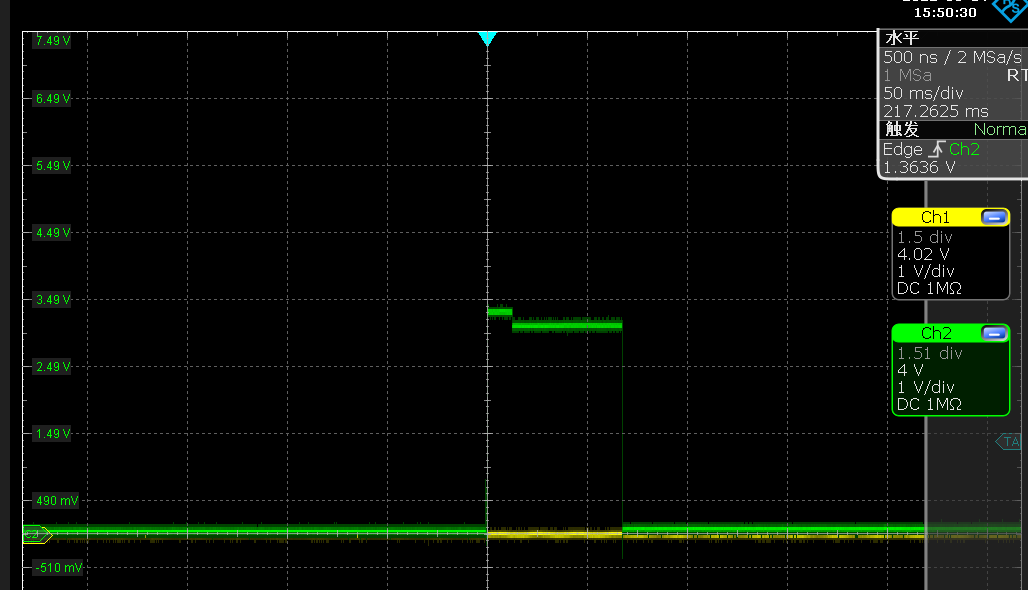

但是在這邊實(shí)際測(cè)試的情況下卻遇到一個(gè)問題:高電平狀態(tài)電壓先是3.3V,后面又被拉低到2.567V。

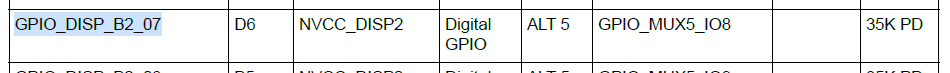

這個(gè)情況非常奇怪,開始被沒有找到原因,直到翻看MASTER 芯片的規(guī)格書,發(fā)現(xiàn)它的這個(gè)GPIO口內(nèi)部是有一個(gè)35K的下拉電阻的。

根據(jù)分壓原理,35K的下拉電阻和10K的上拉電阻,中間的分壓點(diǎn)電壓計(jì)算就是3.3V*35/(35+10)=2.567V。理論分析對(duì)得上實(shí)際測(cè)試結(jié)果。

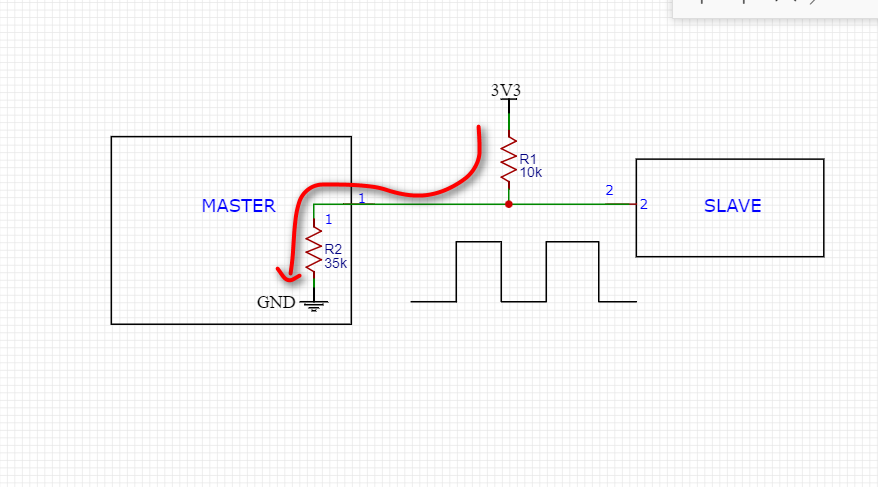

那么在這種情況下,預(yù)防高電平狀態(tài)的電壓閾值不夠,就只能把上拉電阻值調(diào)小了,最后選擇調(diào)整為2.2K。那么進(jìn)行計(jì)算,分壓點(diǎn)電壓V=3.3V *35/(35+2.2) =3.1V。

那么3.1V的電壓就沒有什么風(fēng)險(xiǎn)了。

審核編輯:劉清

-

上拉電阻

+關(guān)注

關(guān)注

5文章

360瀏覽量

30633 -

電平

+關(guān)注

關(guān)注

5文章

360瀏覽量

39918 -

GPIO

+關(guān)注

關(guān)注

16文章

1205瀏覽量

52139

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TFP401APZP將DVI信號(hào)轉(zhuǎn)換成TTL RGB信號(hào),輸出的TTL RGB信號(hào)測(cè)量的波形就是3.3v高電平,為什么?

LSF0108電平轉(zhuǎn)化后發(fā)生信號(hào)失真的情況,怎么處理?

使用TXB0108時(shí),3.3V側(cè)的低電平不能拉低到0V位置,同時(shí)某些時(shí)候低電平會(huì)后很多毛刺,為什么?

電路中對(duì)該輸出信號(hào)做了10K的下拉,IO口的輸出高電平為3.3V,外部的下拉是否會(huì)對(duì)IO口的輸出狀態(tài)造成影響?

SN74CBTLV3257輸入是1.8v,輸出是否可以是3.3v, 上拉電阻是3.3v?

用信號(hào)發(fā)生器產(chǎn)生3.3V方波信號(hào),經(jīng)過(guò)16245電平轉(zhuǎn)換后得到的低電平卻是負(fù)電壓,如圖中CH2波形所示,為什么?

求助,關(guān)于LSF0108 3.3V和5V轉(zhuǎn)換問題求解

DAC70502將SPI2C和RSTSEL引腳上拉到3.3V電平,是否可行?

MCU 3.3V供電,OC輸出高電平能到5V嗎?

具有3.3V/5V輸入和12V/15V輸出的信號(hào)和電源隔離

將5V傳感器和信號(hào)連接到3.3V輸入SAR ADC

信號(hào)被上拉,但電平不是3.3V的原因

信號(hào)被上拉,但電平不是3.3V的原因

評(píng)論