在典型的最后一英里廣播分發系統中,有線電視運營商通過衛星接收來自內容提供商的廣播節目,使用集成接收器/解碼器 (IRD) 對其進行解碼,然后重新編碼基帶視頻(在編碼器盒中)所需的分辨率、比特率和壓縮標準。接下來,他們將多個節目流結合起來,最終分發給最終消費者。

一些國家要求有線電視運營商在傳輸給最終消費者的視頻中插入他們的標志。本文討論了在基帶視頻中插入靜態徽標的各種機制及其優缺點。此外,本文還描述了我們認為為實現低成本解決方案而采用的獨特設計方法。

視頻編碼器

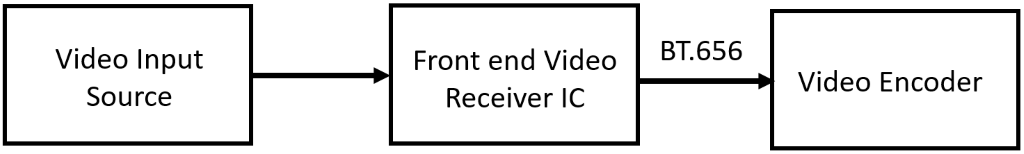

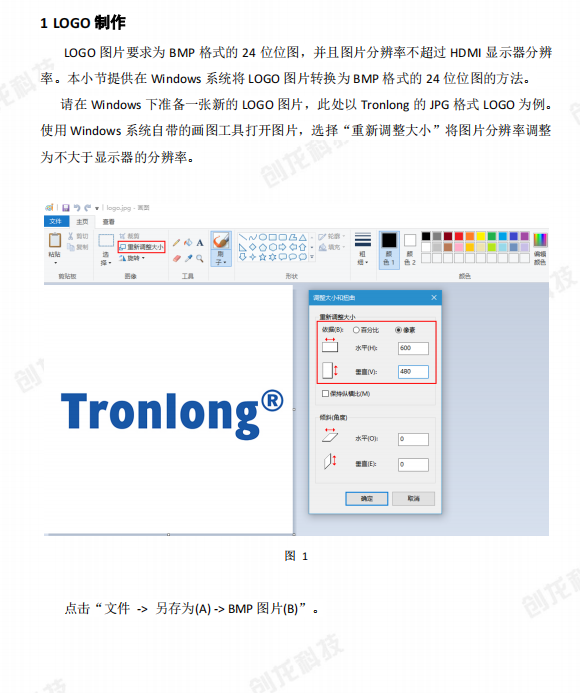

視頻編碼器通過各種模擬/數字接口接收視頻內容,如復合 (S-Video)、分量 (YPbPr)、HDMI、DVI 和 3G-SDI,通常與視頻前端 IC 連接,如圖所示在圖 1 中。

圖 1:編碼器系統中的視頻接口

視頻前端包括一個視頻接收器 IC——它可以是一個 ASIC 或一個編程為用作視頻接收器的 FPGA——它將前端視頻信號解碼為基帶視頻。該 ASIC/FPGA 的輸出通常是 BT.656 標準格式的并行端口數字視頻總線,連接到視頻編碼器進行壓縮和持續傳輸。

標識插入的設計方法

標識圖像需要在編碼操作開始之前插入到基帶視頻幀中。將靜態徽標插入視頻流有多種設計可能性,如下所示:

在視頻輸入源之后和前端接收器 IC 之前使用標準徽標插入器。

選擇一個前端視頻接收器解決方案,它可以執行將視頻解碼為 BT.656 以及插入徽標的雙重功能。

使用在基于 Arm/GPU 的處理器上運行的基于軟件的視頻編碼器系統在原始捕獲的視頻中執行徽標插入。

上述每種方法幾乎沒有缺點和限制。選項 1 需要為徽標圖像編程和配置采購和維護外部硬件。

選項 2 涉及使用領先制造商提供的支持屏幕顯示 (OSD) 的視頻前端收發器 ASIC。這些都有其自身的限制,包括徽標大小、混合能力、IC 成本以及每個視頻輸入接口對外部存儲器(如 DDR2)的要求。此外,在收發器之后,需要將數據呈現給視頻接收器,以將數據解碼為數字 BT.656 格式,以便與標準編碼器設備連接。

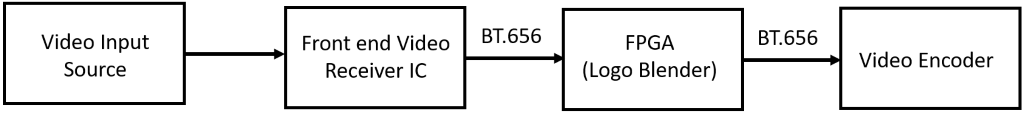

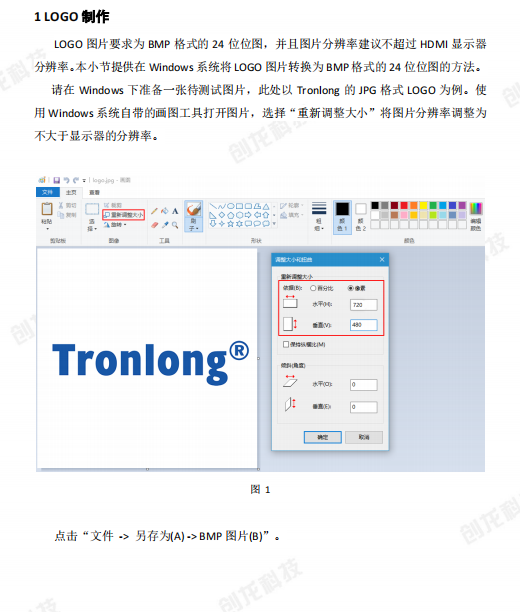

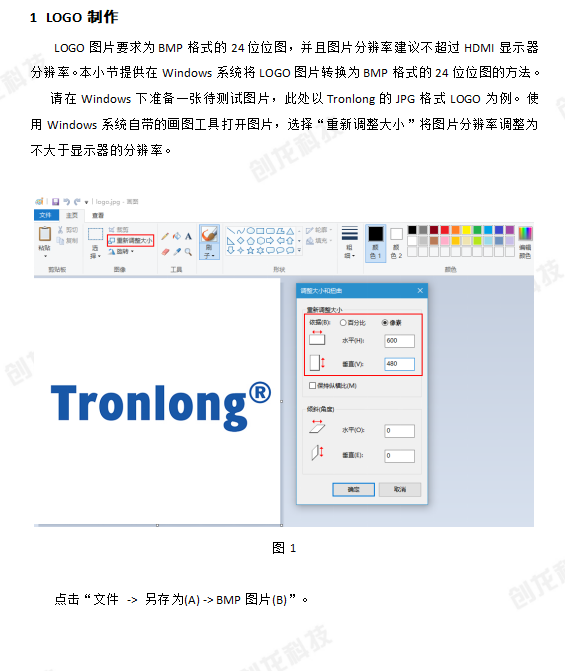

選項 3 是更好的解決方案,前提是視頻編碼器是基于軟件的,它提供了將徽標圖像混合到作為幀緩沖區存儲在 DDR 中的原始視頻像素中的可配置性。但是,如果視頻編碼器是一個沒有提供標識插入的 ASIC,那么這個選項會自動被排除,我們必須依賴選項 1 或 2。在這種情況下,要實現一個低成本的多- 輸入視頻編碼器的通道系統,在 Ittiam,我們決定使用一種創新方法,包括低成本 FPGA,在視頻前端 IC 之后和基于 ASIC 的視頻編碼器之前混合徽標圖像,如圖 2 所示。

圖 2:編碼前在數字視頻路徑中插入徽標

此選項提供了一種低成本的多通道解決方案,因為單個 FPGA 能夠對多個視頻通道執行徽標混合操作(上圖中僅顯示一個通道以進行說明)。用于存儲徽標圖像的 SPI 閃存連接到 FPGA。FPGA 可以在配置的適當位置讀取這些徽標圖像并將其與輸入基帶視頻流混合。

選擇的 FPGA 可以是低成本的,因為該設計使用 FPGA 的內部 RAM、邏輯元件和常見的 DSP 乘法器硬件塊來執行混合操作所需的像素乘法操作。

FPGA RTL IP 旨在將 SPI 閃存配置為 QSPI 模式,以滿足 FIFO 讀寫接口的數據速率要求。QSPI 接口足夠快,可以在 BT.656 像素時鐘讀取單行徽標數據之前將一行徽標寫入或緩沖到 FPGA 的 FIFO 塊中以進行混合操作(這決定了 QPSI 操作頻率在 FPGA 設計中)。透明度因子(α,或alpha)可由用戶在FPGA中配置,并且該因子可以被FPGA中實現的alpha混合算法用于執行標識插入操作。

結論在Ittiam Systems

開發的硬件設計中,上述方法已成功設計并實現了在基帶視頻中插入徽標圖像。這種設計的優點是它具有最小的延遲并降低了硬件解決方案的總體成本。

審核編輯:郭婷

-

解碼器

+關注

關注

9文章

1143瀏覽量

40721 -

編碼器

+關注

關注

45文章

3639瀏覽量

134435 -

接收器

+關注

關注

14文章

2468瀏覽量

71876

發布評論請先 登錄

相關推薦

常見的視頻接口有哪些

基帶芯片和射頻芯片的關系

卷積神經網絡在視頻處理中的應用

蘋果考慮調整iPad Logo方向

SBC3568啟動升級,靈活更換動畫logo

labview 隊列最前端插入的應用

5G射頻芯片和基帶芯片是什么關系?

基帶視頻中Logo插入的設計方法

基帶視頻中Logo插入的設計方法

評論