射頻芯片設計面臨的難題是非常多的,有設計者理論及經驗方面的主觀因素,最大的難題還是工藝及封裝的客觀限制因素。

首先說一下主觀因素吧,射頻芯片設計需要的理論知識真的是非常多,很多設計理論甚至被人認為玄乎,而且射頻芯片的設計存在各種指標的折中均衡,什么樣的折中是最佳的?怎樣折中是取決于產品的實際應用要求,沒有定論,所以經驗的積累也算是一個難題吧。再者很多射頻芯片的指標要求都是要挑戰工藝極限,這就需要很多創新性的電路結構,例如噪聲抵消啊、交調分量抵消啊、為了提高功放效率采用的動態偏置啊,有時為了降低功耗也是想盡了辦法,各種電流復用。

關鍵的還是工藝及封裝的物理限制或者模型的不準確性導致的難題。射頻芯片最重要的指標是噪聲系數和線性度,這兩個指標和工藝完全相關,例如cmos工藝襯底上就會耦合過來各種噪聲干擾,cmos器件的線性度也很差,這種難題是硬傷,沒辦法解決,只能通過合適的電路結構或者采取一些無法定量分析的隔離措施來緩解問題,這就存在很多不確定性了。

其次,射頻電路隨著頻率的升高,對寄生參數越來越敏感,大的寄生電阻、電容會使電路的性能降低到無法容忍的地步,那么如何準確的評估這些寄生參數的量就是一個極大的難題,這里面涉及到器件的精確射頻模型建模和版圖中寄生參數的精確提取。器件的射頻精確模型是業內的一大難題,頻率越高偏差會越大,還有一些器件特性難以建模,例如亞閾值區域特性,大信號條件下的高階非線性特性,各類噪聲特性的準確建模,這些模型的問題都會帶來仿真結果與實際產品之間的差異,器件模型近年來還是有了長足發展了,成熟工藝廠提供的模型在射頻頻段還是相對比較準確了,微波及毫米波頻段會差異大些。另外一個難題就是版圖寄生參數提取的準確性和電磁仿真的建模精度問題,版圖寄生參數通常只是提取寄生的電阻和耦合電容,精度也非常有限,這些寄生參數對電路的影響往往又是致命的,可能會使高頻增益嚴重降低,噪聲急劇惡化,匹配完全偏離設計,甚至帶來穩定性問題;而且工作頻率升高以后分布寄生參數對電路影響的評估變得極不準確,電磁耦合干擾的問題會很嚴重,這時就需要電磁仿真工具來進行評估了,電磁仿真嚴重依賴于晶圓上各層材料的建模,這個模型非常難建的準確,特別是襯底的模型,通常都會簡化很多因素來建立一個相對簡單實用的模型,其次電磁仿真本身就存在精度問題,這都導致了版圖對電路性能影響的評估存在偏差。

很多時候能夠通過一些手段來評估分布寄生參數或者電磁耦合對射頻芯片電路的影響,可是對電路版圖卻束手無策,沒辦法優化,或者怎么優化都沒什么本質性的改善,這才是讓人頭疼的事情。

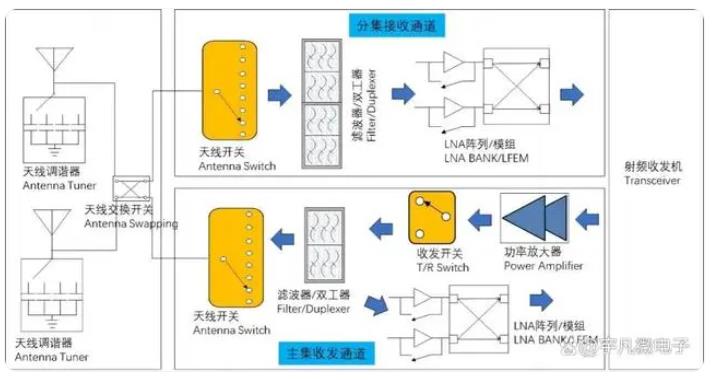

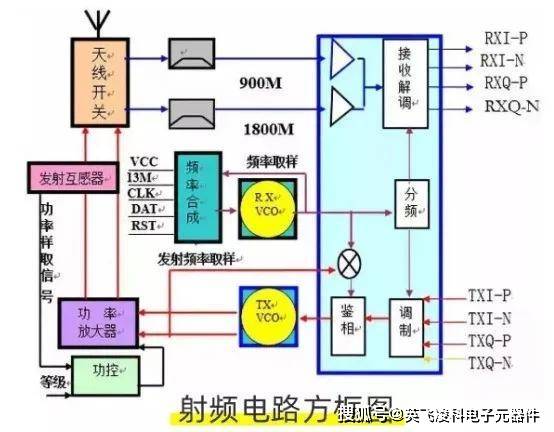

以上所說的基本都還是單個功能模塊電路在設計上會遇到的難題,到整個復雜芯片的總版圖及封裝設計階段還有很多其它難題。例如完整的transceiver包含射頻前端、鎖相環、ad采樣、發射上變頻通道及射頻功率放大器,很多部分都是數模混合電路,存在各個部分之間的相互干擾,特別是通過襯底、電源、地的干擾和電磁耦合干擾,這些因素的評估和分析真的可以上升為玄學了,通常是依賴多次的流片測試來評估了,因為基本沒辦法定量分析。還有一個難題是射頻芯片的esd設計,小小的esd二極管帶來的寄生電容也可能是致命的,太小的esd二極管又滿足不了抗靜電要求,總之就是矛盾。

射頻芯片設計完成以后的封裝影響也是一大難題,小小的一根封裝引線就是1nH以上的電感,這些電感對射頻芯片的影響實在是太大了,在成本可控的前提下盡量采用先進的封裝形式,減少封裝帶來的引線電感。

審核編輯:湯梓紅

-

射頻電路

+關注

關注

35文章

425瀏覽量

43258 -

射頻芯片

+關注

關注

976文章

411瀏覽量

79581

發布評論請先 登錄

相關推薦

射頻功放芯片選型原則

射頻芯片的工作原理和用途

基帶芯片和射頻芯片的關系

揭示射頻芯片性能測試的核心指標

1.2-1.3GHZ頻段的的VTX 射頻芯片方案

瘋狂內卷下,2024射頻芯片看這篇

射頻芯片設計難題

射頻芯片設計難題

評論