克服 5nm 節(jié)點(diǎn)以下未來(lái)晶體管技術(shù)的挑戰(zhàn)

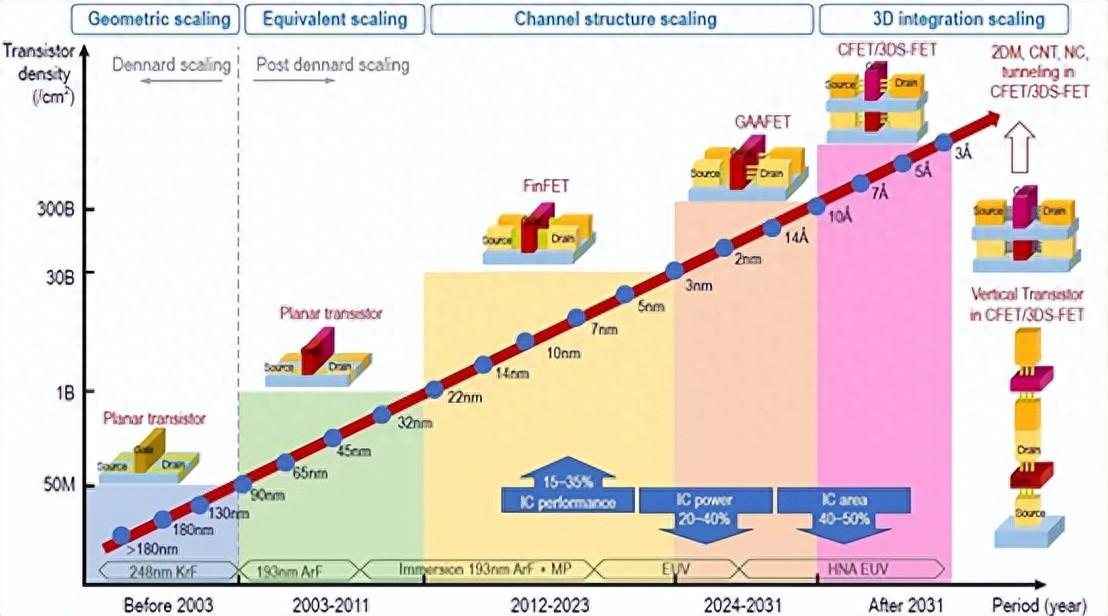

“半導(dǎo)體時(shí)代”始于 1960 年集成電路的發(fā)明。在集成電路中,所有有源-無(wú)源元件及其互連都集成在單個(gè)硅晶片上,在便攜性、功能性、功率和性能方面具有眾多優(yōu)勢(shì)。數(shù)十年來(lái),VLSI 行業(yè)一直遵循摩爾定律,即“芯片上的晶體管數(shù)量大約每?jī)赡攴环薄榱双@得縮小晶體管的好處,VLSI 行業(yè)正在不斷改進(jìn)晶體管結(jié)構(gòu)和材料、制造技術(shù)以及設(shè)計(jì) IC 的工具。迄今為止,晶體管已采用各種技術(shù),包括高 K 電介質(zhì)、金屬柵極、應(yīng)變硅、雙圖案化、從多側(cè)控制溝道、絕緣體上硅等技術(shù)。其中一些技術(shù)在“關(guān)于 CMOS、SOI 和 FinFET 技術(shù)的評(píng)論論文”中進(jìn)行了討論。 [1]

如今,物聯(lián)網(wǎng)、自動(dòng)駕駛汽車、機(jī)器學(xué)習(xí)、人工智能和互聯(lián)網(wǎng)流量的需求呈指數(shù)級(jí)增長(zhǎng),這成為將晶體管縮小到現(xiàn)有 7nm 節(jié)點(diǎn)以下以獲得更高性能的驅(qū)動(dòng)力。然而,縮小晶體管尺寸存在若干挑戰(zhàn)。

亞微米技術(shù)的問(wèn)題

每次我們縮小晶體管尺寸時(shí),都會(huì)產(chǎn)生一個(gè)新的技術(shù)節(jié)點(diǎn)。我們已經(jīng)看到了諸如 28nm、16nm 等晶體管尺寸。縮小晶體管尺寸可以實(shí)現(xiàn)更快的開關(guān)、更高的密度、低功耗、更低的每個(gè)晶體管成本以及許多其他收益。 CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)晶體管基礎(chǔ) IC 技術(shù)在 28nm 節(jié)點(diǎn)上表現(xiàn)良好。然而,如果我們將 CMOS 晶體管縮小到 28 nm 以下,短溝道效應(yīng)將變得無(wú)法控制。在該節(jié)點(diǎn)下方,由漏源電源產(chǎn)生的水平電場(chǎng)試圖控制通道。結(jié)果,柵極無(wú)法控制遠(yuǎn)離柵極的泄漏路徑。

16nm/7nm晶體管技術(shù):FinFet和FD-SOI

VLSI 行業(yè)已將 FinFET 和 SOI 晶體管用于 16nm 和 7nm 節(jié)點(diǎn),因?yàn)檫@兩種結(jié)構(gòu)都能夠防止這些節(jié)點(diǎn)的泄漏問(wèn)題。這兩種結(jié)構(gòu)的主要目標(biāo)是最大化柵極到溝道的電容并最小化漏極到溝道的電容[1]。在這兩種晶體管結(jié)構(gòu)中,都引入了溝道厚度縮放作為新的縮放參數(shù)。隨著溝道厚度的減小,沒(méi)有遠(yuǎn)離柵極區(qū)域的路徑。因此,門對(duì)通道有很好的控制,從而消除了短通道效應(yīng)。

在絕緣體上硅 (SOI) 晶體管中,使用了掩埋氧化物層,它將主體與圖 1a 所示的襯底隔離開來(lái)。由于 BOX 層,降低了漏源寄生結(jié)電容,從而加快了開關(guān)速度。 SOI 晶體管的主要挑戰(zhàn)是難以在晶圓上制造薄硅層。

碳納米管的帶隙可以通過(guò)其手性和直徑來(lái)改變,因此可以使碳納米管表現(xiàn)得像半導(dǎo)體。半導(dǎo)體 CNT 可以成為用于溝道材料的納米級(jí)晶體管器件的有利候選者,因?yàn)樗峁┝藘?yōu)于傳統(tǒng)硅 MOSFET 的眾多優(yōu)勢(shì)。碳納米管傳導(dǎo)熱量類似于鉆石或藍(lán)寶石。此外,與基于硅的設(shè)備相比,它們的切換更可靠且功耗更低。 [5]

此外,CNFETS 的跨導(dǎo)是其對(duì)應(yīng)物的四倍。 CNT 可以與 High-K 材料集成,從而對(duì)通道提供良好的柵極控制。由于遷移率增加,CNFET 的載流子速度是 MOSFET 的兩倍。 N型和P型CNFET的載流子遷移率在提供相同晶體管尺寸方面的優(yōu)勢(shì)方面是相似的。在 CMOS 中,由于遷移率值不同,PMOS(P 型金屬氧化物半導(dǎo)體)晶體管的尺寸大約是 NMOS(N 型金屬氧化物半導(dǎo)體)晶體管的 2.5 倍。

CNTFET 的制造過(guò)程是一項(xiàng)非常具有挑戰(zhàn)性的任務(wù),因?yàn)樗枰椒ǖ木群蜏?zhǔn)確性。在這里,我們討論了頂柵 CNTFET 制造方法。

該技術(shù)的第一步從將碳納米管放置到氧化硅襯底上開始。然后隔離各個(gè)管。源極和漏極觸點(diǎn)使用先進(jìn)的光刻技術(shù)進(jìn)行定義和圖案化。然后通過(guò)細(xì)化觸點(diǎn)和CNT之間的連接來(lái)降低接觸電阻。通過(guò)蒸發(fā)技術(shù)在納米管上沉積薄的頂柵電介質(zhì)。最后,為了完成該工藝,柵極觸點(diǎn)沉積在柵極電介質(zhì)上。 [6]

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27510瀏覽量

219742 -

晶體管

+關(guān)注

關(guān)注

77文章

9705瀏覽量

138470

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

IBM與Rapidus在多閾值電壓GAA晶體管技術(shù)的新突破

晶體管與場(chǎng)效應(yīng)管的區(qū)別 晶體管的封裝類型及其特點(diǎn)

雪崩晶體管的定義和工作原理

PMOS晶體管的飽和狀態(tài)

CMOS晶體管的尺寸規(guī)則

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

晶體管的主要材料有哪些

GaN晶體管的應(yīng)用場(chǎng)景有哪些

GaN晶體管和SiC晶體管有什么不同

PNP晶體管符號(hào)和結(jié)構(gòu) 晶體管測(cè)試儀電路圖

微電子所在《中國(guó)科學(xué):國(guó)家科學(xué)評(píng)論》發(fā)表關(guān)于先進(jìn)CMOS集成電路新結(jié)構(gòu)晶體管的綜述論文

臺(tái)積電擴(kuò)增3nm產(chǎn)能,部分5nm產(chǎn)能轉(zhuǎn)向該節(jié)點(diǎn)

什么是達(dá)林頓晶體管?達(dá)林頓晶體管的基本電路

克服5nm節(jié)點(diǎn)以下未來(lái)晶體管技術(shù)的挑戰(zhàn)(上)

克服5nm節(jié)點(diǎn)以下未來(lái)晶體管技術(shù)的挑戰(zhàn)(上)

評(píng)論