展會名稱: CEIA中國環渤海電子制造及智能自動化展覽會展會時間: 2014年10月22—24日展會地點: 天津濱海國際會展中心主辦單位: 中國電子學會天津經濟技術開發區管理委員會承辦單位: 天津

2014-07-30 13:19:47

中的重大價值。為順應國際工業4.0發展,實施《中國制造2025》規劃綱要及工業和信息化部智能裝備發展指導意見,順應智能化發展趨勢,進一步推動智能制造裝備在現代汽車工業中的應用,2016上海國際智能制造

2016-01-29 14:42:54

2017中國(廣州)國際機器人、智能裝備及制造技術展覽會(RoboIMEX)由中國機械工業集團有限公司主辦,中國機械國際合作有限公司、國機智能科技有限公司、中國電器科學研究院有限公司共同承辦,將于

2017-03-15 15:13:10

:中華人民共和國工業和信息化部中華人民共和國商務部支持單位:成都市人民***四川省經濟和信息化委員會四川省國防科學技術工業辦公室中國電子信息產業集團有限公司主辦單位:中國電子器材總公司承辦單位:中電會展

2018-05-21 14:23:50

`一、組織機構指導單位:中國科學技術協會 中國機械工業聯合會主辦單位: 上海市經濟和信息化委員會中國儀器儀表學會中國自動化學會《先進制造業》全媒體特別協辦單位:中國平安財產保險股份有限公司承辦單位

2018-03-15 16:52:57

2019)時間:2019年4月9日至11日地點:深圳會展中心 主題:智領新時代慧享新生活組織機構主辦單位:工業和信息化部、深圳市人民***承辦單位:中國電子器材有限公司、深圳市平板顯示行業協會協辦單位

2018-09-06 10:05:17

,隨著國家人口紅利的逐漸消退,高成本、員工難求的局面更加嚴峻,手機制造業人力資源成本變成企業主要的成本構成,降本增效成為我們成本控制的必然選擇!自動化、智能化、信息化是我們工廠未來減員增效的主要手段

2019-03-06 17:27:40

”產業發展研究報告》解析14. 金融創新助力“中國制造2025”轉型升級15. 中國制造業的智能化、信息化以及工程教育的對策六、參會范圍本屆大會擬邀請來自***相關部門,行業協會、學會、聯盟、商會,高校

2018-10-16 14:53:50

的必然選擇!自動化、智能化、信息化是我們工廠未來減員增效的主要手段,自動化生產是落腳點。打造“智能制造”,“智慧工廠”已成為眾多手機品牌企業,設計企業,加工企業的共識。“2021深圳國際手機制造自動化

2020-11-03 15:03:30

2022第六屆CMM中國電子制造自動化&資源展同期展會:東莞國際芯片及半導體產業博覽會CMM工業物聯網&工業自動化展聯系方式:***主辦單位:惠州智能終端制造協會支持單位:深圳電子

2021-11-18 15:13:56

產業發展和變革的重要方向。中國要建設制造業強國,必須要緊緊把握制造業的發展趨勢,加快智能制造的發展,促進工業向中高端邁進,這是新常態下打造新的國際競爭優勢的必然選擇。新一代信息技術和工業融合發展呈現

2016-08-15 15:23:12

產業發展和變革的重要方向。中國要建設制造業強國,必須要緊緊把握制造業的發展趨勢,加快智能制造的發展,促進工業向中高端邁進,這是新常態下打造新的國際競爭優勢的必然選擇。新一代信息技術和工業融合發展呈現

2016-08-25 11:46:58

裝備制造業提供了綠色轉型的方向。強調“綠色”意在提升能源、原材料的利用效率,最大限度地實現涵蓋全球工業范圍的可持續發展;而強調“智能”則意在提升生產效率、提高工業資源調配的合理性,以及工業設備的可用性

2014-01-15 16:14:50

工業和信息化部指導下,決定組織“工業和信息化數字中國專題館”,展品涵蓋通訊、互聯網、物聯網、云計算、大數據、車聯網、人工智能等技術及相關成果。工業和信息化數字中國專題館參展范圍 展品涵蓋數字中國涉及

2018-09-07 09:19:08

第七屆中國電子信息博覽會(CITE 2019)時間:2019年4月9日至11日地點:深圳會展中心主題:智領新時代慧享新生活組織機構主辦單位:工業和信息化部、深圳市人民***承辦單位:中國

2018-11-21 11:47:35

在“中國制造 2025 ”“工業 4.0 ”的大背景下產生了數字化轉型,當前來看還是很多企業停留在工業 2.0 (電氣化)的狀態,當企業發展到一定規模的時候,會遇到瓶頸:如具體是人員管理復雜、生產

2021-08-19 15:53:57

互聯網”,我國叫“中國制造2025”,這三者本質內容是一致的,都指向一個核心,就是智能制造。 2015年中國有幾個概念非常火,第一是大眾創業、萬眾創新,第二就是工業4.0,第三個就是“互聯網

2016-03-07 15:39:00

時間和地點會議時間:2015年5月7-8日會議地點:中國·上海綠地會議中心二、組織機構指導機構:國家信息化專家咨詢委員會、中國機械工業聯合會主辦機構:《先進制造業》全媒體協辦單位:機械科學研究總院先進制造

2015-03-25 10:22:00

的無憂環境。工業大數據是指制造企業在生產運輸銷售過程中所產生的各種數據,包括企業生產鏈的各個環節以及工業傳感器,自動控制系統,物聯網等等。其實,相比較國外而言,我國制造業的信息化水平還是比較落后

2016-06-19 17:43:37

投重振制造業。 韓國,2014年提出“制造界創新3.0策略”,協助中小企業建立智慧化與優化稱產程序。 中國大陸,2015年宣布“中國制造2025”,力曾從制造大國邁入制造強國

2018-02-28 10:41:52

和高效的獲取銷售線索,推廣新產品,樹立品牌形象進一步增強市場競爭優勢。【組織機構ARE ShenZhen 2016】指導單位: 中華人民共和國工業和信息化部廣東省經濟和信息化委員會主辦單位: 深圳自動化

2016-05-25 09:01:48

,AI專家則大談智能制造中的AI賦能。閱讀國外的文章,西方企業從全球化帶來的壓力出發,討論如何通過智能制造實現...

2021-07-19 07:56:15

`說起智能制造,大家應該不會陌生。近年來隨著國家由上至下的扶持和推進,國內大范圍地出現了“智造熱潮”。機器換人、全自動化、信息追蹤等與智能制造相關的嘗試層出不窮,重新點燃了工業升級革命的熱情。盡管

2018-09-26 17:12:52

智能制造與工業物聯網有什么關系?智能工廠對工業物聯網有哪些要求?

2021-06-17 08:32:50

`智能制造是什么當前,全球制造業正加快邁向數字化、智能化時代,智能制造對制造業競爭力的影響越來越大。智能制造就是面向產品全生命周期,實現泛在感知條件下的信息化制造。智能制造技術是在現代傳感技術

2018-11-15 10:50:32

,我們具備一定基礎優勢。我國工業化和信息化深度融合已推行多年,信息技術廣泛應用于制造業設計、生產等全流程,數字化工具、數控裝備等市場普及率迅速擴大,有效提高了我國制造業的自動化和智能化水平。我國還在物

2015-11-17 16:10:21

,信息系統不僅具有強大感知、計算分析與控制能力,更具有學習提升、產生知識的能力。新一代智能制造進一步突出了人的中心地位,是統籌協調人、信息系統和物理系統的綜合集成大系統。圖4新一代智能制造的系統集成 中國

2020-04-26 07:55:03

互聯網+制造”就是工業4.0。“工業4.0”是德國推出的概念,美國叫“工業互聯網”,中國叫“中國制造2025”,這三者本質內容是一致的,都指向一個核心,就是智能制造。 2015年中幾個概念非常

2015-11-18 13:33:32

電子制造企業也在尋求智能制造轉型道路上突破。事實證明,答案己逐步顯現:通過信息化與工業化的融合,優化生產過程,從而實現降低人員配置,提高生產效率,擴大利潤空間。 IMS是一款真正貼近電子制造企業從

2013-08-07 09:50:23

基于“中國制造2025”,業界已加大投入發展先進制造業,以實現互聯網、大數據、人工智能和實體經濟的進一步融合,并建立世界級先進的制造業集群,推動國家產業邁向全球價值鏈的中高端。作為電子元器件與開發

2018-09-05 10:53:24

、科技和工農業生產等各個領域。以微機電系統技術為基礎的智能傳感器代表了傳感器的主要發展方向,其技術的進步不僅可以提高產品智能化水平,還可推動中國制造向中國智造的發展。

2020-08-18 06:31:31

智能工廠作為工業智能化發展的重要實踐模式,已經引發行業的廣泛關注。到底什么是智能工廠?智能工廠的核心架構是怎樣的?能為企業的轉型提供哪些支撐?這都是企業比較關心的話題。智能工廠、數字化工廠與智能制造

2019-01-09 15:46:25

。 智能工廠產業鏈分析 (一)上游行業--傳感器 不管“工業4.0”還是“中國制造2025”,其實最本質的變化是智能化生產,而在谷榮祥看來,傳感器是整個智能化的關鍵。因為“工業4.0”和“中國

2016-01-12 11:44:11

1 物流信息化的新特點1.1整合成為物流信息化的熱點根據哈佛大學教授查理*諾蘭的模型--企業信息化的六個階段,企業信息化在經過了初期的建設后會進入一個以整合為特點的階段,信息技術的單點應用要整合

2019-07-15 08:29:46

射頻識別(RFID)技術是21世紀最具變革力與核心價值的一項新技術,得到各國***普遍關注。作為中國信息化建設的起步工程之一,金卡工程在實施14年來取得的顯著成效為RFID的信息化應用奠定了

2019-10-15 07:18:46

智能制造是工業自動化與信息化技術的融合,可提升工廠的生產靈活性,可節約能源、保護環境、降低成本、提高人身安全,從而使工廠的生產效率和產品質量得到大幅度優化。 在工業生產制造過程中,工廠需要

2020-12-02 11:53:52

通過互聯網來為消費者提供差異化的產品和服務。《中國制造2025》更多的是把德國工業4.0和美國工業互聯網的特點融合起來了,既強調了在工廠端的自動化和企業管理能力的提升,又強調了要通過互聯網來為消費者

2016-06-04 11:20:42

,工業和信息化部軟件與集成電路促進中心和中國產業互聯網發展聯盟聯合舉辦首屆全國智能制造創新創業大賽。希望通過本次大賽,集合創新人才的智慧,挖掘一批有投資前景、有創新潛力,可以促進傳統產業轉型升級的創新性

2016-09-28 11:40:32

國情的信息化、智能化發展之路,他山之石可以攻玉。通過對工業4.0、工業物聯網的深度解讀結合中國企業本土的國情,打造一個適合中國智能制造的新思維模式歡迎掃描以下二維碼,現場與演講嘉賓互動提問 `

2016-03-03 01:37:17

一些方向,信息技術的深度利用非常關鍵! 東莞的大朗鎮是中國乃至整個世界聞名的傳統紡織重鎮,兩年前,這里的紡織企業從半自動化全面進入智能制造時代,一家工廠里,1個工人可以同時管48臺機器,最原始的生產

2017-02-23 15:53:08

發展新一 代信息技術,機器人等領域,智能制造成為中國制造的主攻方向。工業互聯網是通向智能制造的必要過程,工業互聯網把無數臺機器、設備、機組和工作站連接在一 起,設備自動化是實現互聯的基礎。 那么互聯網將怎樣

2016-02-25 20:35:16

,工業和信息化部軟件與集成電路促進中心科技發展處處長、中國產業互聯網發展聯盟常務副秘書長杜嬌,安徽省馬鞍山市人民***副秘書長商成勇,中國產業互聯網發展聯盟副秘書長周銳,馬鞍山經濟技術開發區王宏書記等

2016-10-31 16:24:55

全國智能制造(中國制造2025)創新創業大賽華北賽區決賽完美收官2016年11月18日,全國智能制造(中國制造2025)創新創業大賽(cism.gizwits.com)華北賽區決賽在北京圓滿舉辦

2016-11-23 10:01:34

`2016年11月25日,由廣東省民營企業合作交流協會、天英匯、機智云、中國電子工業科學技術交流中心聯合承辦的全國智能制造(中國制造2025)創新創業大賽(http

2016-11-28 14:29:49

商品滲透到垂直的電子供應鏈行業,再加上資本的入場,電子行業面臨非常重要的發展契機。平臺需發揮產業互聯網的特性,加強信息化改造和技術投入,從電子產品的生產制造端做一些根本性的改變。秉承著“為電子產業增效

2022-10-28 16:53:58

更高的自動化和信息化程度。研究應用RFID技術,探索重組企業信息流,更大限度地發揮我國制造業現有資源優勢,推動企業技術進步及傳統制造業的升級換代的可行方案與模式,已成為當務之急。而將RFID技術融入MES系統之中,必定是促進傳統制造業發展升級的眾多途徑之一。

2019-08-08 07:24:24

現代科學技術,加強信息化管理,是提高高校管理水平和效率的有效手段。射頻識別技術具有廣闊的應用前景,在高校的信息化管理中將發揮重要的作用。

2019-07-23 07:32:46

、技術水平很高。沒有‘內行’的直接參與,僅僅依靠軟件人員是寫不出工業軟件的。”周宏仁指出。 促進前沿科學成果信息化轉變 在近日召開的兩化融合高層研討會上,周宏仁提到了令與會代表頗具新鮮感的詞語“先進制造

2012-12-14 09:58:10

的重要技術代表,在汽車制造場景中應用廣泛。整體思路為:通過適度改進系統結構,提升各部件間耦合性,降低接口設計量,從而增加在控制上的邏輯連續性。汽車制造中的基層自動化技術,實現了工業組態、數據庫及通信

2018-02-28 09:18:44

的電子信息技術應用早已成為現實。汽車電子的發展,自然帶動了電子制造設備的發展。在2011年5月11日至13日于上海光大會展中心所舉行的第二十一屆中國國際電子生產設備暨微電子工業展(NEPCON China

2011-01-24 13:39:57

通信等不斷融入到工業生產的各個環節,大幅提高制造效率,改善產品質量,降低產品成本和資源消耗,將傳統工業提升到智能化的新階段。總的來說,智能工業的實現是基于物聯網技術的滲透和應用,并與未來先進制造技術

2014-07-23 07:41:30

軟件到平臺等智能制造等各個環節中的先進設備與智能制造解決方案。通過對包括自動化設備、機器人與自動化、生產信息化技術、工廠物流技術、工裝夾具等工業互聯產業生態前沿技術及智能解決方案的展示,探討智能工廠

2018-09-25 09:32:47

讀寫、信息處理、數據交換、決策優化的能力。是其工業體系從信息化、數據化、自動化到智能化發展歷程的延續和漸進式創新的升級,通過上述要素的連接,持續推動管理和生產過程的智能化,將分布式的制造企業和客戶進行

2015-12-29 16:04:58

、惠民生的重要引擎,是實現中國制造2025的重要抓手,制造業是國民經濟的主體,也是“雙創”的主戰場,工信部信息化和軟件服務業司將繼續加速制造業“雙創”平臺建設,推動產業轉型升級。李穎巡視員充分肯定大賽篩選

2017-12-12 11:01:42

廣闊的應用市場。《中國制造2025》明確提出新能源汽車和智能汽車產業發展的戰略目標,到2025年,與國際先進水平同步的新能源汽車年銷量300萬輛,在國內市場占80%以上,并逐步實現車輛信息化、智能化

2018-10-11 09:08:52

***指導,并由東莞市科學技術協會和國際智能制造產業聯盟聯合主辦,因此大會在東莞引起了廣泛的關注,被東莞日報、東莞陽光網等東莞主流媒體多次報導。★由人民日報社《中國經濟周刊》、中國經濟研究院、廣東省

2016-11-01 18:15:25

的創業項目和創新產品應用,打造推動經濟發展和轉型升級的強勁引擎,推動智能制造產業快速發展,助力“中國制造2025”新進程。大賽由工業和信息化部軟件與集成電路促進中心(CSIP)、中國產業互聯網發展聯盟

2017-11-01 15:29:29

的創業項目和創新產品應用,打造推動經濟發展和轉型升級的強勁引擎,推動智能制造產業快速發展,助力“中國制造2025”新進程。大賽由工業和信息化部軟件與集成電路促進中心(CSIP)、中國產業互聯網發展聯盟

2017-11-03 12:26:18

。從中央到地方,產業智能化的創新與發展正在掀起新的一輪熱潮。作為國內最權威的智能制造雙創賽事,第二屆全國智能制造(中國制造2025)創新創業大賽今年將首次舉辦產業智能化創新發展論壇,這也是十九大以后

2017-11-15 10:33:36

國際中小企業博覽會智能制造與裝備展由工業和信息化部、國家工商行政管理總局、廣東省人民***主辦,國際智能制造產業聯盟應邀參與本屆展會,并牽頭組辦“東莞組團“。展覽面積達2萬平方,預計將吸引全球21個國家和地區

2015-09-16 17:08:43

信息物理系統(CPS)為基礎,以生產高度數字化、網絡化、機器自組織為標志的第四次工業革命。《中國制造2025》被視為“用3個10年完成中國從制造業大國向制造業強國轉變”的第一個10年路線圖,很多內容

2016-03-21 18:07:45

信息物理系統(CPS)為基礎,以生產高度數字化、網絡化、機器自組織為標志的第四次工業革命。《中國制造2025》被視為“用3個10年完成中國從制造業大國向制造業強國轉變”的第一個10年路線圖,很多內容

2016-04-26 16:46:41

工業革命后,人類將迎來以信息物理系統(CPS)為基礎,以生產高度數字化、網絡化、機器自組織為標志的第四次工業革命。《中國制造2025》被視為“用3個10年完成中國從制造業大國向制造業強國轉變”的第一個

2017-06-15 10:40:15

活動背景從我國提出《中國制造2025》規劃,把智能制造作為兩化深度融合的主攻方向,轉型為高端制造業國家。在物聯網技術的發展帶來了機遇和挑戰下,傳統制造業面臨著產業升級的歷史機遇的同時,也面臨資本貿易

2019-11-14 16:19:02

`在剛剛結束的2017中國產業互聯與數字經濟大會上,機智云智能硬件自助開發平臺 入選工信部信息化與軟件服務業司 2017年度中國產業互聯網集成服務優秀解決方案。 為貫徹落實《中國制造2025

2017-12-15 10:28:43

一直位列第一,且在智能制造領域的探索和實踐走在國內前沿。合川作為重慶的城市發展新區,是工業化的主戰場。隨后工業和信息化部軟件與集成電路促進中心處長中國產業互聯網發展聯盟常務副秘書長杜嬌介紹大賽的賽制

2016-10-27 19:52:49

智能制造獨角獸。大賽簡介本次大賽由工業和信息化部軟件與集成電路促進中心和中國產業互聯網發展聯盟聯合主辦,機智云和中國電子工業科學技術交流中心聯合承辦,覆蓋全國核心城市,聯合地方***資源,集合產業鏈

2016-10-18 15:38:07

創業大賽的重要意義,并表示能通過此次比賽匯聚資源、挑選落地項目,將助力區域經濟的快速發展。工業和信息化部軟件與集成電路促進中心副主任曲大偉也對推動智能制造領域科技成果的轉化發出號召,希望大家齊心協力打造

2016-10-18 16:37:01

2025》,把發展智能制造作為主攻方向。擴大試點示范城市(群)覆蓋面,選擇20至30個基礎條件好、示范帶動作用強的城市(群),繼續開展中國制造2025試點示范創建工作,以試點示范推進《中國制造2025》深入實施。面對國際產業競爭形勢、國內

2017-09-19 14:58:34 51

51 “中國制造2025”將是中國工業未來10年的發展綱領、頂層設計。政府的諸多行動向市場傳遞出強烈信號,顯示工業轉型將迎來大突破、大提速。

2017-12-25 10:04:19 66537

66537 “中國制造2025”將是中國工業未來10年的發展綱領、頂層設計。政府的諸多行動向市場傳遞出強烈信號,顯示工業轉型將迎來大突破、大提速。工信部曾表示,計劃大體分三步、用三個十年左右時間實現制造業大國向制造業強國的轉變

2018-01-04 14:48:01 31332

31332

智能制造,隨著工業4.0、中國制造2025等國家戰略而名聲大振。智能制造,離不開對各式各樣的智能系統的構建,從智能產品到智能產線,從智能物流到智能服務,從智能組織到智能企業。在需求與政策的雙輪驅動

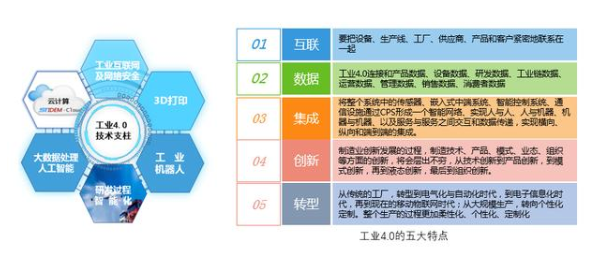

2018-01-19 09:39:35 1036

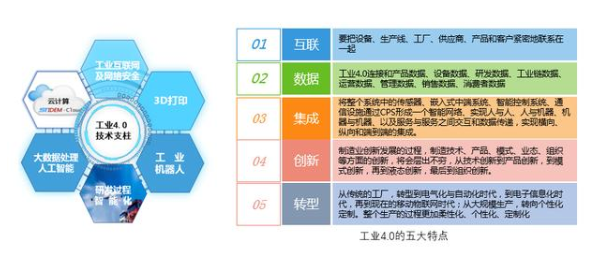

1036 工業4.0的核心是智能制造,而非工業4.0是智能制造,需要實現工業4.0,中國企業首先需要實現制造的自動化、智能化,最后才能談工業4.0的實現。

2018-02-07 09:49:23 10934

10934

中國秉承開放發展、合作共贏的理念,提出“中國制造2025”,這是公開透明的,目的是為推動中國制造業升級提供戰略指引和信息指導。

“中國制造2025”也是開放、非歧視的,相關政策措施適用于中國境內所有企業,中資企業、外資企業都可以參加,當然也包括美資企業。

2018-04-12 08:24:00 7249

7249 5月9日,由中國工程院、工業和信息化部、中國科學技術協會共同主辦的“2018智能制造國際會議”在北京召開。工業和信息化部部長苗圩出席并作主旨報告。

2018-05-12 09:49:09 3947

3947 《中國制造2025》的出臺,為多個行業帶來新一輪市場投資。其中,涉及智能制造的工業自動控制裝置、工業機器人、智能化成套裝備、智能終端產品前景更好。

2018-05-17 17:47:00 3640

3640 加快推進智能制造,是實施《中國制造 2025》的主攻方向,是落實工業化和信息化深度融合、打造制造強國的戰略舉措,更是我國制造業緊跟世界發展趨勢、實現轉型升級的關鍵所在。 行業痛點 實施智能制造,重點

2018-06-14 09:50:00 774

774 為落實《中國制造2025》總體部署,按照《智能制造發展規劃(2016-2020年)》《智能制造工程實施指南(2016-2020年)》的要求,工業和信息化部現開展2018年智能制造試點示范項目推薦工作。

2018-07-17 11:15:00 2161

2161 為落實《中國制造2025》總體部署,按照《智能制造發展規劃(2016-2020年)》《智能制造工程實施指南(2016-2020年)》的要求,工業和信息化部現開展2018年智能制造試點示范項目推薦工作。

2018-07-25 10:58:40 6505

6505 為落實《中國制造2025》總體部署,按照《智能制造發展規劃(2016-2020年)》《智能制造工程實施指南(2016-2020年)》的要求,工業和信息化部現開展2018年智能制造試點示范項目推薦工作。

2018-09-07 16:48:50 1862

1862 隨著信息化時代的迅猛發展,“中國制造2025”戰略的持續推進,以信息化、工業化深度融合為方向的科技革命正式拉開帷幕,智能化轉型成為各行業主攻方向之一。

2018-09-25 17:00:37 2161

2161 德國的工業4.0和中國的智能制造2025想必大家一定有所耳聞,但一直也是停留在概念的層面,說起來朗朗上口卻沒有人真的好好解釋過其中的真正內涵。小編就結合自己所看過的資料,為大家整理一下有關說明。為大家今后的產業布局提供理論基礎。

2018-10-24 11:12:01 19162

19162 為全面反映產業運行態勢,進一步推動電子信息制造業向高質量發展,工業和信息化部組織研究形成了《中國電子信息制造業綜合發展指數研究報告(2018年第2屆)》。

2018-12-02 09:14:26 3972

3972

自2015年“中國制造2025”正式實施以來,國內的制造業開始加大信息化建設力度,而科技技術作為第一生產力,在推動中國制造立足于世界一流行列具有決定性的作用。這幾年來,作為信息化技術之一的VR虛擬現實技術表現出巨大的潛力,對制造業實現高度信息化的價值也逐漸顯示出來。

2018-12-12 13:56:49 4701

4701 為落實《中國制造2025》總體部署,按照《智能制造發展規劃(2016-2020年)》《智能制造工程實施指南(2016-2020年)》的要求,工業和信息化部開展了智能制造試點示范項目推薦工作。下面根據

2019-01-27 07:42:00 5405

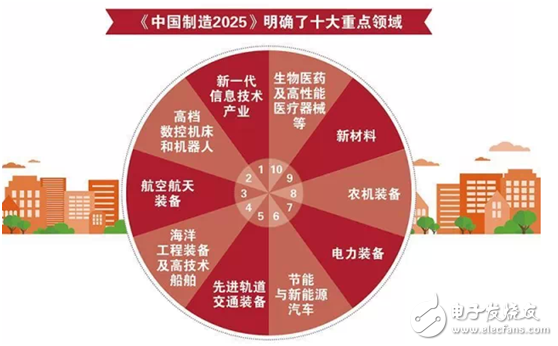

5405 本文對《中國制造2025》進行了介紹。

2019-08-05 16:51:05 9364

9364 MES智能制造作用有哪些?MES系統是一套面向制造企業執行層的生產信息化管理系統。MES可以為企業提供制造數據管理、計劃排程管理、生產調度管理、庫存管理等。那MES在智能制造中的作用有哪些呢?

2019-10-31 16:50:47 5317

5317 《中國制造2025》的出臺,為多個行業帶來新一輪市場投資。其中,涉及智能制造的工業自動控制裝置、工業機器人、智能化成套裝備、智能終端產品前景更好。

2019-12-14 11:31:53 1673

1673 2015年5月,國務院正式印發《中國制造2025》,部署全面推進實施制造強國戰略,中國制造2025核心和實質就是我們通常提到的“兩化融合”:以信息化帶動工業化、以工業化促進信息化,走新型工業化道路。

2020-01-23 14:46:00 5255

5255

隨著信息技術的不斷發展,智能制造這一概念迅速深入到生產制造領域。當前制造業的轉型可以看作是自動化升級和信息技術升級的融合,而其中PLM,即產品生命周期管理的應用是其不可缺少的技術核心,并在工業智能制造中發揮著重要作用。

2020-10-18 11:24:58 3260

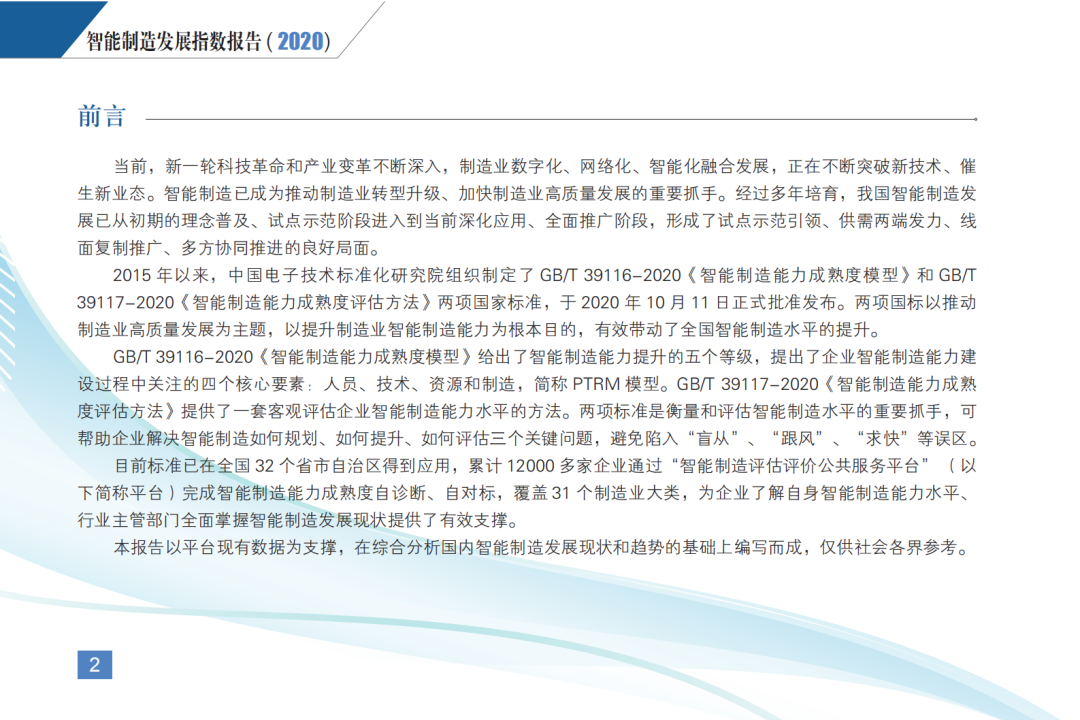

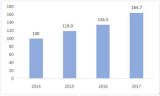

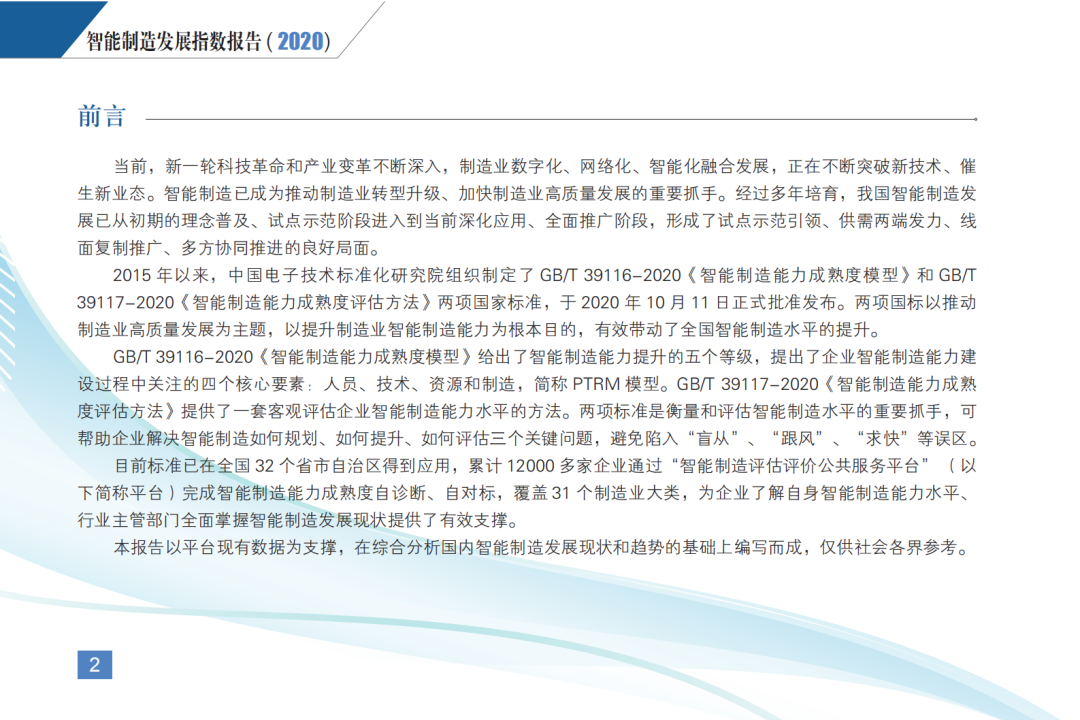

3260 ? ? 1月21日,工信部網站發布了《智能制造發展指數報告(2020)》。 ? 2020年10月,《智能制造能力成熟度模型》和《智能制造能力成熟度評估方法》兩項國家標準發布。工業和信息化部組織中國

2021-02-05 13:40:38 2182

2182

目前,我國尚處于“工業2.0”(電氣化)的后期階段,“工業3.0”(信息化)還有待進一步普及,“工業4.0”(智能化)正在嘗試盡可能做一些示范,制造的自動化和信息化正在逐步布局,較世界發達國家有一定

2021-03-05 11:21:32 1680

1680

電子發燒友App

電子發燒友App

評論