在FPGA開發(fā)中,我們經(jīng)常遇到因為管腳忘記約束,導(dǎo)致最后生成bit的時候報錯。

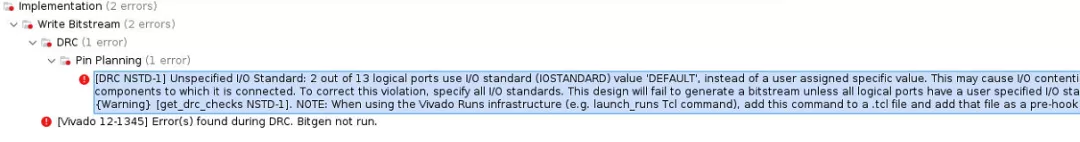

1.管腳電平未約束

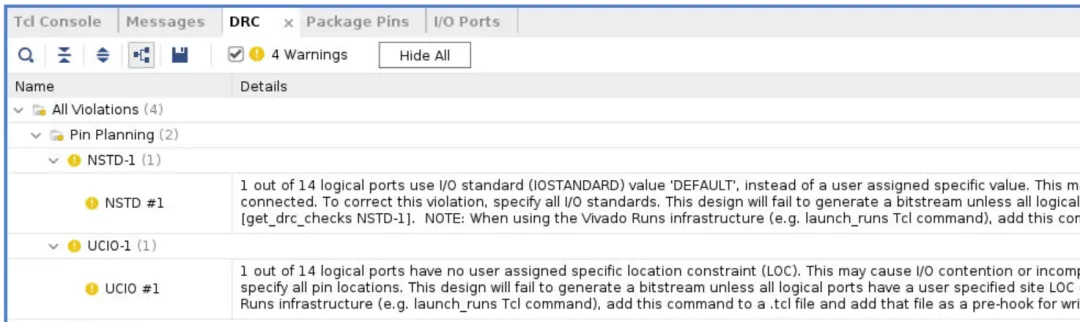

像上面這個圖中,由于在約束中忘記指定mdc和mdio的電平,再經(jīng)過了長時間的綜合和實現(xiàn)后,最后的Generate Bitstream報錯了。

這種情況下,如何才能不重新Implementation的情況下生成bit呢?

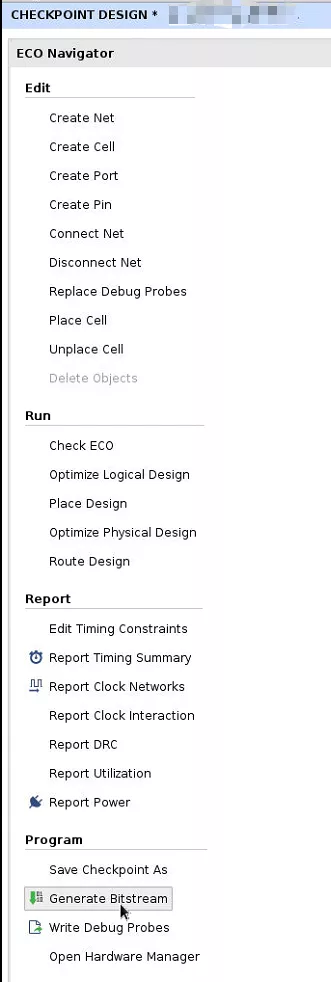

打開實現(xiàn)后的routed.dcp文件:

open_checkpoint ./Work/eth_demo.runs/impl_1/top_routed.dcp

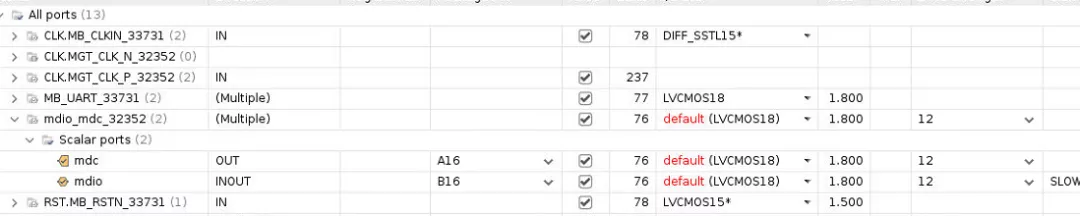

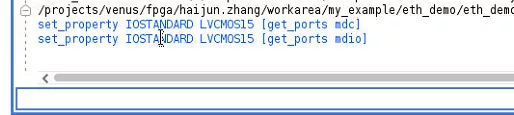

然后通過下面指令設(shè)置這兩個管腳的電平:

set_property IOSTANDARD LVCMOS15 [get_ports mdc] set_property IOSTANDARD LVCMOS15 [get_ports mdio]

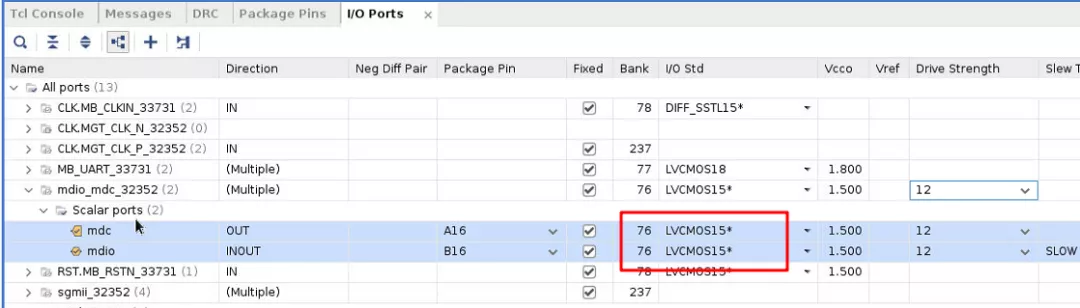

設(shè)置完成后,可以在I/O Ports窗口中看到這兩個管腳的電平已經(jīng)改了過來

然后再點左側(cè)的生成bit:

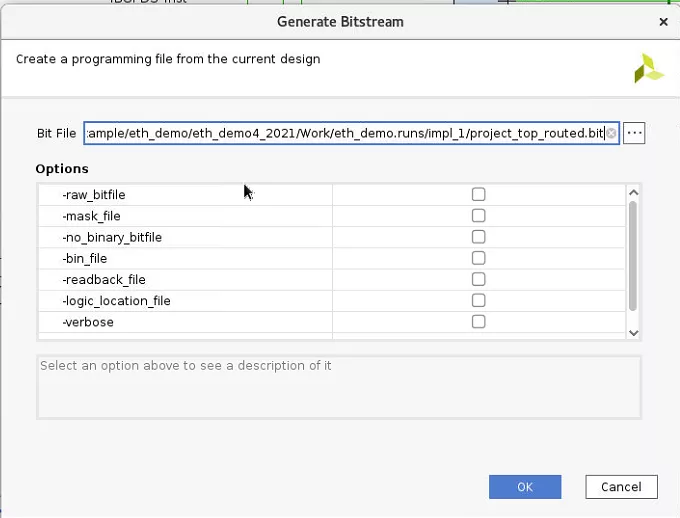

提示生成文件的位置和名字:

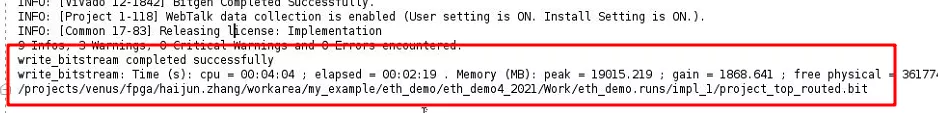

在正確生成后,可以看到tcl中提示write_bitstream completed successfully:

管腳電平修改后由于跟布局布線都沒有關(guān)系,因此直接生成bit是可以的。

2.管腳位置未約束

如果是管腳位置未約束,那我們就不能在dcp中修改位置然后直接生成bit了,因為位置變了,布局布線也需要改變。如果這個管腳的功能的需要的,那我們只能重新Implementation,如果這個管腳功能是不需要的,

那如果這個管腳的功能我們可以先不用,就想把經(jīng)過了長時間的Synthsis和Implentation后的工程生成bit文件。

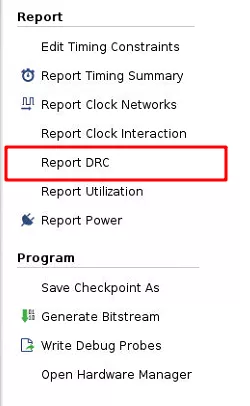

還是像上面一樣,打開route.dcp文件,然后點擊坐標(biāo)的Report DRC

可以看到有兩個問題,一個是NSTD-1,一個是UCIO-1

我們只需要把這兩個DRC的問題設(shè)成warning,不讓工具在生成bit的時候報錯,也是可以生成bit的。執(zhí)行tcl腳本如下:

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

然后再Generate Bitstream。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1630文章

21781瀏覽量

604936 -

電平

+關(guān)注

關(guān)注

5文章

361瀏覽量

39961 -

管腳

+關(guān)注

關(guān)注

1文章

228瀏覽量

32078

發(fā)布評論請先 登錄

相關(guān)推薦

ADC128S022的驅(qū)動架構(gòu)參考 ti-adc128s052.c,要如何做移位生成12bit結(jié)果呢?

C# 調(diào)用2020版本Labview生成的.NET指令集報錯,2018不報錯

ESP32-C3私有服務(wù)的UUID設(shè)置為128bit UUID會報錯怎么解決?

在不重新安裝Vivado的情況下,是否能夠安裝線纜驅(qū)動器?

時序約束實操

在keil5下定義64bit編譯報錯的原因?

Efinity Interface Designer報錯案例-v2

管腳約束問題導(dǎo)致生成bit時報錯 如何在不重新Implentation情況下生成bit?

管腳約束問題導(dǎo)致生成bit時報錯 如何在不重新Implentation情況下生成bit?

評論