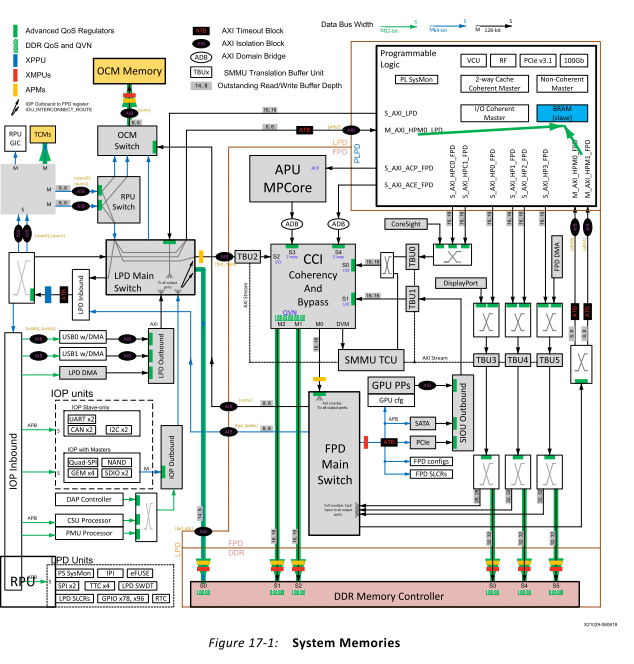

MPSoC的DDR控制器的數(shù)據(jù)通道上集成了 AXI performance monitors (APM)。具體情況,可以參考Xilinx UG1085 (v2.2)中Chapter 15的“Figure 15‐1: PS Interconnect”或者Figure 17-1。

1. APM驅(qū)動程序

對于AXI performance monitors (APM),xilinx提供的驅(qū)動程序是drivers\uio\uio_xilinx_apm.c,相關(guān)匹配字符串和主要數(shù)據(jù)結(jié)構(gòu)如下:

static const struct of_device_id xapm_of_match[] = { { .compatible = "xlnx,axi-perf-monitor", }, { /* end of table*/ } }; MODULE_DEVICE_TABLE(of, xapm_of_match); static struct platform_driver xapm_driver = { .driver = { .name = "xilinx-axipmon", .of_match_table = xapm_of_match, .pm = &xapm_dev_pm_ops, }, .probe = xapm_probe, .remove = xapm_remove, };

APM驅(qū)動程序最終會注冊UIO設(shè)備。

在每個單板的device tree里,會支持DDR的APM。比如,在VCU TRD里,為DDR的APM定義了下面字段。

perf-monitor@fd0b0000 {

compatible = "xlnx,axi-perf-monitor";

reg = <0x00 0xfd0b0000 0x00 0x10000> ;

interrupts = <0x00 0x7b 0x04> ;

interrupt-parent = <0x04> ;

xlnx,enable-profile = <0x00> ;

xlnx,enable-trace = <0x00> ;

xlnx,num-monitor-slots = <0x06> ;

xlnx,enable-event-count = <0x01> ;

xlnx,enable-event-log = <0x00> ;

xlnx,have-sampled-metric-cnt = <0x01> ;

xlnx,num-of-counters = <0x0a> ;

xlnx,metric-count-width = <0x20> ;

xlnx,metrics-sample-count-width = <0x20> ;

xlnx,global-count-width = <0x20> ;

xlnx,metric-count-scale = <0x01> ;

clocks = <0x03 0x1c> ;

phandle = <0x9b> ;

};

perf_monitor_ddr = "/amba/perf-monitor@fd0b0000";

OCM、CCI等模塊也有APM。

perf_monitor_ocm = "/amba/perf-monitor@ffa00000";

perf_monitor_cci = "/amba/perf-monitor@fd490000";

perf_monitor_lpd = "/amba/perf-monitor@ffa10000";

單板Linux啟動后,能查詢到對應(yīng)的UIO設(shè)備。

root@vcu_trd:~# ls /dev/uio* /dev/uio0 /dev/uio1 /dev/uio2 /dev/uio3 /dev/uio4

2. APM用戶態(tài)程序

對于AXI performance monitors (APM),xilinx也提供了用戶態(tài)程序,是apm_main.elf。使用apm_main.elf,可以查詢APM監(jiān)視到的DDR帶寬利用情況。

root@vcu_trd:~# chmod +x apm_main.elf root@vcu_trd:~# ./apm_main.elf -d /dev/uio0 AXI PMON is in Advanced Mode port 1 read: 0 0.00 MBps port 1 write: 0 0.00 MBps port 2 read: 0 0.00 MBps port 2 write: 0 0.00 MBps port 4 read: 0 0.00 MBps port 4 write: 0 0.00 MBps port 5 read: 0 0.00 MBps port 5 write: 0 0.00 MBps root@vcu_trd:~# root@vcu_trd:~# ./apm_main.elf -d /dev/uio1 AXI PMON is in Advanced Mode port 1 read: 12523440 12.52 MBps port 1 write: 7564856 7.56 MBps port 2 read: 13290992 13.29 MBps port 2 write: 7493209 7.49 MBps port 4 read: 0 0.00 MBps port 4 write: 331253760 331.25 MBps port 5 read: 667254864 667.25 MBps port 5 write: 320656878 320.66 MBps root@vcu_trd:~# ./apm_main.elf -d /dev/uio2 AXI PMON is in Advanced Mode port 1 read: 0 0.00 MBps port 1 write: 0 0.00 MBps port 2 read: 0 0.00 MBps port 2 write: 0 0.00 MBps port 4 read: 0 0.00 MBps port 4 write: 0 0.00 MBps port 5 read: 0 0.00 MBps port 5 write: 0 0.00 MBps root@vcu_trd:~# ./apm_main.elf -d /dev/uio3 AXI PMON is in Advanced Mode port 1 read: 0 0.00 MBps port 1 write: 0 0.00 MBps port 2 read: 0 0.00 MBps port 2 write: 0 0.00 MBps port 4 read: 0 0.00 MBps port 4 write: 0 0.00 MBps port 5 read: 0 0.00 MBps port 5 write: 0 0.00 MBps

上述設(shè)備“/dev/uio1”代表DDR APM1。在使用VCU TRD進(jìn)行1080p編碼時,port 4寫帶寬331.25 MBps,port 5讀帶寬667.25 MBps,port 5寫帶寬320.66 MBps。每個DDR port對應(yīng)的硬件模塊,請參考ug1085的Figure 17-1。port 4連接到了HP 1/HP 2。port 5連接到了HP 3。

-

APM

+關(guān)注

關(guān)注

1文章

72瀏覽量

13336 -

MPSoC

+關(guān)注

關(guān)注

0文章

200瀏覽量

24645 -

AXI

+關(guān)注

關(guān)注

1文章

134瀏覽量

17133

發(fā)布評論請先 登錄

使用AXI-Full接口的IP進(jìn)行DDR的讀寫測試

Zynq MPSoC系列器件的AXI總線介紹

Designing High-Performance Video Systems with the AXI Interconnect

如何實現(xiàn)從microblaze端訪問ARM DDR?

AXI流量生成器不會驅(qū)動QoS線路怎么辦

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

一文詳解MPSoC芯片

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

XILINX MPSOC系列FPGA視頻教程

Arm AMBA協(xié)議集中AHB與AXI相比訪問DDR效率帶寬會差很大

Arm中AHB與AXI相比訪問DDR效率帶寬會差很大

如何調(diào)試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

更新的AXI performance monitors(APM)測試工具

AMD MPSoC PS PCIe使用要點

評論