研究背景

CMOS技術是無數現代電子產品、儀器和計算工具的大腦。60多年來,CMOS技術在性能、能效和單位功能成本方面持續增長,這得益于遵循摩爾定律的硅基MOSFET的不斷擴展。雖然仍在全力以赴,但硅基CMOS已開始顯示出未來技術節點出現問題的早期跡象。前面有兩個主要的技術障礙:1)對于亞10 nm節點,必須積極減小溝道厚度以保持柵極靜電,從而保持理想的器件性能。硅和其他塊材半導體由于有害的量子限制效應和溝道-電介質界面處電荷載流子的散射增加而容易受到厚度縮放的影響,從而導致遷移率嚴重下降。2)算術核心或邏輯單元與數據存儲或內存單元的物理分離,這是馮諾依曼架構所要求的,限制了CMOS處理器在計算和數據密集型應用中的能效。第一個問題的解決方案是超薄通道材料的創新。第二個問題的解決方案是非馮諾依曼架構,其中消除了邏輯和內存之間的物理分離。

成果介紹

有鑒于此,近日,美國賓夕法尼亞州立大學Saptarshi Das教授團隊首次報道了大面積生長的n型MoS2和p型釩摻雜WSe2 FET的異質集成,具有非易失性和模擬存儲器存儲能力,可以實現非馮諾依曼2D CMOS平臺。這種制造工藝流程允許精確定位n型和p型FET,這對于任何IC開發都至關重要。本文還演示了使用這種非馮諾依曼2D CMOS平臺的反相器和簡化的2輸入1輸出多路復用器和神經形態計算原語,例如高斯、sigmoid和tanh激活函數。該演示展示了晶圓級2D材料異質集成的可行性。文章以“Heterogeneous Integration of Atomically Thin Semiconductors for Non-von Neumann CMOS”為題發表在著名期刊Small上。

圖文導讀

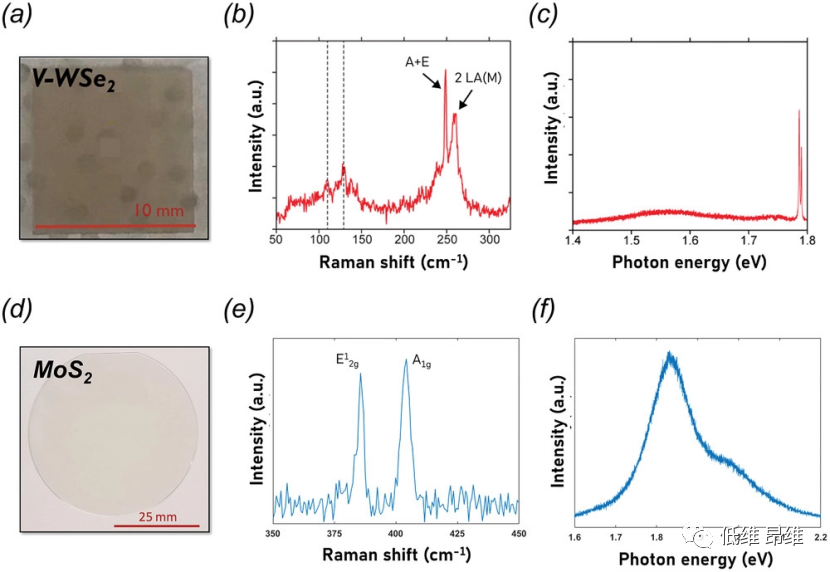

圖1. 大面積p型V-WSe2和n型MoS2。(a)在c面藍寶石襯底上MOCVD生長和完全聚結的單層V-WSe2的光學圖像。(b&c)V-WSe2的拉曼光譜和光致發光光譜。(d)在c面藍寶石襯底上MOCVD生長和完全聚結的單層MoS2的光學圖像。(e&f)MoS2的拉曼光譜和光致發光光譜。

V-WSe2薄膜在定制的冷壁MOCVD反應器中沉積在10 mm×10 mm的c面藍寶石襯底上。W(CO)6、H2Se和V(C5H5)2分別用作金屬、硫族元素和摻雜劑前驅體,H2作為載氣。MOCVD合成使用三步生長方法進行,其中摻雜劑與金屬前驅體在生長的所有階段同時引入反應室。圖1a顯示了生長襯底上完全聚結的單層V-WSe2的光學圖像。圖1b所示的拉曼光譜顯示缺陷激活的ZA(M)和LA(M)模式的強度分別在129.2和109.9 cm-1處增加,同時WSe2的A+E模式在248.7 cm-1處增加,這是故意引入雜質引起V-WSe2晶格擾動的直接證據。此外,如圖1c所示,PL信號由于正三重子的非輻射復合而完全猝滅,其中由于薄膜中的空穴數量增加,預計其密度會增加。類似地,通過MOCVD將單層MoS2沉積在外延2英寸c面藍寶石襯底上。圖1d顯示了生長襯底上完全聚結的單層MoS2的光學圖像。圖1e給出了單層MoS2的拉曼光譜,在383和404 cm-1處有兩個特征峰,分別對應于面內E2g1和面外A1g模式,預期的單層峰分離約為19 cm-1。圖1f顯示了峰值為1.83 eV的PL光譜,證實了單層MoS2。

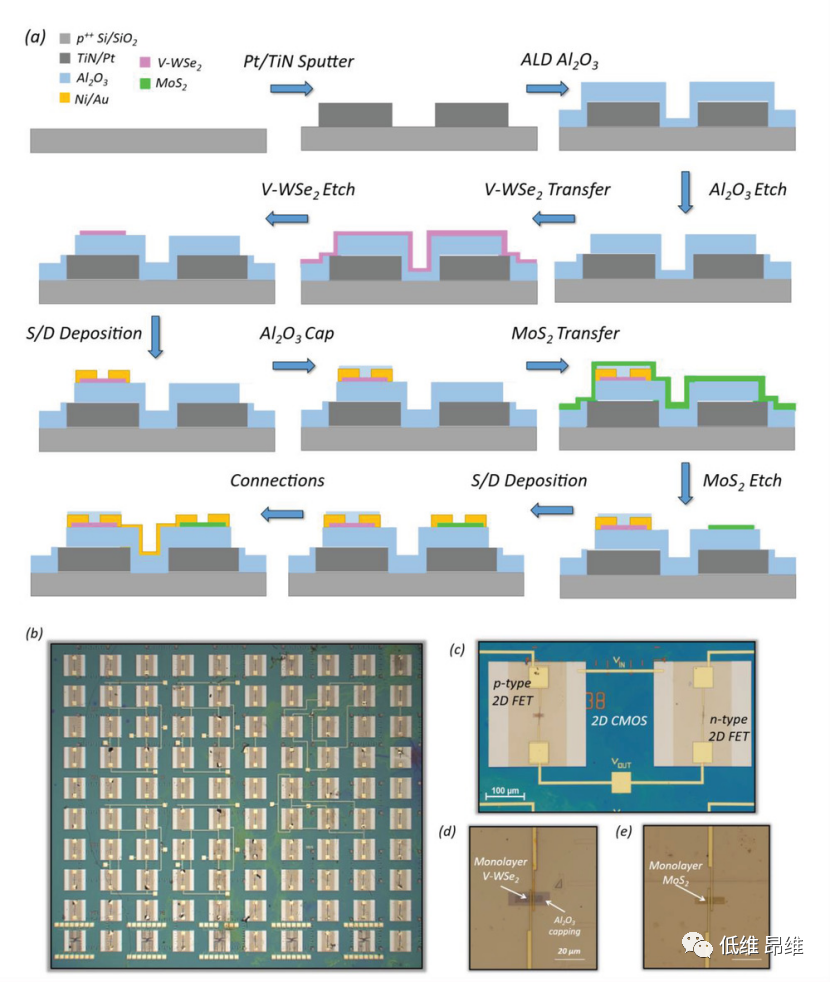

圖2. p型V-WSe2和n型MoS2的集成。(a)使用n型MoS2和p型V-WSe2實現2D CMOS基集成電路的制造工藝流程。(b)顯示芯片布局的代表性光學圖像。(c)2D CMOS反相器。(d)具有Al2O3覆蓋層的單層V-WSe2 FET的光學圖像,可保護底層材料免受后續制造步驟的影響。(e)單層MoS2 FET的光學圖像。

圖2a總結了整個制造工藝流程,允許在SiO2/p++-Si襯底上精確定位單獨柵控的p型和n型2D FET。第一步是制造局部背柵島。為此,采用電子束光刻技術定義250 μm×250 μm正方形,然后濺射20 nm TiN和50 nm Pt。選擇Pt作為背柵接觸是因為它的功函數大。沉積TiN層來促進Pt和SiO2之間的粘附。在背柵接觸放置之后,使用ALD沉積50 nm Al2O3作為背柵氧化物。然后使用光學光刻來定義可以訪問Pt柵電極的區域,然后使用BCl3氣體進行反應離子刻蝕(RIE)步驟以刻蝕暴露的氧化鋁。刻蝕在20 s四個循環中完成,以避免襯底加熱效應。在制造Al2O3/Pt/TiN背柵島堆疊后,使用PMMA輔助的濕法轉移技術將V-WSe2從生長襯底轉移到島襯底。然后RIE使用SF6氣體在5 ℃下30 s,用于分離5 μm×20 μm的V-WSe2條帶。這些分離的V-WSe2薄膜位于島的頂部,需要用作p型FET。通過這種方式,p型FET可以在襯底的任何位置制造,從而允許設計任何復雜的CMOS電路。最后,通過電子束蒸發40 nm Ni/30 nm Au接觸完成p型FET制造。所有p型V-WSe2 FET的溝道長度和寬度分別設計為1和5 μm。接下來,進行另一個電子束光刻步驟,然后進行30 nm Al2O3蒸發以封裝所有p型FET,保護它們免受后續制造步驟的影響。然后使用相同的濕法轉移技術將MOCVD MoS2薄膜轉移到襯底上。然后重復用于制造p型FET的相同制造步驟,在所需的島上制造MoS2基n型FET。所有n型MoS2 FET的溝道長度和寬度也分別設計為1和5 μm。最后,p型FET和n型FET之間的必要電路連接是通過使用電子束光刻定義7 μm寬的線,然后使用電子束沉積蒸發60 nm Ni/30 nm Au來實現的。圖2b-d分別顯示了完全制造的2D CMOS芯片、代表性電路以及單獨n型MoS2和p型V-WSe2 FET的光學圖像。

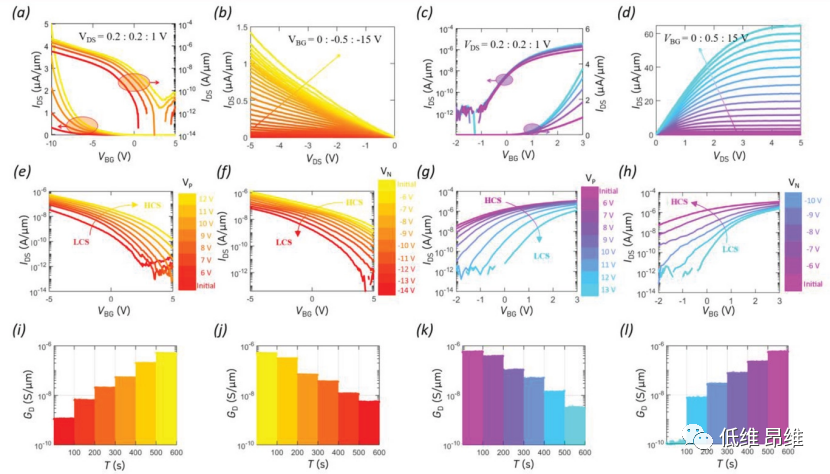

圖3. 非馮諾依曼2D CMOS的電學表征。(a&b)基于單層V-WSe2的代表性p型FET的轉移和輸出特性。(c&d)基于單層MoS2的代表性n型FET的轉移和輸出特性。(e&f)使用不同幅度的大正(VP)和大負(VN)電壓脈沖對V-WSe2 FET進行編程。(g&h)使用不同幅度的大正(VP)和大負(VN)電壓脈沖對MoS2 FET進行編程。(i&j)V-WSe2 FET的編程后和擦除后電導狀態的非易失性保留。(k&l)MoS2 FET的編程后和擦除后電導狀態的非易失性保留。

在沉積電路演示所需的連接線之前,對p型和n型FET進行了電學表征。圖3a和b顯示了基于V-WSe2的代表性p型FET的轉移和輸出特性。MoS2基n型FET的相同兩個圖如圖3c和d所示。p型V-WSe2 FET表現出電流開/關比(rON/OFF)≈105和亞閾值斜率(SS)≈470 mV dec-1。在10 nA μm-1等電流下提取的閾值電壓(VTH-p)為≈-3 V,從峰值跨導中提取的空穴場效應遷移率(μp)為≈2 cm2 V-1 s-1。在VDS=5 V時,對于≈1.5×1013 cm-2的反轉載流子密度,導通電流(Ip)達到≈1.5 μA μm-1。n型MoS2 FET的rON/OFF≈107,SS≈450 mV dec-1,閾值電壓(VTH-n)≈2.8 V,電子場效應遷移率(μn)≈17 cm2 V-1 s-1。在VDS=5 V時,對于≈1.5×1013 cm-2的反轉載流子密度,導通電流(IOn)高達≈65 μA μm-1。與V-WSe2 FET相比,對于相似的反轉電荷載流子密度,n型MoS2 FET達到更高的導通電流。這可以歸因于遷移率值的差異以及Ni/MoS2界面處的低肖特基勢壘(SB)高度導致接觸電阻的顯著差異,這從它們各自的輸出特性可以看出。

上述特征的2D FET還表現出模擬編程和電導狀態的非易失性保留,如圖3e-h所示。這種能力可歸因于電介質/2D界面處/附近的電荷俘獲/去俘獲現象。將高正編程電壓脈沖(VP)施加到這些器件的局部背柵,將兩個器件的閾值電壓轉移到正側。對于大的正VP值,在給定VBG處測量的電導對于p型FET將增加,對于n型FET將減少,分別如圖3e和g所示。同樣,施加高負電壓脈沖(VN)將導致閾值電壓向負側偏移,從而導致p型FET從高電導狀態變為低電導狀態,對于n型FET反之亦然,如圖3f和h所示。無論編程電壓脈沖的幅度和持續時間如何,發現在這些編程電導狀態中的每一個的存儲器保留對于兩種類型的器件都是穩定的。圖3i-l分別顯示了p型V-WSe2和n型MoS2 FET在VBG=VR=0 V的讀取電壓下提取的100 s內不同編程后和擦除后電導狀態(GDS)的演變。雖然傳統的存儲器需要多年的非易失性保留,但包括神經形態和邊緣計算在內的許多內存計算應用程序放寬了對長期保留的要求,并且可以很好地滿足幾小時到幾天的短期存儲保留。盡管如此,這里的關鍵成就是能夠在p型和n型FET中編程和存儲模擬電導狀態,從而首次實現非馮諾依曼CMOS。

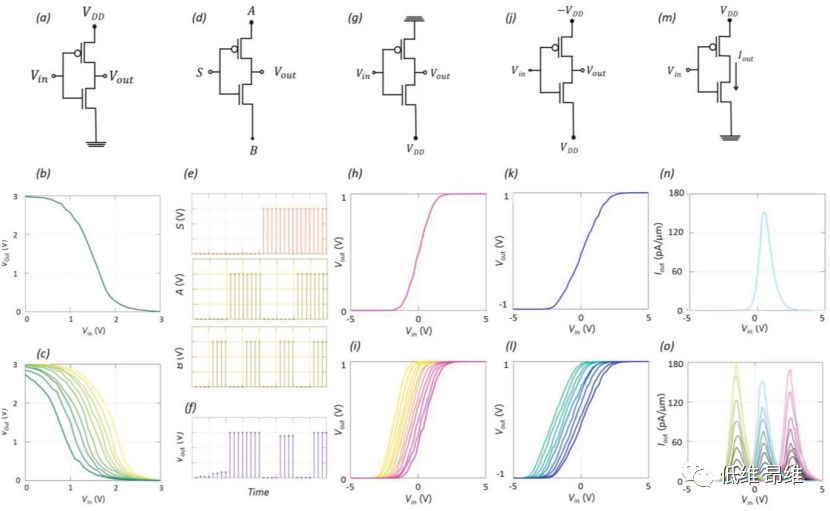

圖4. 2D CMOS基內存計算原語。(a-c)2D CMOS基可編程反相器的電路原理圖、輸出(Vout)與輸入(Vin)特性以及可重構的開關閾值(VSW)。(d-f)2×1 MUX的電路原理圖,施加到選擇器S和輸入A和B的電壓波形,以及輸出電壓(Vout)波形。(g-i)電路原理圖、輸出(Vout)與輸入(Vin)特性,以及使用可編程2D CMOS實現的可重構sigmoid激活函數。(j-l)電路原理圖、輸出(Vout)與輸入(Vin)特性,以及使用可編程2D CMOS實現的可重構雙曲正切激活函數。(m-o)電路原理圖、輸出(Vout)與輸入(Vin)特性,以及使用可編程2D CMOS實現的可重構高斯激活函數。

使用上述2D FET的非易失性編程能力,在此展示了可重構的數字和神經形態計算原語。圖4a顯示了2D CMOS反相器的電路原理圖。反相器是IC技術中的核心邏輯元件,需要p型和n型晶體管來實現高增益。盡管已經展示了僅基于具有電阻負載的n型MoS2 FET的反相器,但這種設計存在更高的功耗和更低的噪聲容限。圖4b顯示了反相器特性,增益≈4。雖然反相器是有用的邏輯元件,但可編程反相器對于數字和模擬電路設計都具有很高的意義。具有可編程開關閾值的反相器可以根據應用和環境要求設置電壓參考電平,從而減少電路占用空間和能量消耗。圖4c顯示了2D CMOS反相器的開關閾值(VSW)。

圖4d顯示了2×1 MUX的電路原理圖。MUX是一種常見的電子器件,用于選擇性地在各種輸入之間切換。在2×1 MUX的情況下,選擇器線S可用于在兩個輸入A和B之間切換。通過將p型V-WSe2 FET與n型MoS2 FET串聯來使用簡化的MUX設計。兩個器件的局部背柵短路并連接到選擇器線,而輸入A和B分別施加到p型FET的漏極端和n型FET的源極端。理想情況下,當S=0時,輸入A應反映在輸出(Vout)上,而當S=1時,Vout應為輸入B。圖4e顯示了選擇器S和輸入A和B的波形,圖4f顯示了Vout。顯然,2晶體管電路可以用作2×1 MUX,從而降低能耗和面積開銷。

接下來,實現可重構的神經形態原語,例如sigmoid、雙曲正切(tanh)和高斯激活函數。圖4g顯示了由p型V-WSe2 FET和n型MoS2 FET串聯組成的電路原理圖,以實現sigmoid激活功能。輸入(Vin)施加于兩個器件的公共背柵端,而VDD和GND分別施加到n型和p型FET的源極和漏極。圖4h顯示了在n型和p型FET的公共節點端處測量的輸出電壓(Vout)與Vin的關系,類似于sigmoid激活函數。與反相器的情況類似,sigmoid激活曲線也可以通過對p型和n型FET進行相應編程來編程為不同的閾值。測量了具有不同開關閾值的各種sigmoid曲線,如圖4i所示。對于相同的sigmoid電路設計,通過在p型FET的漏極端施加-VDD,如圖4j所示,得到如圖4k所示的雙曲正切(tanh)曲線。這里,函數從-1切換到+1。與上述情況類似,該函數也可以編程為不同的狀態,如圖4l所示。最后,使用圖4m所示的電路設計實現高斯激活函數。當Vin值為大的正或大的負時,串聯連接的兩個FET中的一個關閉,防止任何電流在電路中流動。然而,隨著n型MoS2 FET從關閉狀態切換到開啟狀態,電流傳導開始并隨著Vin遵循亞閾值特性呈指數增加,并達到由VDD確定的峰值幅度。超過這個峰值,電流開始隨著p型V-WSe2 FET的亞閾值特性呈指數下降。因此,p型V-WSe2和n型MoS2 FET的串聯表現出具有指數尾的非單調傳輸特性,可模擬高斯分布。然而,高斯的幅度可以通過VDD來改變,而平均值可以通過對底層p型和n型FET進行編程來相應地調整。具有不同幅度和平均值的高斯曲線如圖4o所示。

總結與展望

本文展示了基于p型V-WSe2和n型MoS2的可編程FET的異質集成,用于實現各種數字和神經形態計算原語。本文的研究結果是實現2D CMOS基集成電路的第一步,盡管仍有一些挑戰有待緩解。例如,改進p型V-WSe2的合成可以帶來更好的器件和電路性能、壽命和良率。此外,金屬功函數工程可用于進一步提高n型和p型2D FET的性能。未來的工作還將通過提出材料、器件和電路級別的解決方案,專注于開發更復雜的2D CMOS電路。材料合成的優化、浮柵的開發和集成以及接觸工程都是將探索實現2D TMDs超大規模集成電路(VLSI)的途徑。

審核編輯:湯梓紅

-

CMOS

+關注

關注

58文章

5724瀏覽量

235702 -

MOSFET

+關注

關注

147文章

7202瀏覽量

213629 -

FET

+關注

關注

3文章

634瀏覽量

63009 -

Small

+關注

關注

1文章

13瀏覽量

10332

原文標題:Small:原子薄半導體的異質集成,用于非馮諾依曼CMOS

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

可編程7.8V UVLO的ADP2302降壓型穩壓器典型應用

USB過流保護IC,可編程的限流開關

USB限流開關IC,具有可編程的電流限制

過流保護芯片,可編程的限流開關

網絡型可編程控制實訓裝置相關資料分享

N型場效應管FET是如何進行工作的?

FX2N可編程序控制器

基于MoS2高密度和高性能的大規模柔性集成電路的制造挑戰

HAT1089C 數據表(-20V -2A Silicon P Channel MOS FET / Power Switching)

HAT1095C 數據表(-12V -2A Silicon P Channel MOS FET / Power Switching)

HAT1089C 數據表(-20V -2A Silicon P Channel MOS FET / Power Switching)

基于p型V-WSe2和n型MoS2的可編程FET的異質集成

基于p型V-WSe2和n型MoS2的可編程FET的異質集成

評論