學(xué)習(xí)內(nèi)容

本文主要介紹了AXI通道以及在每個(gè)通道下信號(hào)的概述。

AXI通道定義

簡(jiǎn)單回顧前文提到的AXI的通道定義,AXI協(xié)議是基于突發(fā)的,并定義了以下獨(dú)立的傳輸通道:

? read address

? read data

? write address

? write data

? write response

每個(gè)獨(dú)立通道由一組信息信號(hào)、VALID信號(hào)和READY信號(hào)組成。用于提供雙向握手機(jī)制。VALID信號(hào):信息源端使用VALID信號(hào)來顯示何時(shí)是有效地址;數(shù)據(jù)或控制信息是否在通道上可用。READY信號(hào):目的端使用READY信號(hào)來顯示何時(shí)可以接受信息。LAST信號(hào):讀數(shù)據(jù)通道和寫數(shù)據(jù)通道都包括一個(gè)LAST信號(hào),以指示傳輸中的最后一個(gè)數(shù)據(jù)。

讀寫數(shù)據(jù)地址通道

讀寫通道都各自包含了他們各自的地址通道,地址通道攜帶了所有被需請(qǐng)求的的地址和相關(guān)的控制信息。

讀數(shù)據(jù)通道

讀數(shù)據(jù)通道把讀數(shù)據(jù)和讀響應(yīng)信息從slave傳送到master。其中包含下述信息:

數(shù)據(jù)總線,可以是8、16、32、64、128、256、512、1024位。

一個(gè)讀響應(yīng)信號(hào)用于表示讀操作完成狀態(tài)。

寫數(shù)據(jù)通道

寫數(shù)據(jù)通道將寫數(shù)據(jù)從master傳送到slave。其中包含下述信息:

數(shù)據(jù)總線,可以是8、16、32、64、128、256、512、1024位。

一個(gè)字節(jié)的通道頻閃信號(hào)(WSTRB)指示8個(gè)數(shù)據(jù)位,指示哪些數(shù)據(jù)字節(jié)是有效的。

寫數(shù)據(jù)通道信息總是被當(dāng)作緩沖處理,因此主機(jī)執(zhí)行寫操作時(shí),不需要從機(jī)確認(rèn)之前的寫操作。

寫響應(yīng)通道

寫響應(yīng)通道由從機(jī)發(fā)送給主機(jī),包含了寫響應(yīng)信號(hào),用于指示當(dāng)前寫操作是否完成。所有寫操作都需要在寫響應(yīng)通道上發(fā)送完成信號(hào)。

AXI總線信號(hào)描述

了解完通道的內(nèi)容,接著介紹具體的信號(hào)功能。本節(jié)介紹的是AXI4-Full的信號(hào)功能,后文將介紹AXI4-Lite接口,相對(duì)AXI4-Full,AXI4-Lite接口信號(hào)會(huì)少很多。

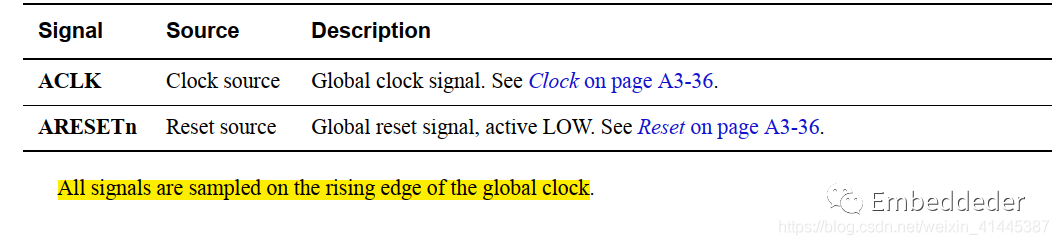

全局信號(hào)

ARESETn :復(fù)位信號(hào)低電平有效。

在AXI總線中所有的數(shù)據(jù)都是在全局時(shí)鐘的上升沿進(jìn)行采樣的。

寫地址通道信號(hào)

下面的表格列舉出寫地址通道的信號(hào),常用的信號(hào)將加粗標(biāo)注。

| AWID | Master | 寫地址ID。這個(gè)信號(hào)是信號(hào)的寫地址組的識(shí)別標(biāo)簽。指定某些特殊傳輸任務(wù)的順序 |

| AWADDR | Master | 寫地址。寫地址給出了寫突發(fā)傳輸下第一個(gè)數(shù)據(jù)的地址。 |

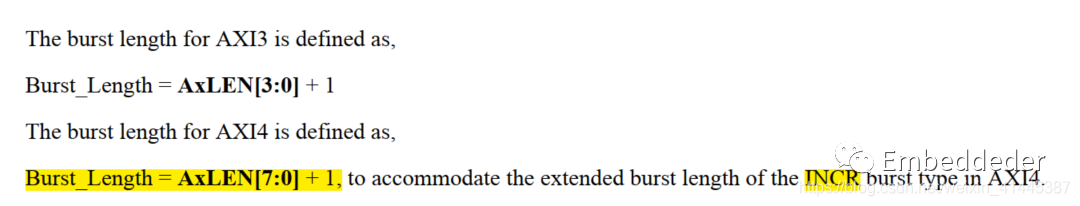

| AWLEN | Master | 突發(fā)傳輸長(zhǎng)度。AWLEN給出了在一次突發(fā)傳輸中的確切數(shù)目長(zhǎng)度。在AXI3和AXI4定義不同 |

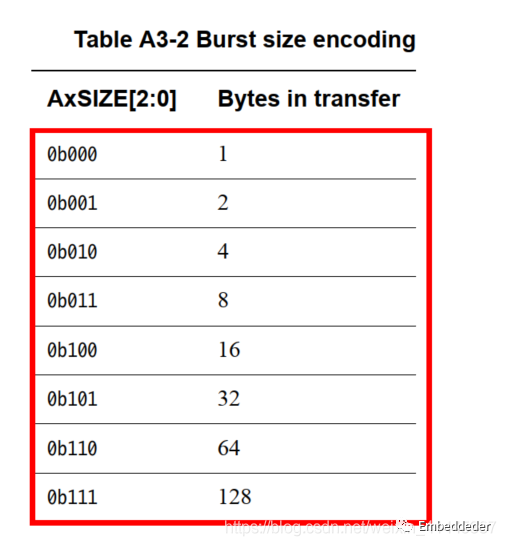

| AWSIZE | Master | 突發(fā)傳輸?shù)拇笮 _@個(gè)信號(hào)指示了單次傳輸?shù)牡臄?shù)據(jù)大小。 |

| AWBURST | Master | 突發(fā)傳輸?shù)念愋汀M话l(fā)類型和大小信息,確定如何計(jì)算突發(fā)內(nèi)每個(gè)傳輸?shù)牡刂贰?/td> |

| AWLOCK | Master | 鎖存的類型。提供關(guān)于轉(zhuǎn)移的附加信息。在AXI3和AXI4定義不同,區(qū)分正常傳輸(0)和獨(dú)有傳輸(1) |

| AWCACHE | Master | 內(nèi)存類型。這個(gè)信號(hào)指示操作如何在系統(tǒng)中進(jìn)行。總線中的存儲(chǔ)類型(0010:不緩存模式) |

| AWPROT | Master | 保護(hù)類型。這個(gè)信號(hào)表明操作的優(yōu)先級(jí)和安全級(jí)別,以及操作是數(shù)據(jù)訪問還是指令訪問。 |

| AWQOS | Master | 服務(wù)質(zhì)量QoS。為每個(gè)寫操作發(fā)送的QoS標(biāo)識(shí)符。僅在AXI4中支持。 |

| AWREGION | Master | 區(qū)域ID標(biāo)識(shí)符。允許一個(gè)slave上的單個(gè)物理接口用于多個(gè)邏輯接口。僅在AXI4中支持。 |

| AWUSER | Master | 用戶信號(hào)。可選寫地址通道自定義信號(hào)。(完成用戶的自定義操作),僅在AXI4中支持。 |

| AWVALID | Master | 寫地址有效。這個(gè)信號(hào)表明通道正在發(fā)送有效的寫地址和控制信息。 |

| AWREADY | Slave | 寫地址準(zhǔn)備。這個(gè)信號(hào)表明從機(jī)準(zhǔn)備接受一個(gè)地址和相關(guān)的控制信號(hào)。 |

| Signal | Source | Description |

|---|

如何確定突發(fā)傳輸?shù)拇笮 ㈤L(zhǎng)度、類型?

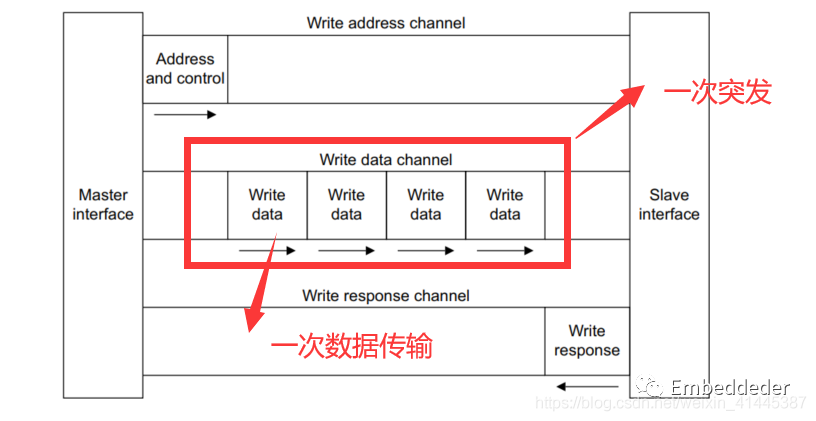

下面給出一個(gè)例子:如下圖所指示:下圖是一個(gè)讀地址通道的操作,這里用方框框選的數(shù)據(jù)傳輸,是一次突發(fā)傳輸。對(duì)于該次突發(fā)傳輸:一共進(jìn)行了四次數(shù)據(jù)傳輸,所以突發(fā)的長(zhǎng)度就是4。然后針對(duì)一次數(shù)據(jù)傳輸,每次數(shù)據(jù)傳輸位寬,為突發(fā)傳輸?shù)拇笮 <僭O(shè)傳輸?shù)臄?shù)據(jù)是8位的,這里的突發(fā)長(zhǎng)度就是8。

對(duì)于突發(fā)傳輸?shù)拈L(zhǎng)度的不同,這里直接引用ARM的文檔內(nèi)容參考即可。

對(duì)于突發(fā)的大小,這里定義了組寄存器來標(biāo)識(shí)傳輸?shù)臄?shù)據(jù)位寬:

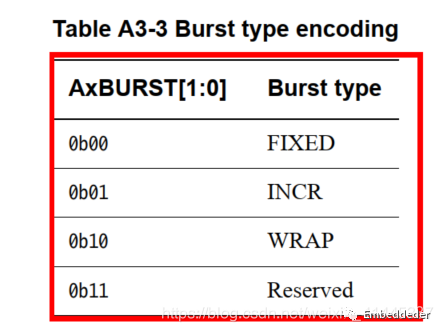

對(duì)于突發(fā)的類型,這里有三種突發(fā)類型分別如下:

FIXED(固定型):在一個(gè)固定的突發(fā)中,地址對(duì)于突發(fā)中的每一次傳輸都是相同的。這種突發(fā)類型用于重復(fù)訪問相同的位置,例如加載或清空FIFO。INCR(自增型):在遞增的突發(fā)中,突發(fā)中每個(gè)傳輸?shù)牡刂肥乔耙粋€(gè)傳輸?shù)牡刂返脑隽俊T隽恐等Q于傳輸?shù)拇笮 @纾谝粋€(gè)大小為4個(gè)bvtes的突發(fā)中,每個(gè)傳輸?shù)牡刂肥乔耙粋€(gè)地址的加4個(gè)。這種突發(fā)類型用于訪問順序存儲(chǔ)器。

WRAP(回環(huán)突發(fā)):回環(huán)突發(fā)類似于遞增突發(fā)。不同的是,如果達(dá)到了地址上限,地址將被重新裝一個(gè)較低的地址。這種突發(fā)類型用于高速緩存線訪問。使用回環(huán)突發(fā)必須遵守下列限制條件:

起始地址必須與每次傳輸?shù)拇笮∫恢?

突發(fā)的長(zhǎng)度必須是2、4、8或16。

回環(huán)突發(fā)要求:

突發(fā)使用的最低地址與要傳輸?shù)臄?shù)據(jù)的總大小對(duì)齊,即為((突發(fā)中每個(gè)傳輸?shù)拇笮?×(突發(fā)中傳輸?shù)臄?shù)量))。這個(gè)地址被定義為換行邊界。

在每次傳輸之后,地址以同樣的方式增加,就像增加帶寬一樣。但是,如果這個(gè)增加的地址是((wrap boundary) +(要傳輸?shù)臄?shù)據(jù)的總大小),那么地址就會(huì)繞到wrap boundary。

在突發(fā)中的第一次傳輸可以使用一個(gè)比繞包邊界更高的地址,這取決于適用于繞包突發(fā)的限制。這意味著對(duì)任何第一個(gè)地址高于邊界的操作,會(huì)自動(dòng)換行突發(fā)。

突發(fā)類型的寄存器的解碼表如下:

寫數(shù)據(jù)通道信號(hào)

| WID | Master | 寫ID。這個(gè)信號(hào)是寫數(shù)據(jù)傳輸?shù)腎D標(biāo)簽。僅在AXI3中支持 |

| WDATA | Master | 寫入數(shù)據(jù) |

| WSTRB | Master | 寫頻閃信號(hào)。該信號(hào)指示哪些字節(jié)通道保存有效數(shù)據(jù)。寫數(shù)據(jù)總線的每8位有一個(gè)寫頻閃位。 |

| WLAST | Master | LAST指示信號(hào)。這個(gè)信號(hào)指示寫操作中的最后一次傳輸。 |

| WUSER | Master | 用戶信號(hào)。可選寫入數(shù)據(jù)通道的自定義信號(hào)。僅在AXI4中支持。 |

| WVALID | Master | 寫有效。這個(gè)信號(hào)表明有效的寫數(shù)據(jù)和頻閃是可用的 |

| WREADY | Slave | 寫準(zhǔn)備。這個(gè)信號(hào)表明從機(jī)可以接受寫數(shù)據(jù)。 |

| Signal | Source | Description |

|---|

寫響應(yīng)通道信號(hào)

| BID | Slave | 寫ID。這個(gè)信號(hào)是寫數(shù)據(jù)傳輸?shù)腎D標(biāo)簽。僅在AXI3中支持 |

| BRESP | Slave | 寫響應(yīng)。這個(gè)信號(hào)指示寫操作的狀態(tài)。 |

| BUSER | Slave | 用戶信號(hào)。可選寫響應(yīng)通道中的自定義信號(hào)。僅在AXI4中支持。 |

| BVALID | Slave | 寫響應(yīng)有效。該信號(hào)表明通道正在發(fā)出有效的寫響應(yīng)信號(hào)。 |

| BREADY | Master | 寫響應(yīng)準(zhǔn)備。這個(gè)信號(hào)表明主機(jī)可以接受寫響應(yīng)。 |

| Signal | Source | Description |

|---|

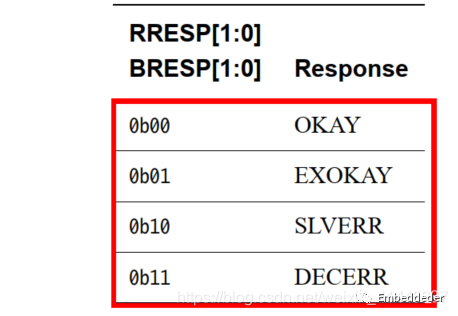

對(duì)于寫響應(yīng)通道的BRESP信號(hào),具體響應(yīng)有下述四種類型:

OKAY:正常訪問成功。表示正常訪問成功。也可以指示獨(dú)占訪問失敗。

EXOKAY:獨(dú)占訪問。指示獨(dú)占訪問的讀或?qū)懖糠忠呀?jīng)成功。

SLVERR:從機(jī)錯(cuò)誤。當(dāng)訪問成功到達(dá)從機(jī)時(shí)使用,但是從機(jī)向主機(jī)返回一個(gè)錯(cuò)誤條件。

DECERR:解碼錯(cuò)誤。通常由互連組件生成,以指示在操作地址處沒有從從機(jī)響應(yīng)。

BRESP信號(hào)解碼表如下:

讀地址通道信號(hào)

| ARID | Master | 讀地址ID。這個(gè)信號(hào)是信號(hào)讀地址組的識(shí)別標(biāo)簽。指定某些特殊傳輸任務(wù)的順序 |

| ARADDR | Master | 讀地址。讀地址給出了讀突發(fā)傳輸下第一個(gè)數(shù)據(jù)的地址。 |

| ARLEN | Master | 突發(fā)傳輸長(zhǎng)度。AWLEN給出了在一次突發(fā)傳輸中的確切數(shù)目長(zhǎng)度。在AXI3和AXI4定義不同 |

| ARSIZE | Master | 突發(fā)傳輸?shù)拇笮 _@個(gè)信號(hào)指示了單次傳輸?shù)牡臄?shù)據(jù)大小。 |

| ARBURST | Master | 突發(fā)傳輸?shù)念愋汀M话l(fā)類型和大小信息,確定如何計(jì)算突發(fā)內(nèi)每個(gè)傳輸?shù)牡刂贰?/td> |

| ARLOCK | Master | 鎖存的類型。提供關(guān)于轉(zhuǎn)移的附加信息。在AXI3和AXI4定義不同,區(qū)分正常傳輸(0)和獨(dú)有傳輸(1) |

| ARCACHE | Master | 內(nèi)存類型。這個(gè)信號(hào)指示操作如何在系統(tǒng)中進(jìn)行。總線中的存儲(chǔ)類型(0010:不緩存模式) |

| ARPROT | Master | 保護(hù)類型。這個(gè)信號(hào)表明操作的優(yōu)先級(jí)和安全級(jí)別,以及操作是數(shù)據(jù)訪問還是指令訪問。 |

| ARQOS | Master | 服務(wù)質(zhì)量QoS。為每個(gè)讀操作發(fā)送的QoS標(biāo)識(shí)符。僅在AXI4中支持。 |

| ARREGION | Master | 區(qū)域ID標(biāo)識(shí)符。允許一個(gè)slave上的單個(gè)物理接口用于多個(gè)邏輯接口。僅在AXI4中支持。 |

| ARUSER | Master | 用戶信號(hào)。可選讀地址通道自定義信號(hào)。(完成用戶的自定義操作),僅在AXI4中支持。 |

| ARVALID | Master | 讀地址有效。這個(gè)信號(hào)表明通道正在發(fā)送有效的讀地址和控制信息。 |

| ARREADY | Slave | 讀地址準(zhǔn)備。這個(gè)信號(hào)表明從機(jī)準(zhǔn)備接受一個(gè)地址和相關(guān)的控制信號(hào)。 |

| Signal | Source | Description |

|---|

讀數(shù)據(jù)通道信號(hào)

| RID | Slave | 讀ID標(biāo)簽。這個(gè)信號(hào)是識(shí)別標(biāo)簽的讀取數(shù)據(jù)信號(hào)的從機(jī)產(chǎn)生的 |

| RDATA | Slave | 讀入數(shù)據(jù) |

| RRESP | Slave | 讀取響應(yīng)。這個(gè)信號(hào)指示讀傳輸?shù)臓顟B(tài)。。 |

| RLAST | Slave | LAST指示信號(hào)。這個(gè)信號(hào)指示讀操作中的最后一次傳輸。 |

| RUSER | Slave | 用戶信號(hào)。可選讀取數(shù)據(jù)通道中的用戶自定義信號(hào)。僅在AXI4中支持。 |

| WVALID | Slave | 讀有效。該信號(hào)表明通道正在發(fā)送所需的讀取數(shù)據(jù)。 |

| RREADY | Master | 讀準(zhǔn)備。該信號(hào)表明主機(jī)可以接受讀取數(shù)據(jù)和響應(yīng)信息 |

| Signal | Source | Description |

|---|

Reference

正點(diǎn)原子ZYNQ視頻教程。

ARM官方文檔:IHI0022D

審核編輯:湯梓紅

-

總線

+關(guān)注

關(guān)注

10文章

2878瀏覽量

88052 -

AXI

+關(guān)注

關(guān)注

1文章

127瀏覽量

16622

原文標(biāo)題:Reference

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Xilinx zynq AXI總線全面解讀

基于AXI總線的加法器模塊解決方案

ARM+FPGA開發(fā):基于AXI總線的GPIO IP創(chuàng)建

ZYNQ & AXI總線 & PS與PL內(nèi)部通信(用戶自定義IP)

玩轉(zhuǎn)Zynq連載3——AXI總線協(xié)議介紹1

AXI總線的相關(guān)資料下載

看看在SpinalHDL中AXI4總線互聯(lián)IP的設(shè)計(jì)

你必須了解的AXI總線詳解

淺談ZYNQ-AXI總線的信號(hào)接口要求以及時(shí)序關(guān)系

AXI總線學(xué)習(xí)(AXI3&4)

AXI通道定義及AXI總線信號(hào)描述

AXI通道定義及AXI總線信號(hào)描述

評(píng)論