工程師熟悉電磁干擾、并聯和布局,但在從硅基芯片過渡到碳化硅或寬帶隙器件時,需要多加注意。

據chip稱,硅(Si)基半導體比寬帶隙(WBG)半導體領先十年,主要是碳化硅(SiC)和氮化鎵(GaN)仍占有約90%至98%的市場份額。供應商。盡管遠非成熟的技術,WBG 半導體正在跨行業進軍,這要歸功于它們相對于硅的性能優勢,包括更高的效率、更高的功率密度、更小的尺寸和更少的冷卻。

使用基于 SiC 或 GaN 的功率半導體獲得最佳設計需要更多的專業知識和在多個領域的仔細考慮,包括開關拓撲、電磁干擾 (EMI)、布局、并聯和柵極驅動器的選擇。

解決可靠性和成本問題也很重要。

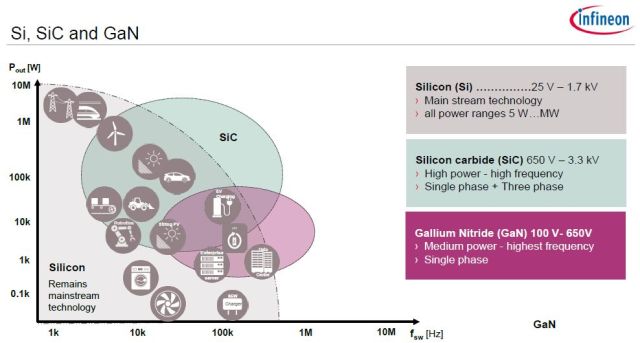

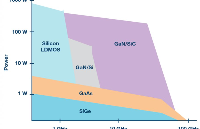

在可以使用 Si、SiC 和 GaN 的重疊應用中,選擇歸結為密度、效率和成本,一旦設計人員了解這三個參數,就會指導他們使用哪種開關技術。(圖片:英飛凌科技)

為什么要搬到WBG?

這一切都始于根據設計目標決定從基于硅的功率器件轉向基于碳化硅或氮化鎵的功率器件。

Infineon Technologies AG 功率分立器件技術營銷工程師 Bob Yee 表示,無論是使用硅還是改用 SiC 或 GaN,設計人員都必須檢查成本、效率和密度這三個因素。據記載,英飛凌憑借 CoolSiC 和 CoolGaN 產品組合同時涉足 SiC 和 GaN 市場,還提供 Si MOSFETS 和 IGBT。

Yee 說,成本以每瓦特美元、功率輸入/輸出百分比的效率以及每立方英寸瓦特的密度來衡量。“一旦你確定了這些目標,這將決定技術的類型以及成本點在哪里。”

Yee 引用了一個小尺寸適配器設計的例子說,尺寸和重量對于理解你是使用硅還是 WBG 很重要,它可能會在 Si MOSFET 上使用 GaN 晶體管 (HEMT)。原因?GaN 的更高開關頻率允許設計人員縮小磁性元件的尺寸,這在電源尺寸中占很大一部分。

“設計人員必須了解他們的密度需求是什么,這最終將決定效率,因為小尺寸的散熱空間更小,”他補充道。“這意味著效率需要更高,促使設計人員使用 WBG。”

神奇的線

幾十年來,基于硅的解決方案實現了更高的效率和更小的尺寸,但 WBG 半導體在某一點上提供了更好的效率。Yee 舉了一個 100 W 電源的例子——100 W 輸入和 94 W 輸出,這意味著 6% 的損耗或 94% 的效率。“這是從硅分離到使用 WBG 技術的神奇線,”他說。“如果工程師的設計高達 94%,那么它就被硅覆蓋了,沒有理由去 WBG 支付更多費用。但是,如果您試圖實現 96% 的效率,則除了使用 WBG 之外別無選擇,這歸結為除了拓撲之外,開關本身屬性的寄生損耗。

“如果您想實現 96% 的效率,您需要一種利用 GaN 或 SiC 的新拓撲,”Yee 補充道。

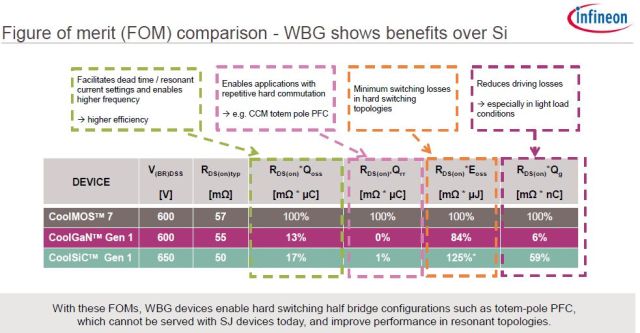

一個很好的例子是使用功率因數校正 (PFC) 拓撲。Yee 說,如果設計人員著眼于如何針對特定拓撲優化開關技術——例如,利用 WBG 的圖騰柱 PFC——它會提高性能,“這就是為什么無橋圖騰柱 PFC 真的是一個扣籃為世界銀行集團。”

設計人員需要通過查看開關技術如何針對特定拓撲進行優化以實現最大的性能改進來評估 WBG 器件。(圖片:英飛凌科技)

挑戰

設計人員可以優化他們的設計以獲得更高的頻率、更高的功率密度和更高的效率。這就是一些 WBG 技術挑戰出現的地方。當以更高頻率進行開關時,設計人員需要注意 EMI 和更高的開關損耗。

WBG 的寄生效應小于硅等效物,這意味著 EMI 很容易升高,因為它是一種更快的開關。Yee 說,當您針對高頻進行優化時,您需要注意 EMI,并且需要考慮額外的開關損耗。

SiC FET、SiC JFET 和 SiC 肖特基二極管制造商 UnitedSiC 工程副總裁 (VP) Anup Bhalla 表示同意。“EMI 問題會變得更加嚴重,尤其是當您試圖獲得更高功率密度的系統優勢時,這實際上意味著一切都變得更小,而變得更小的唯一方法就是您的開關速度要快得多。這使您可以將變壓器、電感器、散熱器和其他東西做得更小。”

Bhalla 說,更快的開關也意味著您正在以高電壓和電流變化率運行,這可能導致大的電壓過沖和 EMI 問題,因此布局變得更具挑戰性。

“電路電源端的這些快速電壓變化很容易影響電路的信號端,因為它可以在你不知情的情況下在這里或那里發送一點電壓尖峰,”他說。“它可能會在錯誤的時間觸發柵極驅動器并炸毀所有東西,因此您必須在布局上更加小心。通常需要[客戶]付出相當大的工程努力才能達到目標,而且他們中的很多人在過去的四五年里已經實現了這一飛躍。”

優化布局

布局可能是一個挑戰;Yee說,最大的障礙是在司機和大門之間。“設計師需要注意三個終端。它是驅動器輸出到柵極輸入,無論是 iw56\s SiC 還是 GaN,以及驅動器源極到 WBG 器件源極的接地連接。”

Yee 說,他們需要最小化的第一件事是環路電感,因為 WBG 部件的開關速度要快得多。“如果他們不注意這一點,他們就會制造出會發出輻射的收音機。” 因此需要特別注意這些連接。為了緩解這一挑戰,英飛凌建議使用具有開爾文源功能的 WBG 器件。

布局也會影響更高功率應用的并聯。Bhalla 說,平行是相當簡單的。“這是相同的一般物理學——你必須保持布局對稱和平衡。我們必須保持零件之間的參數分布相對緊密,這樣所有零件看起來都差不多,這樣它們就很容易平行。

“設計人員喜歡采用這些快速部件并將它們并聯起來,就像過去并聯 IGBT 一樣,”他補充道。“這很難,因為 IGBT 的速度要慢得多,因此它們更容易并聯。當您嘗試并行并同時將切換速度提高 10 倍時,您必須在布局方面做更多的工作。

“你必須小心,至少要做好一半的布局,這樣并行設備之間的所有電流路徑看起來都差不多。你不能讓一個設備的電感只有另一個的五分之一,然后期望它們并聯;這是行不通的。”

Bhalla 說,有時向工程師展示如何解決布局和并聯方面的挑戰的最簡單方法是給他們一個演示板。“我們非常小心地確保當您并行使用這些設備時,用于驅動柵極的環路必須與路由所有功率/電流的環路保持分離。柵極驅動電路是一個小回路,然后有一個強大的大回路驅動所有的功率/電流,您希望最大限度地減少這兩者之間的耦合。如果你這樣做,你就會知道并行變得更好、更容易。”

使用 GaN 器件時也是如此。“工程師必須比過去更好地理解布局,因為 GAN 速度很快,”GaN Systems 銷售和營銷副總裁 (VP)、GaN HEMT/E-HEMT 設備專家 Larry Spaziani 說。“如果您沒有正確的布局,那么您可能會遇到性能或 EMI 甚至故障模式的問題。

“GaN 不會改變布局規則,但一切都更小、更緊密、更緊湊,所以你必須確保你做得對,”他補充道。

碳化硅的小調整

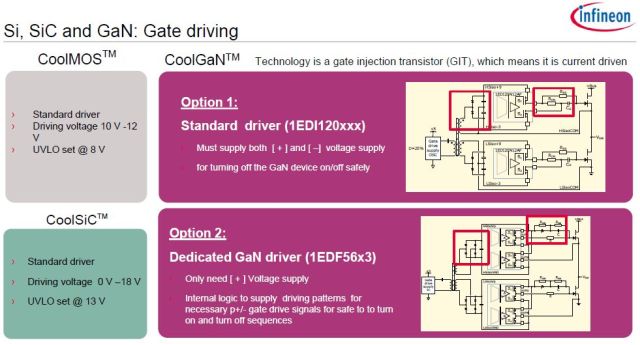

Yee 解釋說,SiC 可以用作 Si IGBT 或 Si MOSFET 的性能替代品,部分原因是驅動結構非常相似——它是一個常關部件并使用標準驅動器,但存在細微差別。

使用 Si MOSFET,驅動電壓為 10 V 至 12 V;但是,如果您使用 SiC,則為 0 V 至 18 V,并且欠壓鎖定 (UVLO) 從 Si 的 8 V 變為 SiC 的 13 V,因此設計人員在移動時需要做一些細微的調整Yee 解釋說,從 Si 到 SiC。

但是,對于GaN,驅動結構完全不同;他補充說,它與 IGBT 或 MOSFET 不同。“您必須使用具有特定開啟和關閉時間的特定驅動程序。因此,設計人員確實需要注意驅動方案,不僅要注意時序,而且如果要并行 GaN FET,則必須在驅動器和 GaN FET 之間具有完美的對稱布局。”

需要注意的是,設計人員可以使用 GaN 的標準驅動器,只要它支持柵極驅動電壓和 UVLO,但同樣需要對設計進行調整。大多數供應商建議使用更新一代的柵極驅動器,以通過能夠以最快的開關速度進行開關來獲得最高性能。

與專用 GaN 驅動器相比,使用標準柵極驅動器驅動 GaN 器件需要添加負電壓電源以安全地開啟和關閉器件。(圖片:英飛凌科技)

“如果您使用標準驅動器,則只有 GaN 才需要提供正電壓和負電壓,這就是我們更喜歡客戶使用專用驅動器的原因,”Yee 說。他推薦英飛凌的 1EDF56x3 系列 GaN 柵極驅動器。

并非所有 SiC 器件都生而平等

大多數 WBG 器件不是 Si MOSFET 或 Si 晶體管的直接替代品。需要很少或不需要額外工程工作的共源共柵型設備除外。然而,設計人員失去了 WBG 半導體的一些優勢。

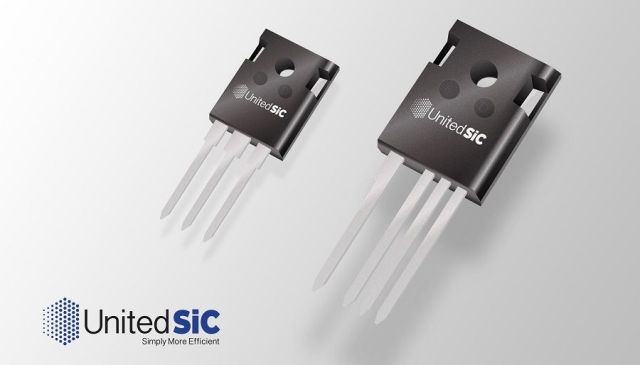

一個例子是 UnitedSiC 的 SiC 產品,它們都采用與硅兼容的封裝。這意味著這些設備可以直接將它們放入以前使用 IGBT 或 Si 超結 MOSFET 的插座中。

Bhalla 表示,其產品的獨特之處之一是它制造的基于共源共柵的設備,其工作方式類似于 MOSFET。這些 SiC FET 包括與共源共柵優化的 Si MOSFET 共同封裝的 SiC 快速 JET,以提供采用標準通孔和表面貼裝封裝的標準柵極驅動 SiC 器件。“我們的共源共柵型器件是一個字面意義上的插入式器件,除了可能的柵極電阻變化之外沒有任何變化,”他說。

此外,這些設備不需要特殊的驅動程序;Bhalla 表示,它們與市場上所有主要供應商提供的標準硅柵極驅動器 IC 兼容十年,包括與 SiC MOSFET 和“老派”IGBT 一起使用的舊款。

他補充說,在過去兩年中,已經專門為 SiC 開發了許多優秀的柵極驅動器。“它們更貴,但人們已經開始使用它們,我們的設備也與那些更好的驅動程序兼容。”

但也有一些缺點,包括不能從 WBG 設備中獲得最高性能。Bhalla 說:“我們正在銷售采用這些封裝的超高速器件,這些封裝具有很大的電感。” “當你通過這些封裝在電路中放置高壓擺率 (di/dt) 時,它只會加劇快速開關的所有問題——更大的過沖、更多的振蕩等。”

Bhalla 說,向更好的包裝過渡是一項正在進行的工作。“這就是現實:人們在使用 SiC 的部分好處的同時,仍然從他們的終端系統中獲得一些好處,這種方法既便宜又臟。

“世界上很大一部分仍然是硅,所以對于他們從硅轉向碳化硅,我們提供了一個非常好的墊腳石,”他說。

Bhalla 認為,到明年,將會有很多頂部冷卻的表面貼裝封裝,甚至是將整個半橋集成到一個封裝中的表面貼裝型模塊。“必須這樣做,因為沒有它,用戶就無法從中獲得所有好處,也無法進入下一個層次,”他說。

例如,UnitedSiC 最近推出了一款采用 TO-247 封裝的7mΩ R DS(ON)、650V器件。(低 R DS(ON)可以實現更高的效率。)該公司最接近的競爭對手的導通電阻高出 3 倍,但 UnitedSiC 遇到的一個問題是封裝引線實際上比芯片更熱。“所以我們采用了一個 200-A 的設備并將其降額到 120A,因為當我們在實踐中使用這個設備時,我們看到引線變得比芯片本身更熱,”Bhalla 說。

UnitedSiC通過在熟悉的 TO-247 封裝中結合第三代 SiC JFET 和共源共柵優化的 Si MOSFET,推出了第一款 SiC FET,R DS(on) <10 mΩ,提高了效率并降低了損耗在與 Si IGBT 相同的柵極電壓下。(圖片:UnitedSiC)

氮化鎵的好處

從消費電子產品到汽車等各個領域的 OEM 設計師都有幾個共同的設計要求:他們想要更高的功率密度和更小的電子產品。

Spaziani 說,在更高的頻率下,電源系統中的幾乎所有組件(電容器、電感器、變壓器等)都可以更小,而且由于 GaN 非常高效且產生的熱量非常少,因此不需要任何散熱器,因此設計人員只需移除散熱器即可節省空間和成本。或者它們可能保持相同的頻率以實現更高的效率。通常,即使效率提高 1%,也足以讓服務器電源領域的客戶從鉑金級升級到鈦級 [96% 的效率],他說。

Spaziani 說,這與工程師通常所做的沒有什么不同。無論是使用硅還是其他技術,他們通常都必須優化他們的電路板,但在柵極驅動方面存在差異。對于 GaN 和 SiC,柵極驅動行為不同于硅 MOSFET 和硅 IGBT,因此工程師必須問的第一件事是:“我如何驅動柵極?”

過去30年,MOSFETS基本變成了0-12-V的柵極驅動電路,而GaN要么是–3-6V,要么是0-10V,要么是0-5V;他們都有點不同,Spaziani 說。“但好消息是 GaN Systems 現在已經走過了 6 年的歷程,我們有大約 12 家主要的半導體公司已經創建了驅動 GaN 的驅動器,所以現在,這只是一個簡單的應用決策。”

GaN Systems 還提供稱為 EZDrive 的電路,無需分立驅動器。它將 12V MOSFET 驅動器轉換為具有大約六個組件的 6V GaN 驅動器。“它真的很便宜,而且適配器設計者喜歡這個電路,”Spaziani 說。“它易于使用、不耗電、體積小,而且無需定制柵極驅動器。”

揭穿 GaN 神話

GaN 供應商認為,關于 GaN 技術仍然存在一些錯誤或半真半假的神話。問題包括 EMI、并聯、雪崩能力、可靠性和成本。

GaN 器件的 EMI 更糟。GaN 提供出色的開關邊緣,可實現更高的效率和更高的頻率,但這并不意味著 EMI 更糟。事實上,供應商表示它通常比具有良好布局的硅更好,并且可以產生更小的 EMI 濾波器,從而降低成本。

并行是一個常見的問題。一種誤解是 GaN 只擅長低功率和高頻率。例如,GaN Systems 的客戶以 20 kHz 至 20 MHz 的頻率進行切換,并且在高功率下,它們是并聯設備。GaN晶體管可以很好地并聯;只需確保每個晶體管承載的電流量大致相同。例如,如果您將兩個設備并聯,并且一個晶體管承載 70% 的電流,則它會磨損得更快,電路也會更快地發生故障。警告:來自不同 SiC 和 GaN 供應商的設備的并行方式略有不同。

沒有雪崩能力。MOSFET 進入雪崩模式以抑制電壓尖峰以保護電路的其余部分免于故障。GaN 器件制造商解決這個問題的方法是在額定電壓中設計大量余量。例如,GaN Systems 的 650V 額定設備在電壓遠遠超過 1,000V 時才會出現故障。

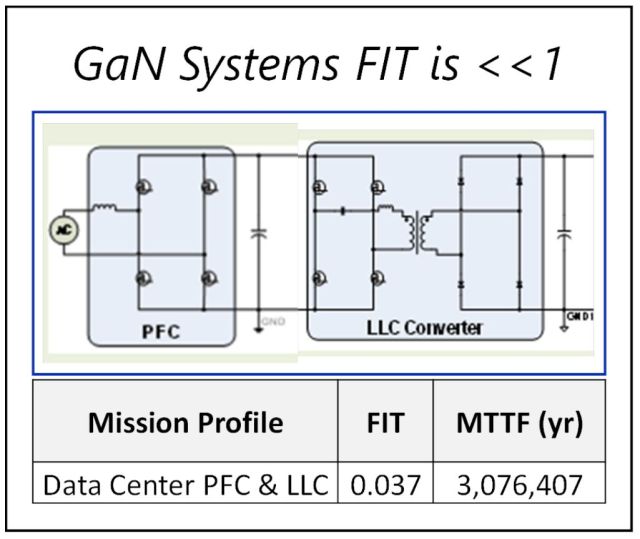

可靠性和成本不等于硅。可靠性是通過及時故障 (FIT) 來衡量的。硅已經存在了幾十年,并且已被大多數供應商證明是可靠的。但 WBG 半導體并非如此。與任何新技術一樣,可靠性風險增加且成本更高。WBG 器件和硅器件之間的比較很難,因為硅芯片的可靠性有據可查,而且多年來的大批量生產降低了成本。

但一些 WBG 供應商,如 GaN Systems,表示可靠性 [FIT] 與硅相當,價格差距在過去五年中顯著縮小,從貴 3 倍到 5 倍下降到 1.5 倍到 2 倍。

GaN Systems 的器件顯示 FIT 率 <0.1。(圖片:GaN Systems)

審核編輯 黃昊宇

-

半導體

+關注

關注

334文章

27515瀏覽量

219773 -

設計

+關注

關注

4文章

818瀏覽量

69911 -

SiC

+關注

關注

29文章

2841瀏覽量

62721 -

GaN

+關注

關注

19文章

1947瀏覽量

73678

發布評論請先 登錄

相關推薦

半導體需要做哪些測試

中國半導體的鏡鑒之路

WBG 器件給柵極驅動器電源帶來的挑戰

Nexperia斥資2億美元加速漢堡工廠寬帶隙(WBG)半導體研發與生產

ATA-5420前置微小信號放大器如何進行半導體測試

安世半導體Nexperia將在漢堡投資2億美元研發下一代寬禁帶半導體產品(WBG)

寬帶隙(WBG)半導體助力可持續電動汽車電源轉換,頂部冷卻(TSC)技術提升熱性能

瑞薩電子收購Transphorm,加速GaN功率半導體市場布局

半導體IC設計是什么?IC設計和芯片設計區別

使用 WBG 半導體進行設計需要更多的奉獻精神

使用 WBG 半導體進行設計需要更多的奉獻精神

評論