CPU又名中央處理器,作為計算機系統(tǒng)的運算和控制核心,是信息處理、程序運行的最終執(zhí)行單元。Logisim是一款邏輯電路設計仿真軟件,我們可以在這個軟件上面繪制各種邏輯電路,當然也包括CPU。

電腦中有intel、AMD、Apple的CPU,手機中也有華為、高通、Apple的SOC,每次我研究這些他們設計的硬件時,總是覺得研究得不能很深入,往往只是看看官網(wǎng)參數(shù)和一些評測數(shù)據(jù)罷了。但是有些時候,總是有那么些不合常理的存在讓我對CPU的認知一次又一次地被刷新。半年前是AMD(他們的筆記本CPU性能竟然直逼臺式機),幾個月前是Apple(他們的15W的M1芯片竟然砍倒一片幾十W乃至幾百W的臺式機CPU,核顯更是劍指獨顯)。這使我很煩躁,因為只是在外頭看個熱鬧,很多原因我不能探明。所以就有了以下的一切。

這是第一章節(jié)《單周期CPU》

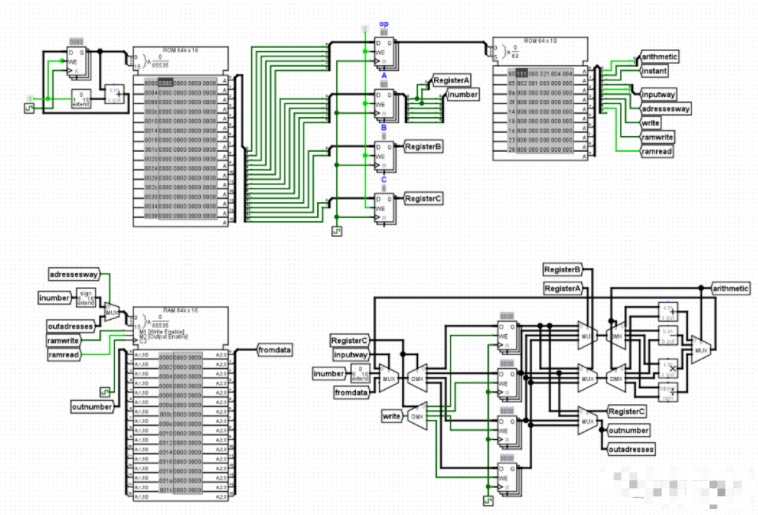

下面直接上圖:

這便是該CPU全貌了

左上的部分是取指單元,其作用是從指令內(nèi)存中取出指令。右上是譯碼單元,其作用是把指令所需操作翻譯成電路的控制信號。右下是計算單元,通過調(diào)整對應的控制信號可以進行兩數(shù)四則運算,并且可以訪問數(shù)據(jù)內(nèi)存,讀取或者寫入對應的數(shù)據(jù)。圖中有深綠、亮綠和黑色的線,深綠色意味著這條線的電壓是0V,亮綠色則為1V,黑色是因為每根黑色線都由若干根深綠或亮綠線組成,所以統(tǒng)一顯示成黑色。

這個CPU采用自己瞎編指令集(ISA),屬于精簡指令集。與復雜指令集的區(qū)別在于它精簡……之所以沒有使用別人的指令集是因為我還在學習,下一次更新會采用RISC-V的開源指令集。有人可能會覺得難道自己造指令集不好嗎?好又不好。這個問題我先挖個坑放著,有空我再講。

字長為16位寬,意味著每次可以做16位的二進制運算,也就是最大2的16次方(65536)的運算,可以尋65536的內(nèi)存地址。目前主流在32位和64位,只有少數(shù)單片機還在用16位,下次更新會更到32位。可能有人會有疑惑,如果我要計算的數(shù)字是天文數(shù)字呢?你就是64位也不夠怎么辦?首先,我們可以多做幾次運算,這個可以通過專門的計算器程序來實現(xiàn)。(求積分的軟件都有這個不算什么),其次可以使用浮點運算。但是我這個CPU沒有浮點運算單元。(滑稽臉)這個挖個坑以后講。

單周期(single cycle),每個時鐘周期只能做一次運算。難道還能做好多次嗎?能的,那就是流水線或者超標量技術甚至多核心。級數(shù)越高的流水線每個時鐘周期可以做越多次的運算。五級流水線是最經(jīng)典的流水線級數(shù),當下主流的CPU的流水線級數(shù)都在8-15之間,也有20多的超流水線。但是流水線不是越深越好,凡事都有個度。再挖個坑,以后講。

僅具備簡單加減乘除的運算功能,當然也可以寫個開方或者冪程序來支持高級運算。目前大多數(shù)的復雜運算也都是基于程序來實現(xiàn)的,直接固化在硬件電路中的也比較少見。據(jù)我所知,intel有把開平方寫在指令集和硬件電路中,這樣的好處是可以更快地求得結果,減少中途程序的調(diào)度過程。下一次更新會增加好多個運算電路,同時砍掉乘除,因為RISC-V中的RC32I不支持乘除指令,所以下次先砍掉。

該CPU一共有4個寄存器,沒有緩存。相比之下,目前的CPU有幾十到幾百個寄存器,以及數(shù)kb的緩存。這個也會在下次更新補足到32個的。

這個CPU的解碼部分也很有趣。我參考了x86的微指令設計。什么意思呢,就是正常的解碼電路都是靠硬件邏輯解碼硬解出來的,我這個不一樣,是像查字典一樣查出來的。這個字典就是圖右上部分的ROM。這樣的好處是不用設計電路了,實際電路生產(chǎn)中,如果電路設計有問題就得從頭再來,再設計再生產(chǎn)。但是如果是我這種設計方式,改改ROM里的數(shù)值就行了,無法是給個軟件升級。壞處也有,就是ROM實現(xiàn)方式占地太大,并且速度慢,功耗高。不過如果是在FPGA中大家都一樣。FPGA我就再挖個坑吧。

對了,這個CPU有個bug,就是立即數(shù)(直接在程序中給明的數(shù))不能直接參與運算,本來實現(xiàn)之初是有考慮到的,這個改也不難,但是現(xiàn)在忙著設計第二代,算了,留點遺憾才是完美。

審核編輯:劉清

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42610 -

cpu

+關注

關注

68文章

10854瀏覽量

211587 -

中央處理器

+關注

關注

1文章

124瀏覽量

16519

發(fā)布評論請先 登錄

相關推薦

ADC器件連續(xù)轉換和單次轉換的區(qū)別是什么?

單端甲類和推挽甲類功放的區(qū)別

CPU時鐘周期與主頻的關系和區(qū)別

總線時鐘周期與CPU時鐘周期的區(qū)別

CPU時鐘周期、機器周期和指令周期的關系

CPU時鐘周期的組成和作用

單CPU 雙項目開發(fā)實現(xiàn)更好的維護性和可行性應用說明

單周期CPU是什么意思呢

單周期CPU是什么意思呢

評論