這是《CPU Logisim設計》的第二個章節。我最近一直在設計流水線為基礎的RISC-V架構CPU,所以一直沒有時間更新,我們這次抽空來聊聊CPU中最基礎的邏輯門。

CPU大部分是由邏輯門構成的(話不能說太絕對),而邏輯門無外乎就是與門、或門、非門這三種。但在開始之前我們先要了解一下CPU中的數制。CPU不同于人腦,CPU采用的是二進制,也就是0和1,比如3這個十進制數等于二進制數11。那么為什么要采用二進制呢?道理很簡單卻也很復雜。簡單來講電路設計成二進制是更為方便的,因為0和1可以用電壓有無來代替,其抗干擾性強;復雜來講CPU使用二進制還涉及到布爾邏輯、歷史遺留等一系列問題。傳聞前蘇聯曾經研制出三進制的計算機,但最后因為性能不優良而被放棄了。所以其實非二進制也不是不可以。

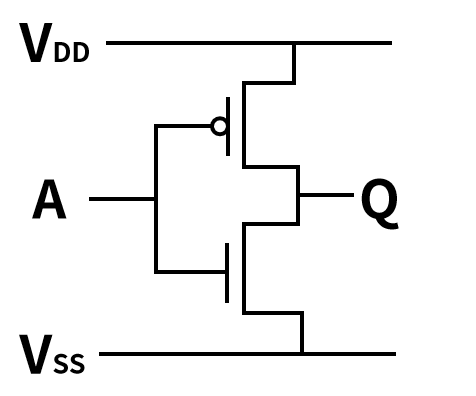

講完了數制,我們開始聊邏輯門。首先要注意一點,邏輯門是一種客觀存在的電路結構,其物理微觀實質比較復雜,我挖個坑……我們這里暫時只討論宏觀現象。

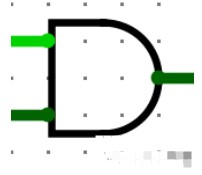

首先是與門(AND)。

左邊這兩條小短線(不一定就只有兩條,可以大于等于兩條)是輸入,右邊就是輸出了。中間那個“半圓形”的就是標準的與門了。

與門的特點是:輸入都是1時,輸出才是1。圖中亮綠色的是1,暗綠色是0,所以輸出是0,沒有問題。

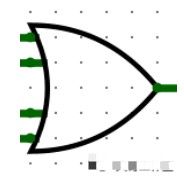

再就是或門(OR)。

或門的特點是:輸入但凡有個1,輸出就是1。我特意找了個四個輸入的或門,這四個輸入都為0,所以很不幸輸出是0。

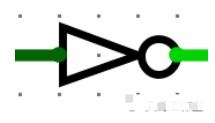

然后是非門(NOT)。

非門就更簡單了。其特點是:輸出是輸入的取反。就是說輸入是1,輸出是0;輸入是0,輸出就是1。另外,不同于以上兩種邏輯門,非門只有一個輸入。

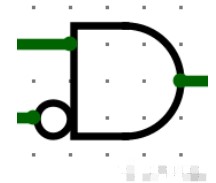

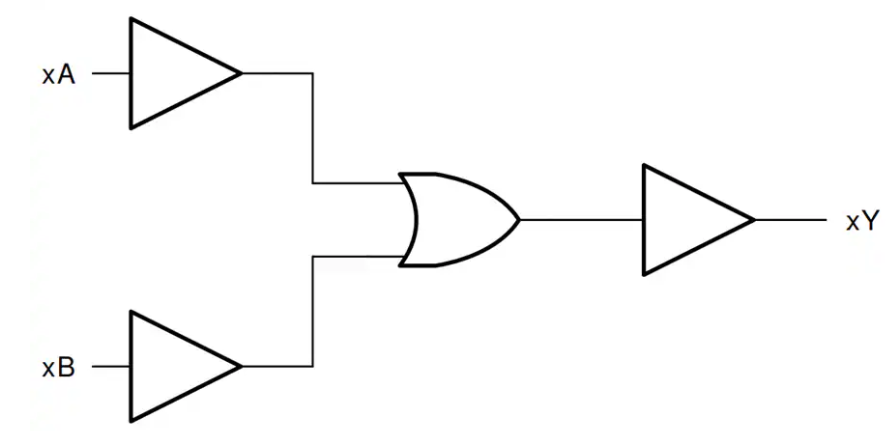

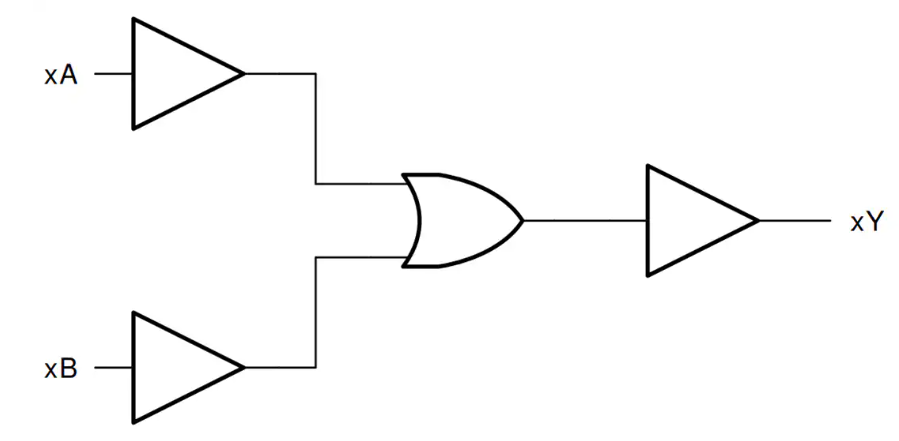

最后,給你們看一個奇怪的東西。

像不像與門長了個瘤?這個其實是與門和非門的結合體,同理還有或門和非門的結合體。其中非門被簡化成了一個圓,用于取反與門的下面一路的輸入。因為非門的邏輯實在是太簡單了卻又太容易被用到,這種畫法可以有效的節省畫板空間。

此外還有異或門(XOR)、同或門(XNOR)等門電路,它們無不是從與、或、非三種邏輯門上組合而來。這種組合而來的電路又被稱為組合邏輯電路。與之相對的概念是時序邏輯電路。

那么這些邏輯門能做什么呢?

且聽下回分解。

審核編輯:劉清

-

cpu

+關注

關注

68文章

11085瀏覽量

217243 -

邏輯門電路

+關注

關注

2文章

68瀏覽量

12269 -

RISC-V

+關注

關注

46文章

2590瀏覽量

48908

發布評論請先 登錄

高 CMR、高速邏輯門密封表面貼裝光耦合器 skyworksinc

密封表面貼裝高 CMR、高速邏輯門光耦合器 skyworksinc

高 CMR、高速邏輯門密封光耦合器 skyworksinc

Texas Instruments CD74HC32雙輸入或門數據手冊

Texas Instruments SN74HC32四路雙輸入或門數據手冊

CMOS的邏輯門如何應用在電路中

多板 PCB 組裝中最常見的邏輯錯誤

評論